Method for making gate oxide layer and gate polysilicon layer

A technology of polysilicon layer and gate oxide layer, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

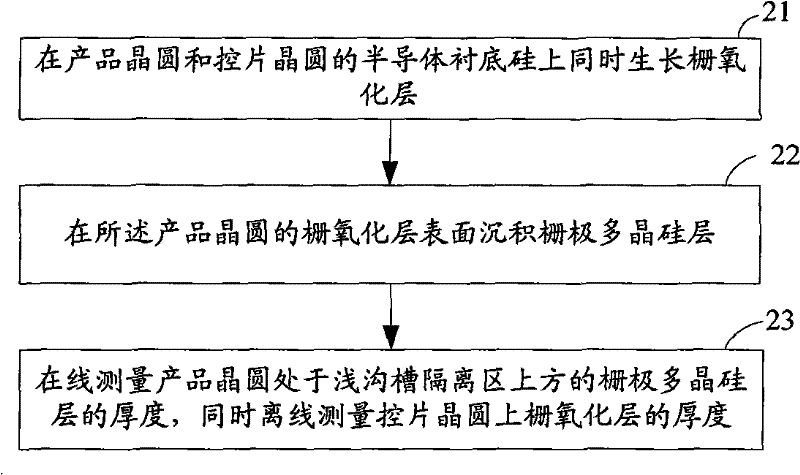

[0026] Step 21, growing a gate oxide layer on the semiconductor substrate silicon. These include simultaneous growth of a gate oxide layer on the semiconductor substrate silicon of the product wafer and the control wafer. Among them, the control wafer is a flat silicon wafer that has not been processed by a process, and is used during testing. When the thickness of the gate oxide layer needs to be measured, the control wafer is placed into the reaction chamber, and after the growth of the gate oxide layer is completed, only the control wafer with the gate oxide layer grown is output from the reaction chamber for thickness measurement;

[0027] Step 22, depositing a gate polysilicon layer on the surface of the gate oxide layer. Because only the thickness of the gate oxide layer on the control wafer needs to be measured offline, there is no need to deposit the gate polysilicon layer on the control wafer at this time, that is to say, only deposit the gate polysilicon layer on th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More