DSP simple development method based on TMS320VC55xx

A simple and modular technology, applied in the direction of program loading/starting, program control devices, etc., can solve the problems of high development cost, difficult development, long development cycle, etc., and achieve the effect of reducing development cost, saving labor cost, and easy debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

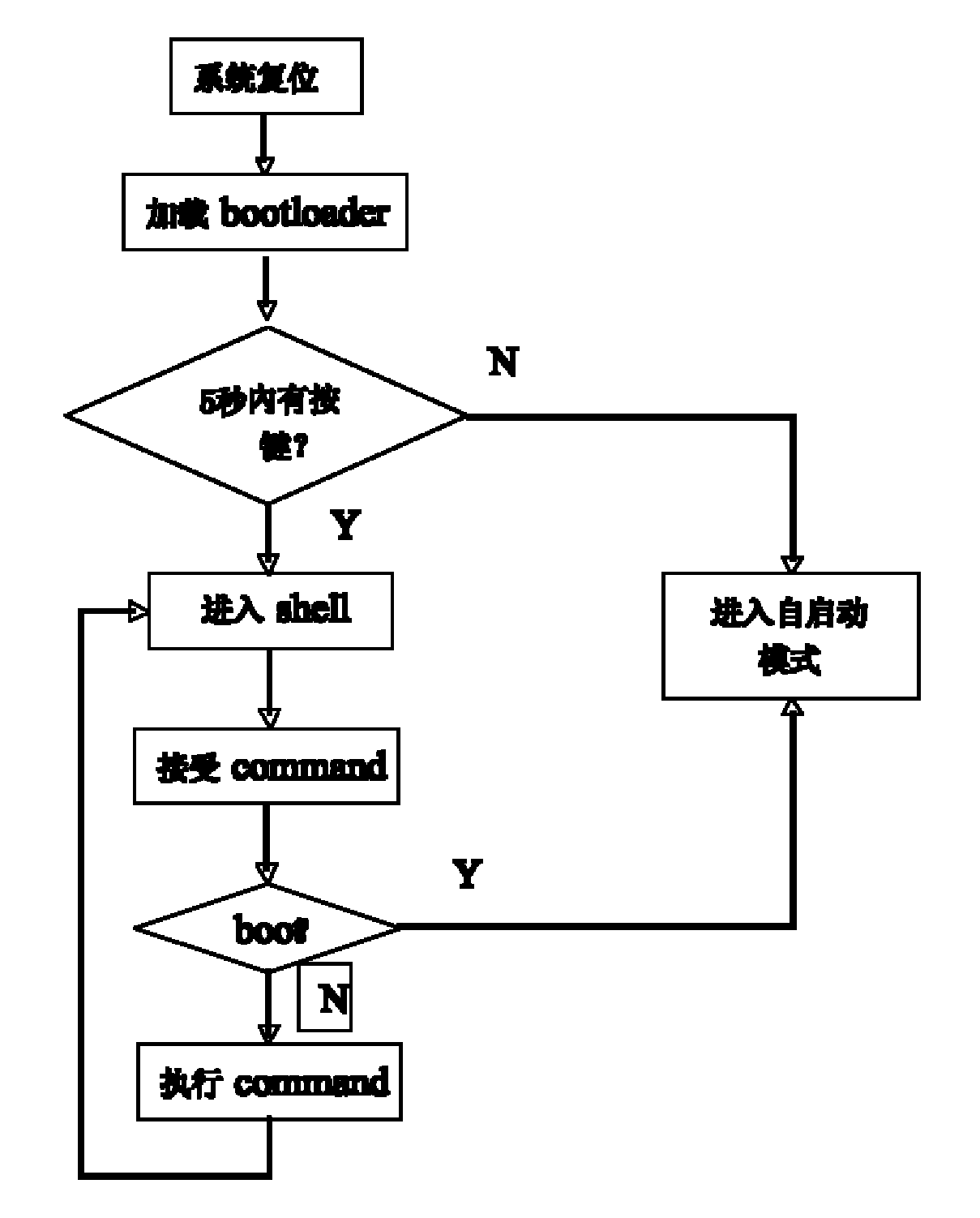

[0031] A kind of simple development method of DSP program based on TMS320VC55xx of the present invention is to finish simple debugging and update work to user program by Bootloader program, Bootloader program includes start-up loading mode and download mode, start-up loading mode completes the independent operation of program, download mode Complete the debugging and updating of the program.

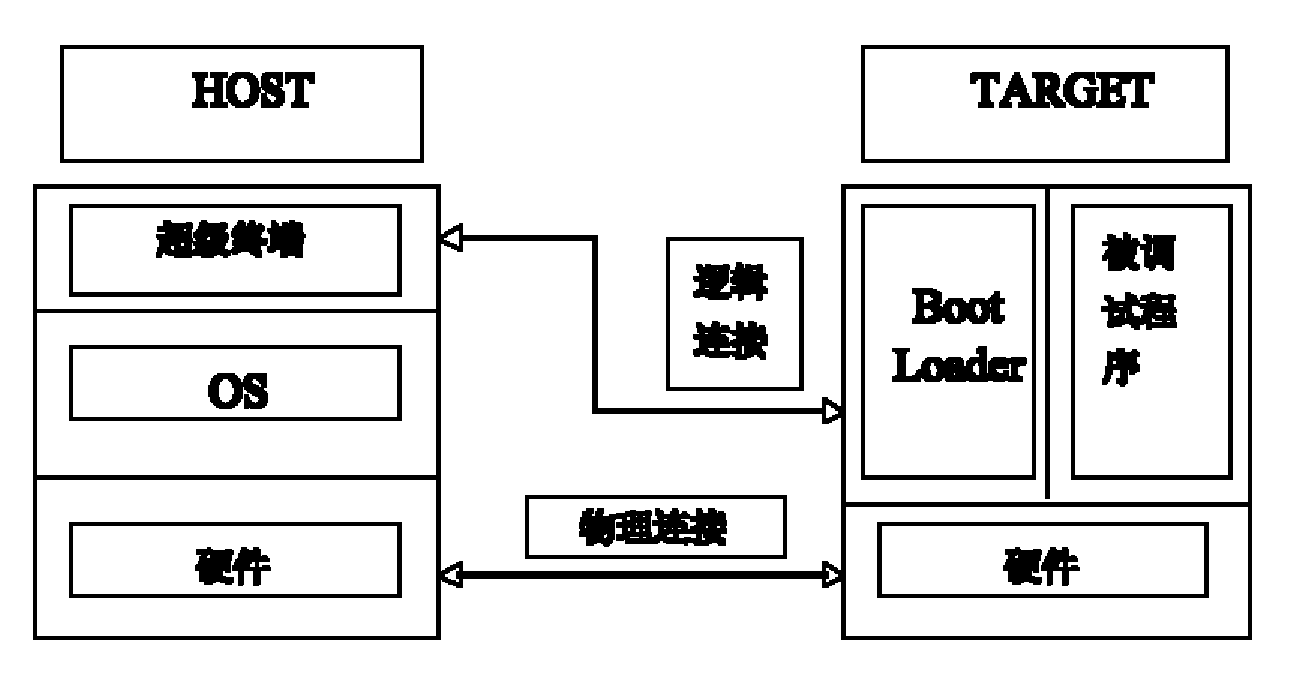

[0032] The development environment includes: a host machine and a target board. The host machine is a pc machine including operating system, integrated development environment, and terminal program; the target machine is a single board, including hardware such as DSP processor, Flash, SDRARM, FPGA, UART, buttons, indicator lights, etc., as well as bootloader and program to be debugged . The host computer communicates with the target board through the serial port.

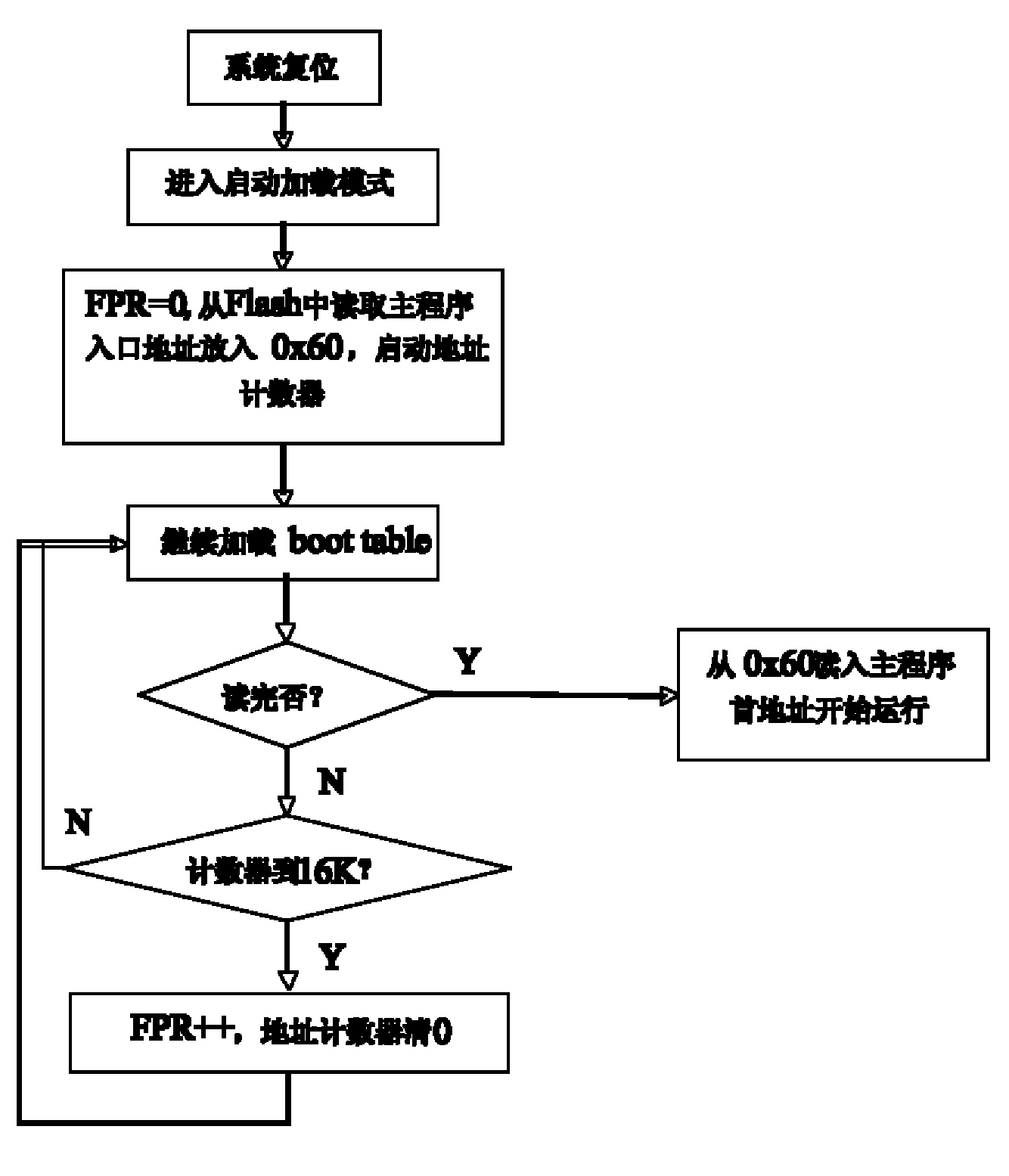

[0033] In this embodiment, the bootloader program and the debugged program will be generated according to the boottable ta...

Embodiment 2

[0059] Embodiment 2 of the present invention is as Figure 1 to Figure 3 As shown, the present invention is further described through the debugging and upgrading of an example program.

[0060] In the experiment, a 16-bit fixed-point DSP chip TMS320VC5509A from Texas Instruments is used, hereinafter referred to as 5509a. Its PGE encapsulation form has only 14 address buses (A0-A13), and the maximum addressable Flash memory of 16 KB. To address a larger address space, it is necessary to control the high address line of the Flash memory. For this reason, a Flash page change register FPR is simulated in CE2 space of DSP through CPLD. Flash adopts AM29LV320DB120 of AMD Company.

[0061] (1) Program debugging

[0062] like figure 1 As shown in the figure, it shows the block diagram of the overall software and hardware structure of the system. It can be seen from the figure that the simple debugging of the debugged program is completed through the Bootloader and the HyperTermin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com