Static discharge protection device

A technology of electrostatic discharge protection and well resistance, which is applied in the field of electrostatic discharge protection devices, can solve the problems that are not suitable for high-frequency applications and analog circuit applications, and the area occupied by electrostatic discharge protection devices is large, so as to achieve good conduction uniformity Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

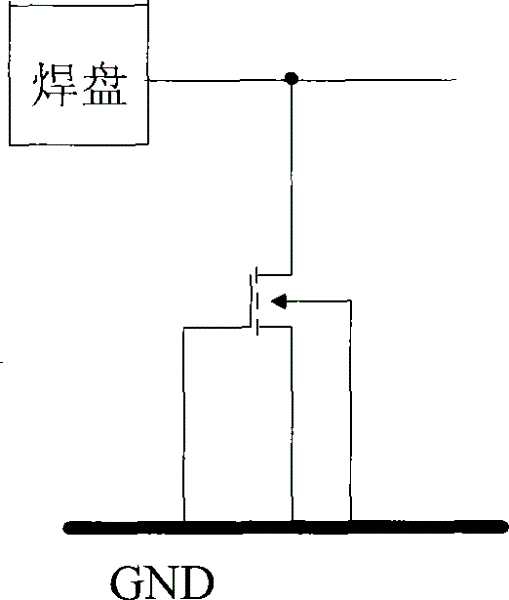

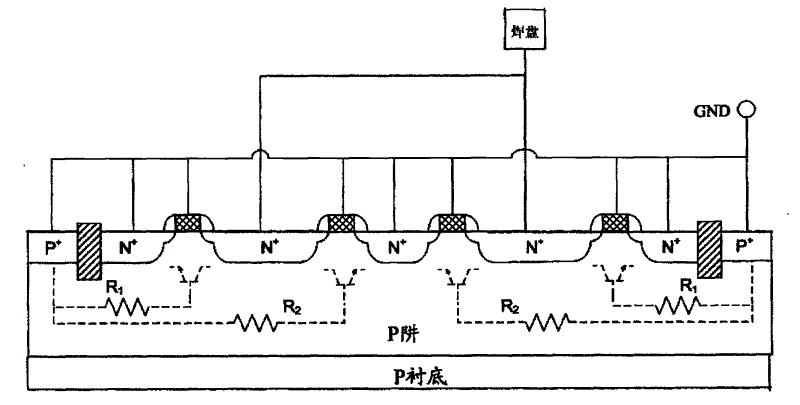

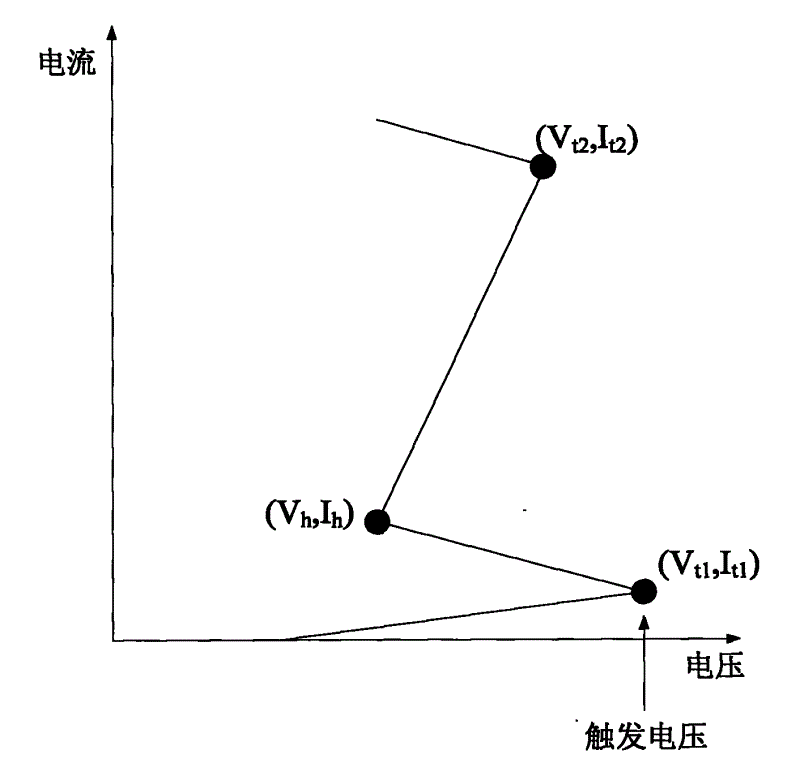

[0023] From the description of the aforementioned prior art, it can be found that for an electrostatic discharge protection device composed of multiple parallel-connected gate-grounded NMOS transistors, since the positions of each NMOS transistor are different, it will inevitably cause the base of the parasitic NPN transistor corresponding to each NMOS transistor The resistors are also different. According to the foregoing analysis, it is inevitable that the parasitic NPN transistor corresponding to the NMOS transistor whose gate is grounded in the middle position is turned on first. In view of this, if the NMOS transistor whose gate is grounded first can be used to provide an external current similar to the leakage current mentioned above to the substrate, it will help to turn on the parasitic NPN transistors corresponding to other NMOS transistors.

[0024] Based on this design concept, an embodiment of the electrostatic discharge protection device of the present invention i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More