Apparatus and method for correcting duty cycle of clock signal

一种时钟信号、内部时钟信号的技术,应用在信息存储、功率的自动控制、数字存储器信息等方向,能够解决占空比的改变没有被校正、占空比没有被校正、内部时钟信号不精确占空比等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Exemplary embodiments of the present invention will be described in more detail below with reference to the accompanying drawings. However, this invention may be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art. Throughout this disclosure, like reference numerals refer to like parts throughout the various figures and embodiments of the present invention.

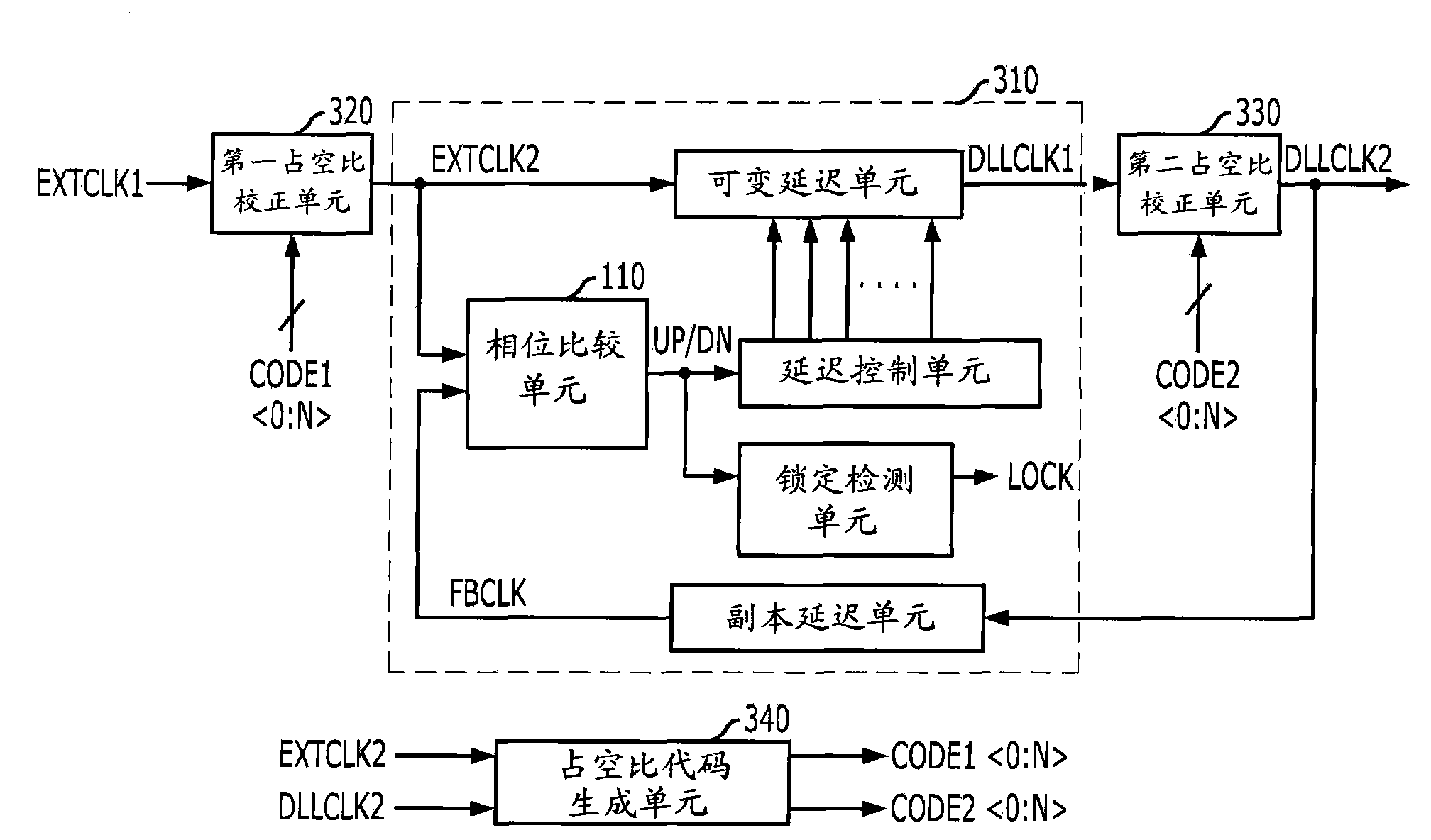

[0026] image 3 is a block diagram showing a clock correction circuit according to an embodiment of the present invention. The clock correction circuit includes a delay locked loop (DLL) 310 , first and second duty cycle correction (DCC) units 320 and 330 , and a duty code generation unit 340 . The first DCC unit 320 corrects the duty ratio of the first external clock signal EXTCLK1 in respons...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More