Method for manufacturing SOI wafer, and SOI wafer

A manufacturing method and chip technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as the inability to form a deep position of the chip, the difficulty of the thickness of the surface component area, and the inability of the BOX layer to become a dense structure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

experiment example

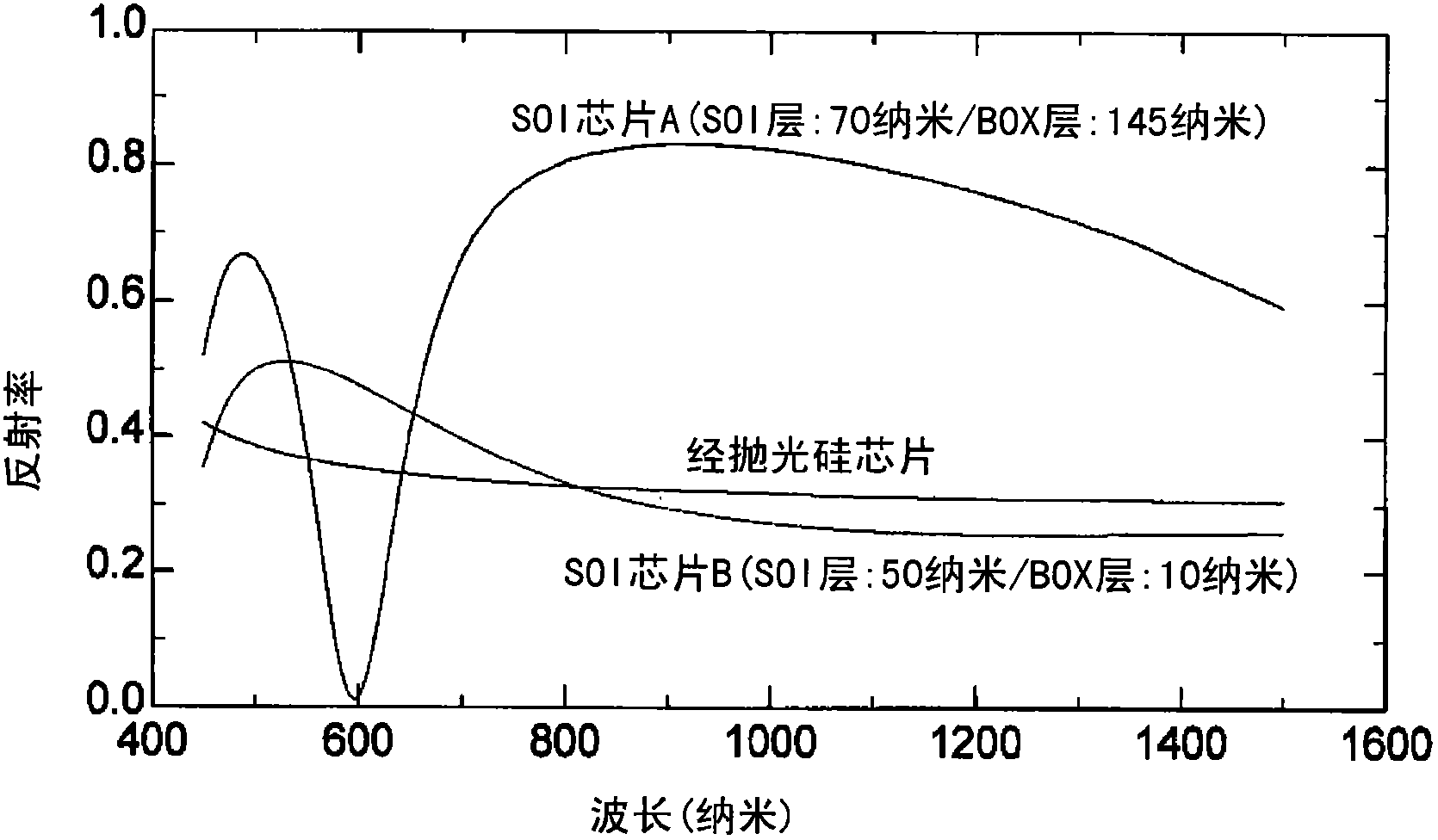

[0044] To confirm the simulation results, polished silicon chips, SOI chip A (SOI layer: 70 nm, BOX layer: 145 nm), SOI chip B (SOI layer: 50 nm, BOX layer: 10 nm) each having a diameter of 300 mm were used. ), and hydrogen (H 2 ) annealing (under an environment of 100% hydrogen gas) was performed at 1100° C. for 900 seconds using a monolithic lamp heating type epitaxial growth apparatus (Centura: manufactured by APPLIED MATERIALS). The occurrence of slip was evaluated based on a slip emphasis display image of a chip stress measurement device SIRD (Scanning Infra Red Depolarization; Scanning Infra Red Depolarization).

[0045] First, for a polished silicon chip, conditions for lamp heating power balance (chip top and bottom, chip inside and outside) conditions to achieve no slip after hydrogen annealing were obtained. The results of hydrogen annealing SOI chips A and B under this condition, as shown in Figure 7 shown. The SOI chip B, which had approximately the same reflect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More