Addressing module structure for realizing digital signal processor

A technology of addressing modules and digital signals, which is applied in the direction of electrical digital data processing, instruments, memory systems, etc., can solve the problems of increasing the complexity of address allocation, the address cannot be flexibly supported, and it is not convenient for programmers to use, so as to reduce the instruction overhead , Small circuit delay, the effect of increasing flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The embodiments of the present invention are described in detail below. This embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following implementation example.

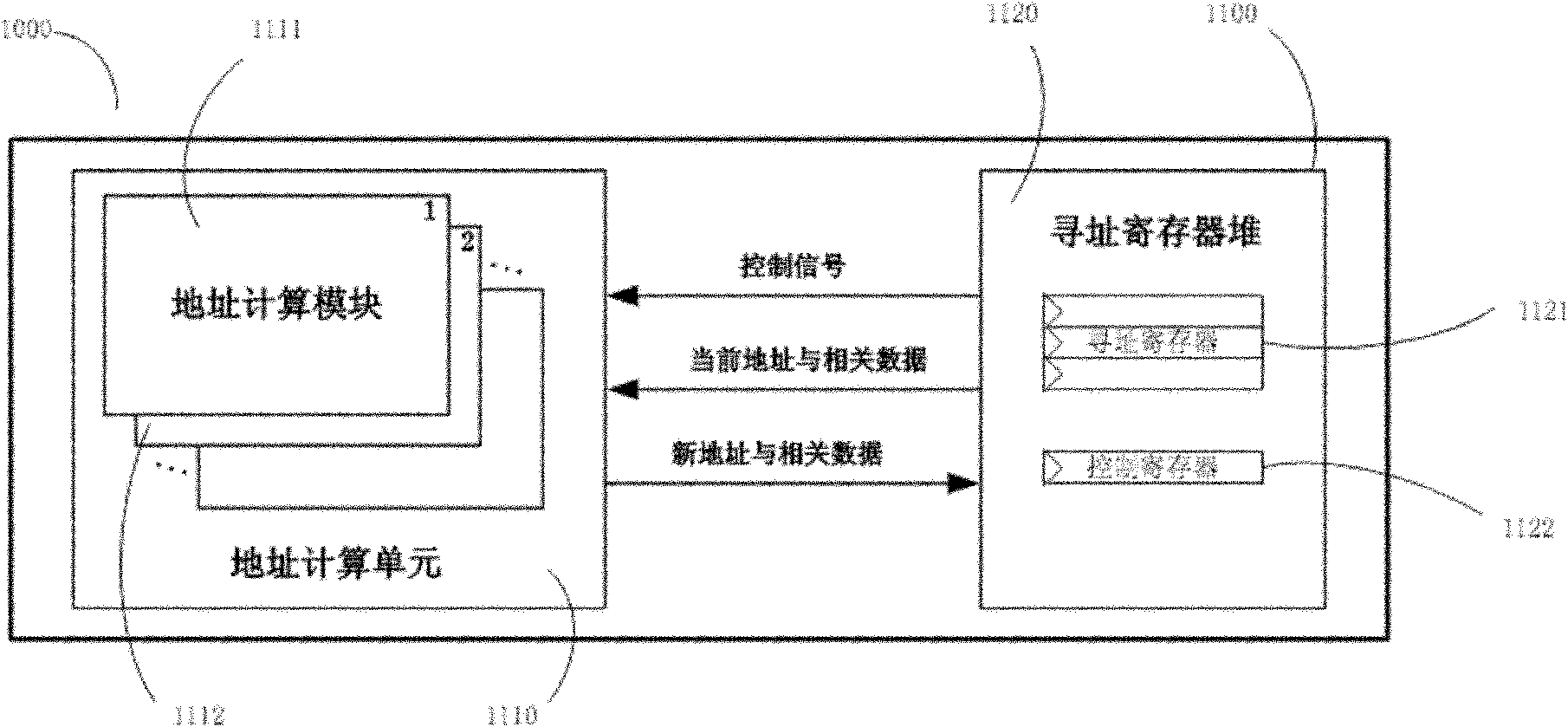

[0035] Such as image 3 As shown, this embodiment includes: an address calculation unit 1110 and an address register file 1120; wherein:

[0036] The address calculation unit 1110 includes at least one address calculation module 1111, 1112, and outputs one or more addresses used by the digital signal processor for memory access. The address calculation unit 1110 receives the control signal and the current address from the address register file 1120 , and outputs the updated address to the address register file 1120 .

[0037] The addressing register file 1120 includes an addressing register 1121 and a control reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More