Device and method for calibrating capacitor array type successive-approximation analog-to-digital converter

An analog-to-digital converter and capacitor array technology, which is applied in the calibration field of capacitor array successive approximation analog-to-digital converters, can solve problems such as complex wiring, considerable number of virtual redundant capacitors, and limited matching accuracy of capacitors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

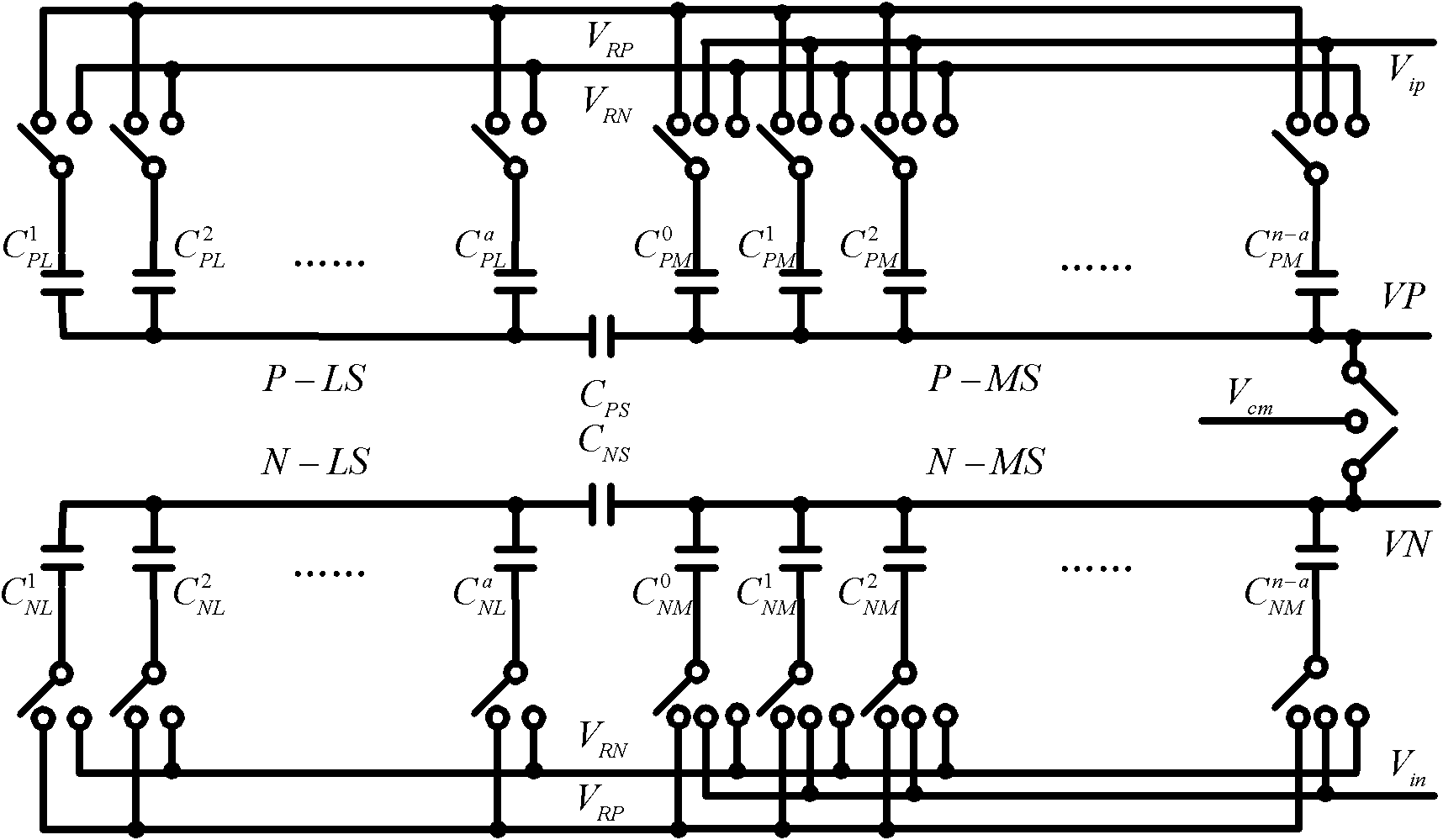

[0021] The present invention proposes a calibrating device and method thereof for a capacitor array type successive approximation analog-to-digital converter, combined below Image 6 and Figure 7 Describe the working process of the device in detail.

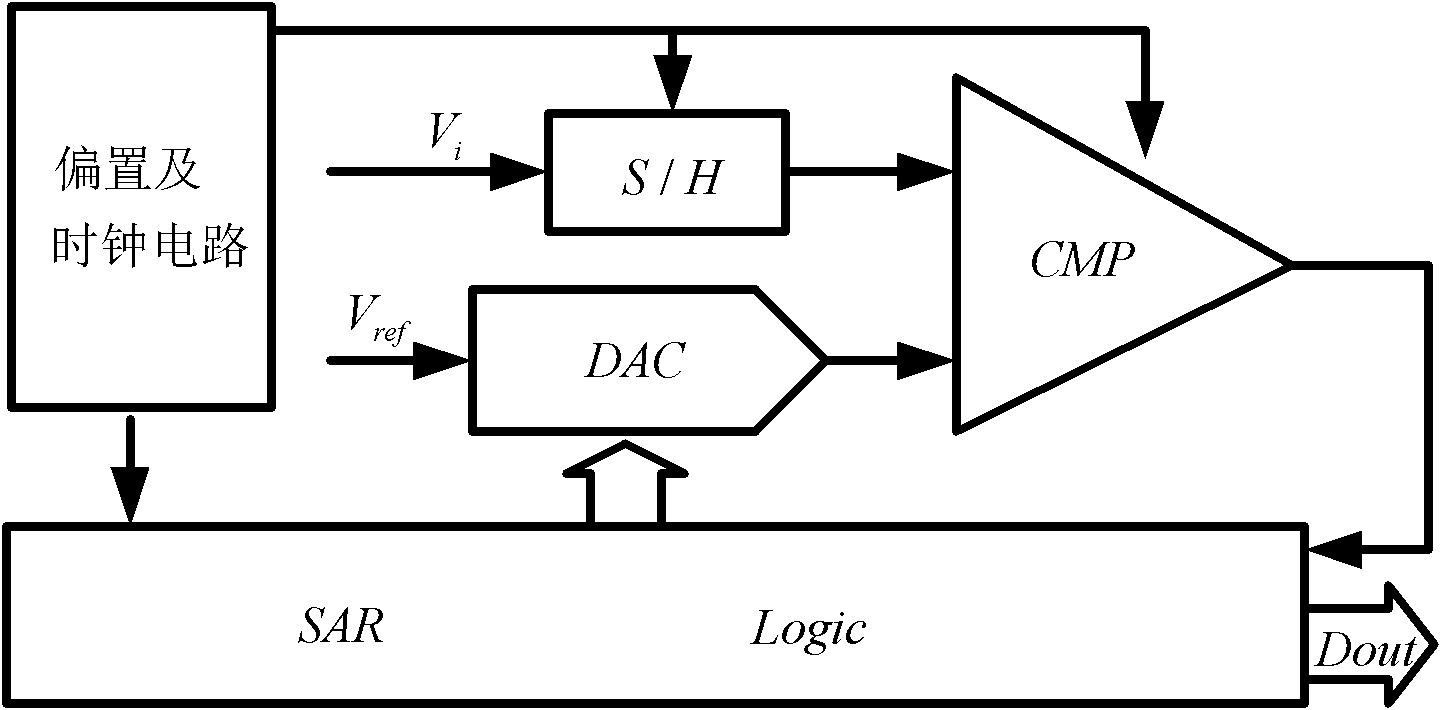

[0022] The calibrating device of a kind of capacitor array type successive approximation analog-to-digital converter that the present invention proposes (see Image 6The part marked with a dotted line box) includes a capacitance measurement circuit C-M, a static memory SRAM and a corresponding control circuit; on this basis, a logical operation unit ALU connected between the capacitance measurement circuit and the static memory is added; Image 6 Outside the dotted line box is shown the capacitor array successive approximation analog to digital converter to be calibrated which is composed of capacitor array digital to analog converter, bias clock circuit, comparator CMP and successive approximation logic SAR-Logic.

[0023] Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More