Multi-core adaptive way prediction algorithm based on Cache division

A way prediction and self-adaptive technology, applied in the field of self-adaptive way prediction algorithm based on Cache division under multi-core, can solve the problem of reducing the dynamic energy consumption of Cache, so as to reduce Cache power consumption, reduce Cache access power consumption, and reduce Cache way number effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036]Taking an on-chip multi-core processor with a two-level Cache structure as an example, the adaptive path prediction algorithm of the present invention will be described in detail below.

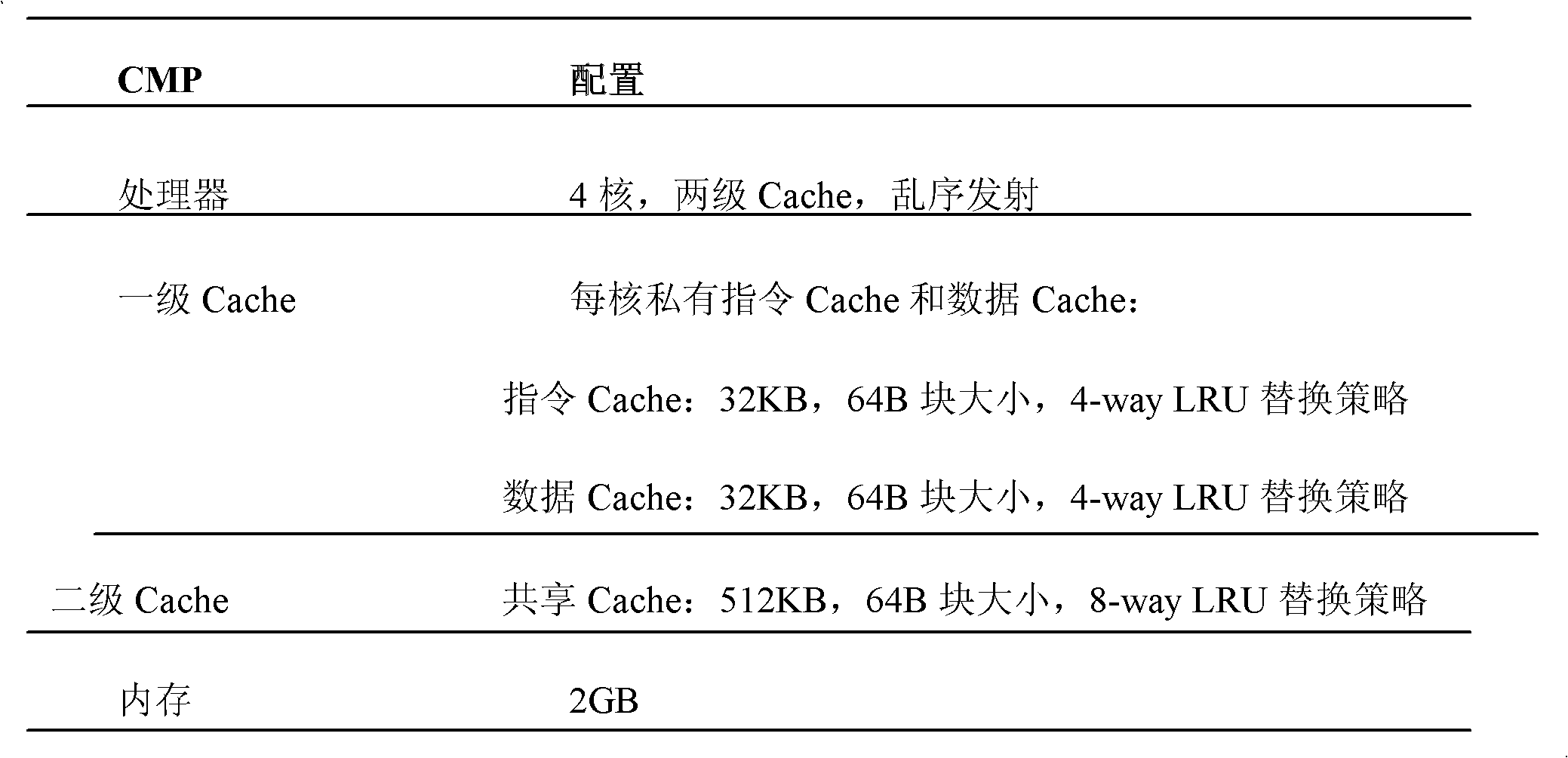

[0037] The configuration is shown in Table 1:

[0038]

[0039] Table 1

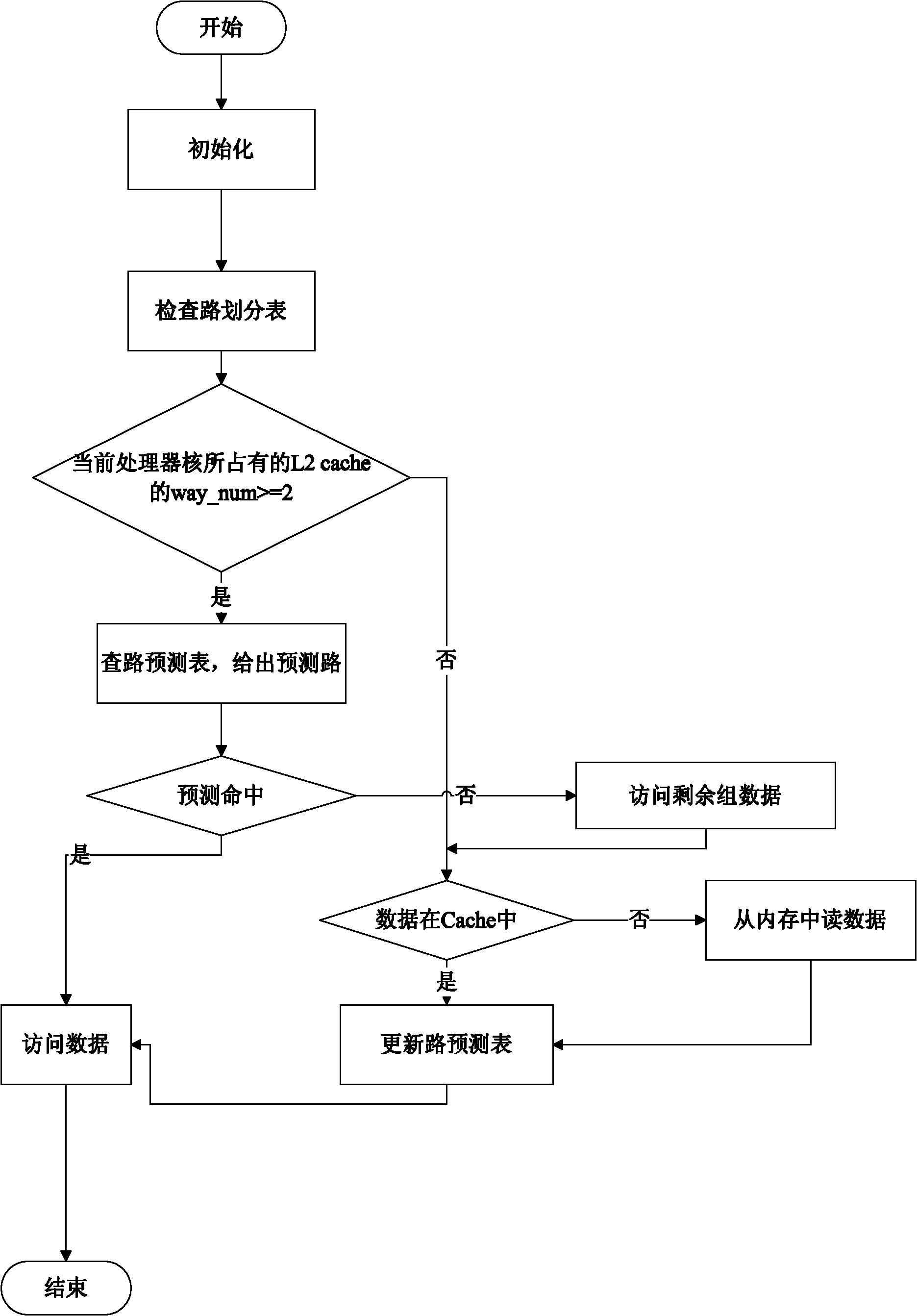

[0040] The specific algorithm flow:

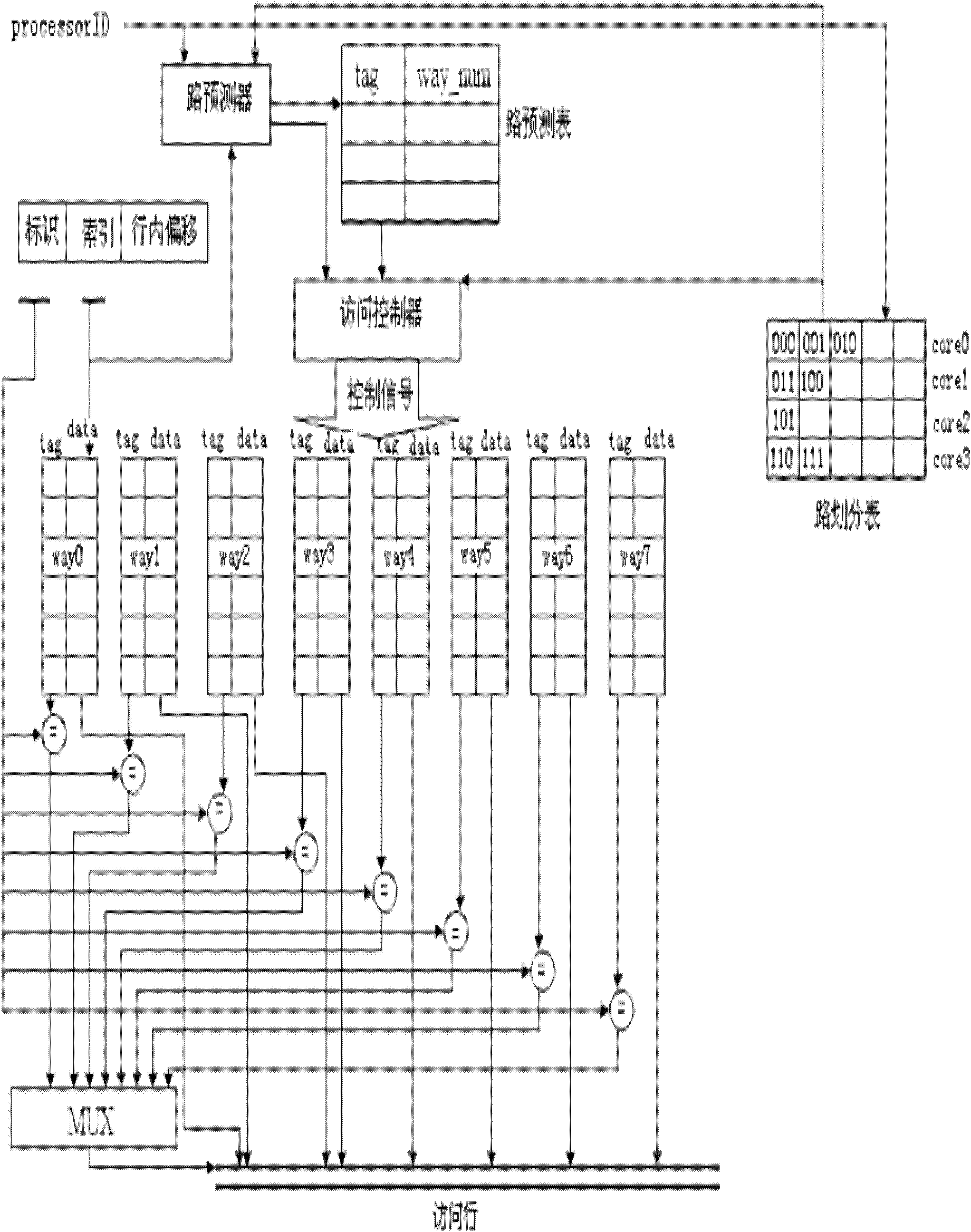

[0041] (1) Initialize the way division table and the way prediction table: the L2Cache division algorithm used is the LRU replacement algorithm, and the result of L2Cache division is stored in the way division table. The size of the way partition table row is determined by the number of processor cores contained in the multi-core processor, such as figure 1 As shown, the way division table has 4 rows and 5 columns, each row corresponds to a processor core, and each column stores the number of the way in the L2Cache occupied by the processor core. figure 1 The processor core0 is divided into three L2Cache ways numbered 000, 001, and 010; taking the multi-core processor in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More