Clock multiplying circuit, solid-state imaging device, and phase-shift circuit

A clock frequency multiplication and circuit technology, applied in TV, color TV, electrical components, etc., can solve problems such as output data error, reduction of setup/hold margin, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

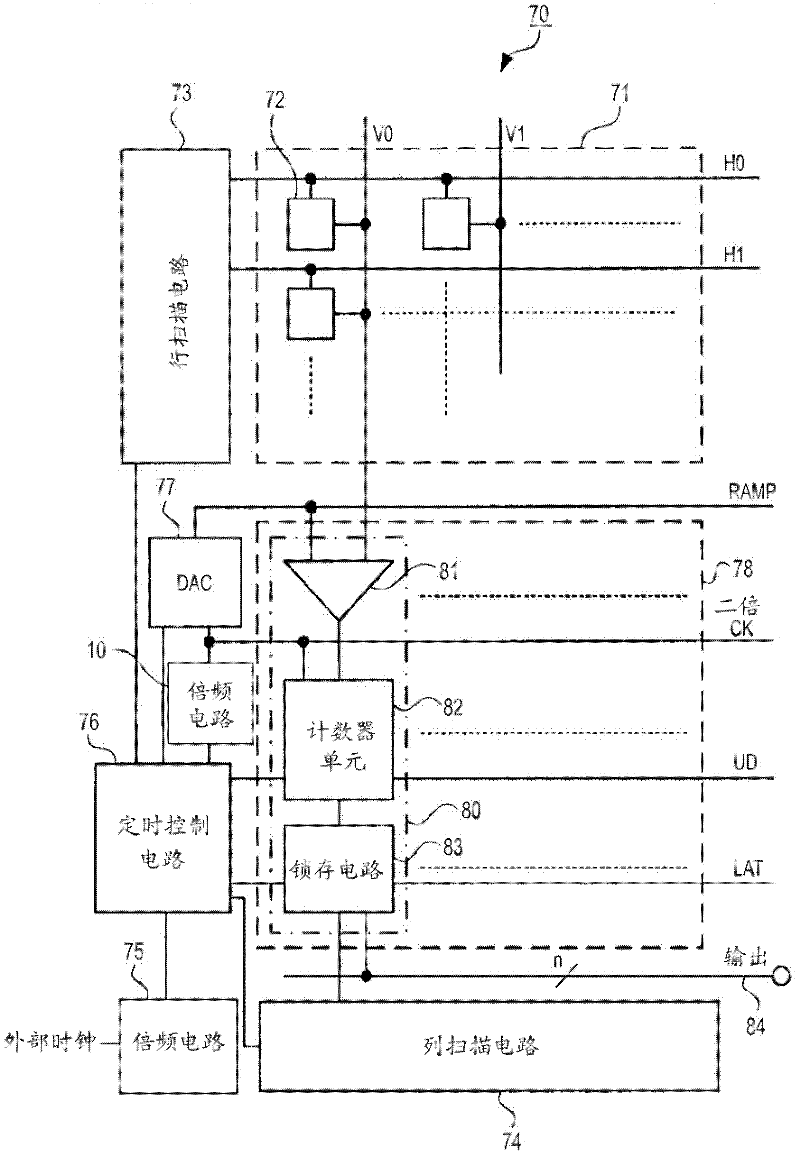

[0038] An example of a frequency doubling circuit, a phase shifting circuit, and a solid-state imaging device including the frequency doubling circuit according to an embodiment of the present invention is explained in the following order with reference to the drawings. The present invention is not limited to the examples explained below.

[0039] 1. Configuration example of frequency multiplication circuit

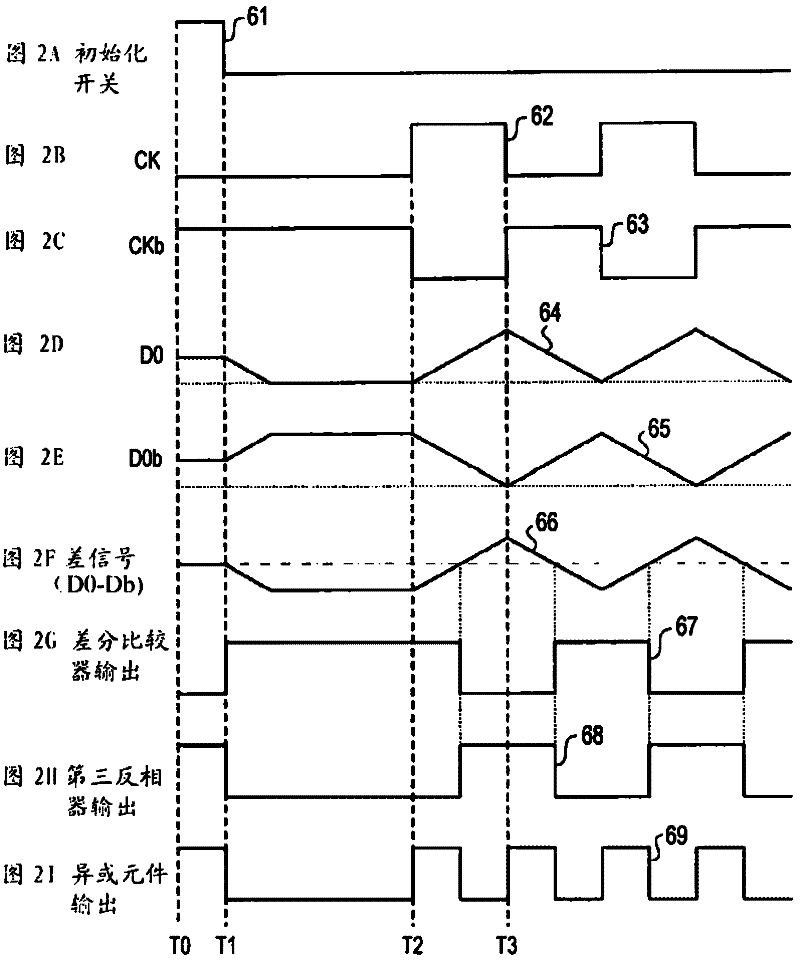

[0040] 2. Operation example of frequency multiplication circuit

[0041] 3. Configuration example of solid-state imaging device

[0042]

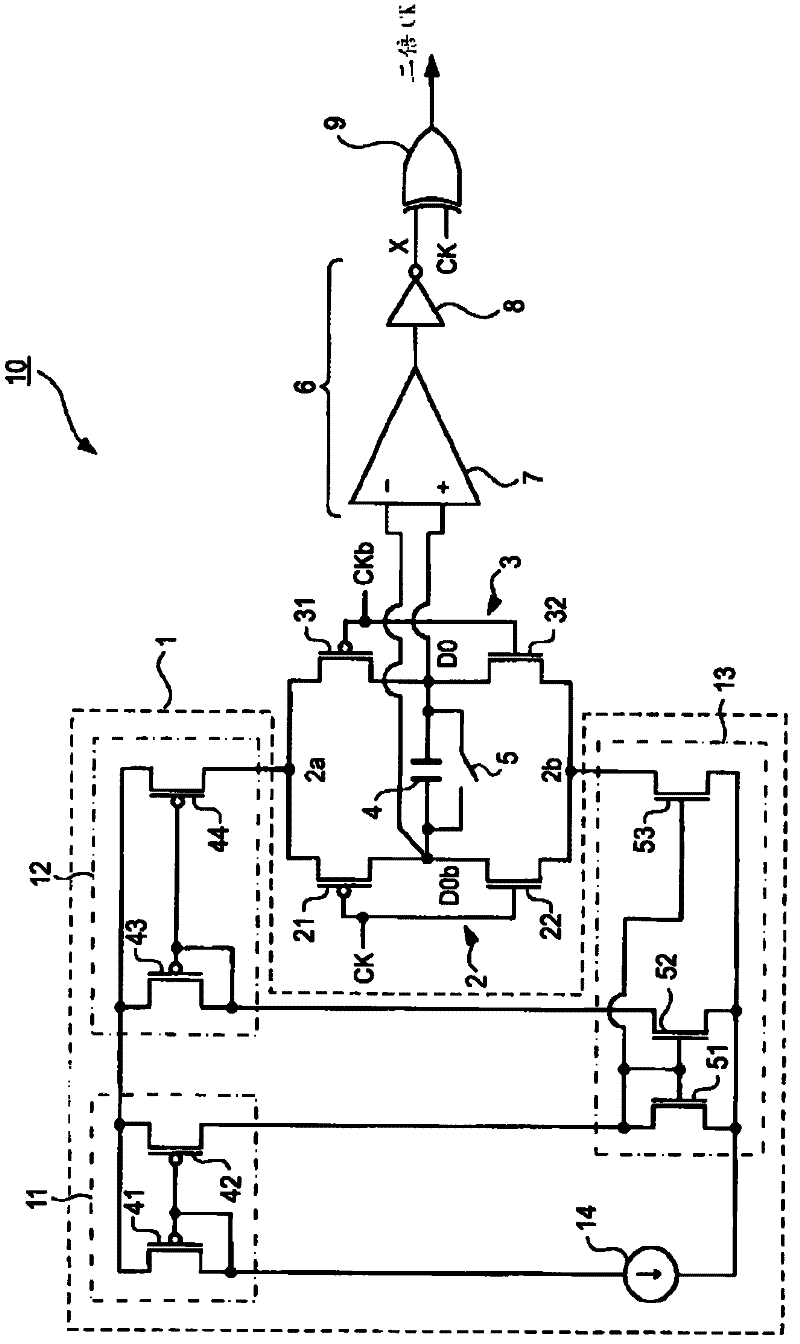

[0043] figure 1 A schematic configuration of a frequency doubling circuit according to an embodiment of the present invention is shown. Frequency multiplication circuit 10 (clock frequency multiplication circuit) includes current supply unit 1, first inverter 2, second inverter 3, capacitive element 4, initialization switch 5 (initialization switching element), differential detector 6, EXOR (Exclusive OR) element 9 (multiplier s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More