Dual-damascene structure and manufacturing method thereof

A dual damascene structure and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of dielectric constant change, low density, and low dielectric constant dielectric layer damage, etc., to prevent Effects of adverse effects, stable dielectric constant value, and improved reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

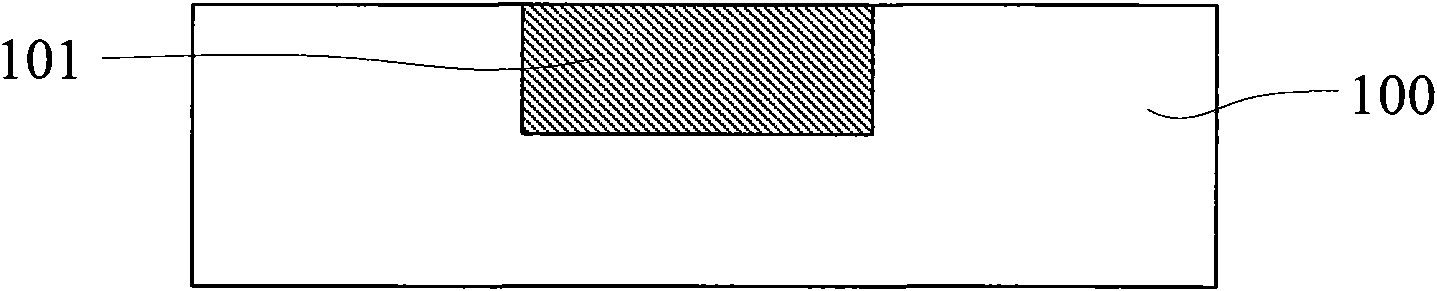

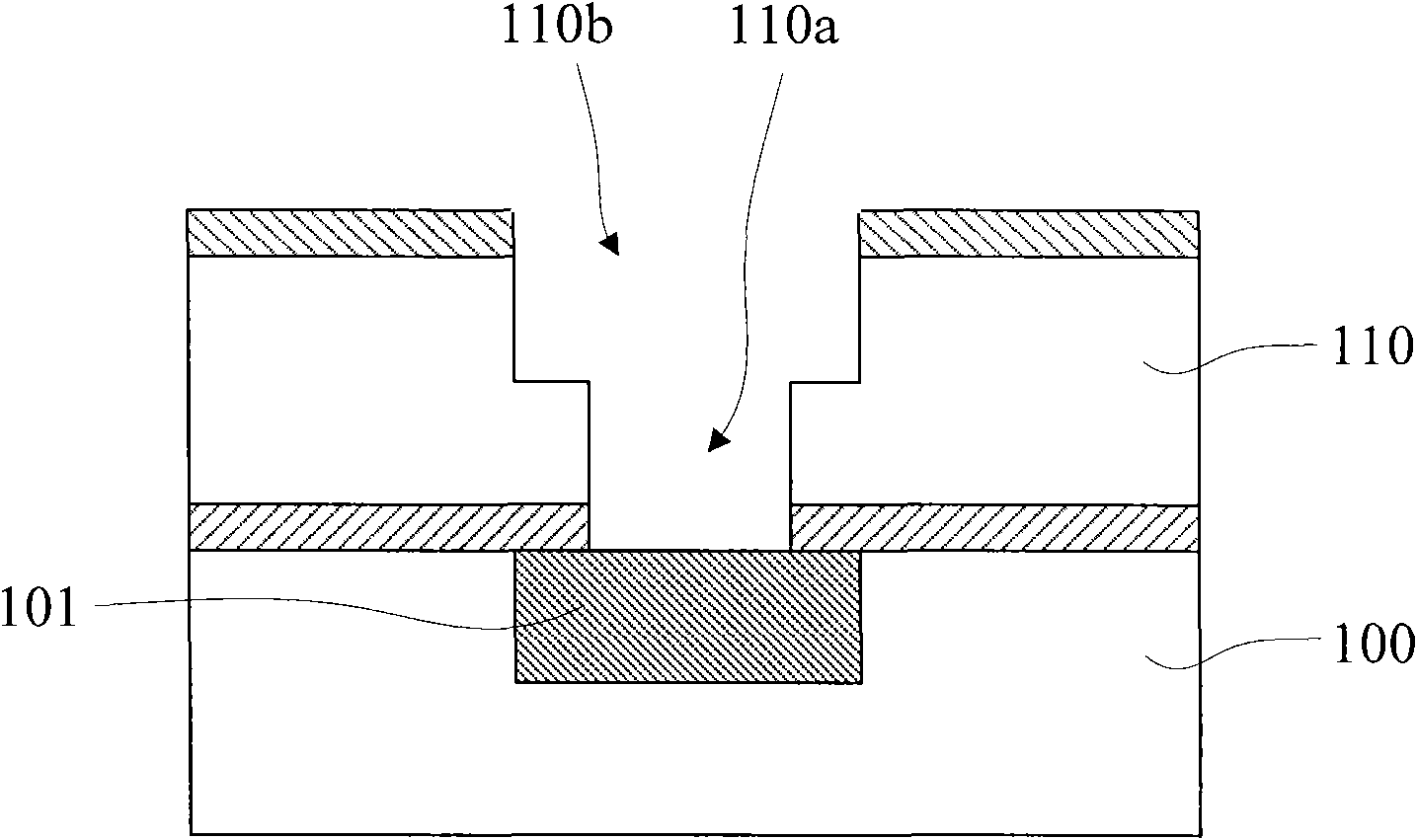

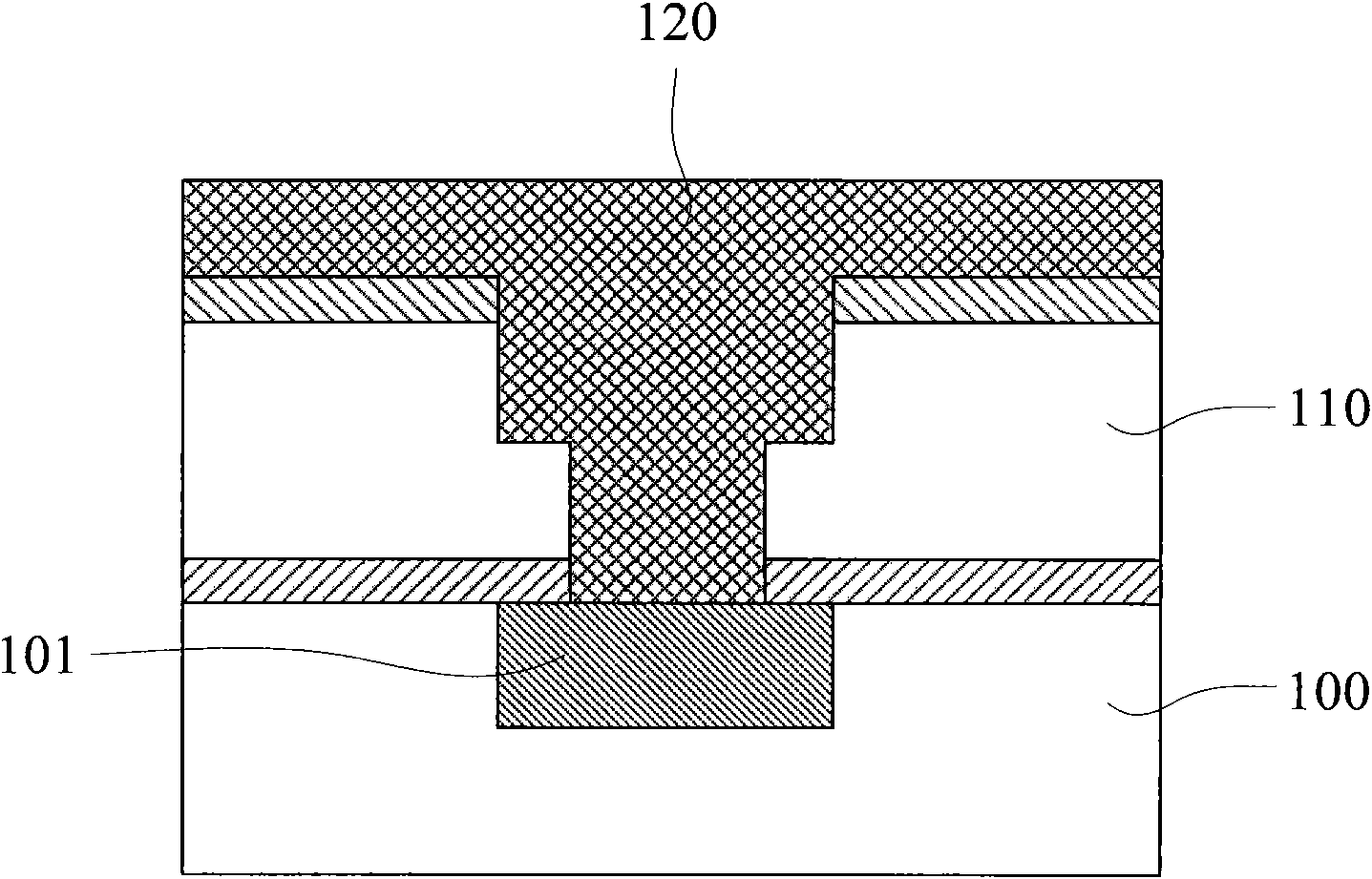

[0030] According to the background technology, when the chemical mechanical polishing process is used to remove the metal material on the low dielectric constant dielectric layer, a part of the thickness of the low dielectric constant dielectric layer will be damaged, resulting in the dielectric constant of the low dielectric constant dielectric layer Changes that affect the reliability of semiconductor devices. Therefore, the present invention provides a dual damascene structure and a manufacturing method thereof. In the manufacturing method of the dual damascene structure, after removing the metal material on the first low dielectric constant dielectric layer, the damaged first dielectric layer is removed, and the remaining A second low dielectric constant dielectric layer is formed on the first low dielectric constant dielectric layer to ensure that the dielectric constant value of the dielectric layer of the finally formed dual damascene structure is stable, and the first d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More