Programmable exception processing latency

A technology of waiting time and exception handling, which is applied in the fields of electrical digital data processing, climate sustainability, instruments, etc., and can solve problems such as user restrictions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

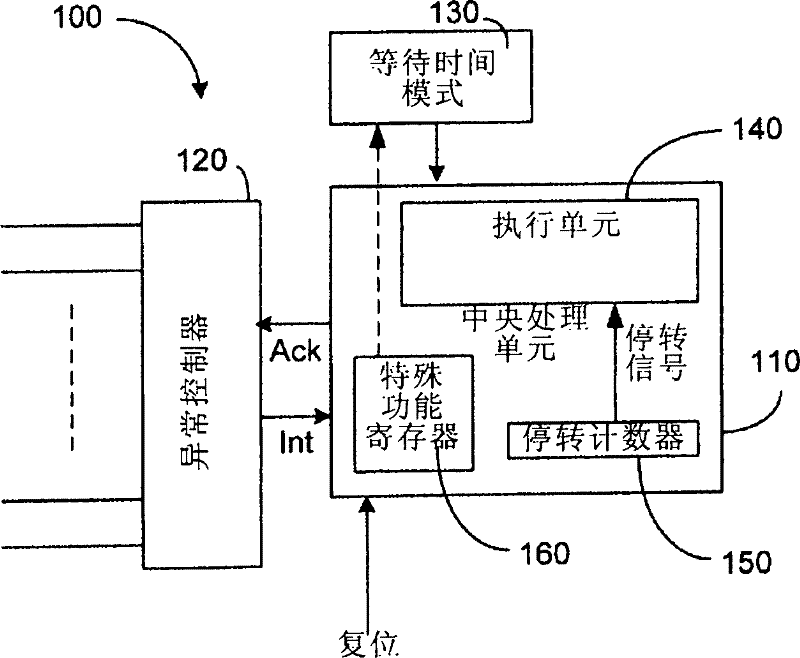

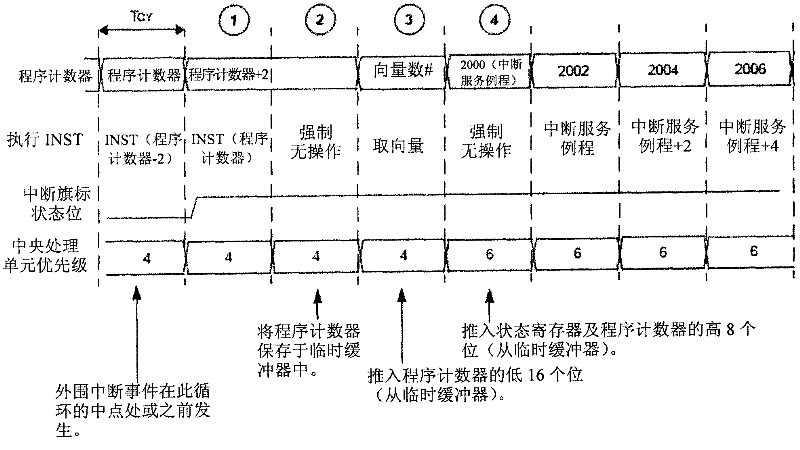

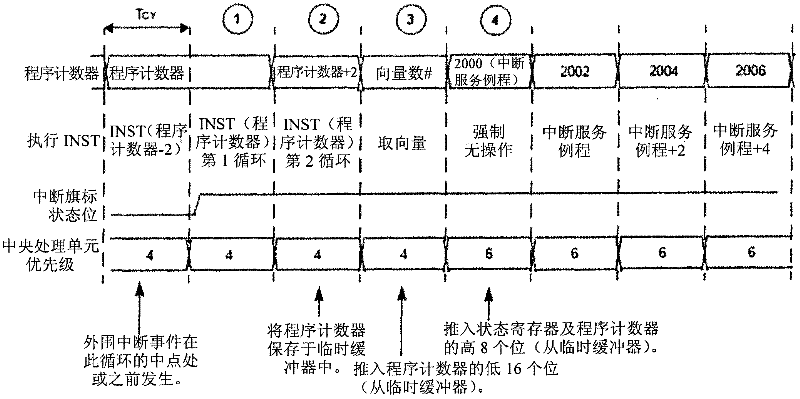

Embodiment Construction

[0020] According to the teachings of the present invention, it is possible to design a processor that operates in at least two modes, where the first mode provides a fixed latency, where all exceptions have the same latency. A second mode may be set in which the processor has a variable latency depending on the pending instruction during which the exception occurred. An exception may be any type of external or internal interrupt or trap caused within a processing unit. A pending instruction is understood to be an instruction that must be executed before an exception can be handled. In many processor architectures, this instruction is the instruction executed in the loop following the loop during which the exception occurred. However, depending on the embodiment, it could also be an instruction that was pending when the interrupt occurred. A control register may be used that provides, for example, a bit to select the first or second mode. However, other means to signal a par...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More