N-type silicon-on-insulator transverse double-diffusion field effect transistor

A technology of field effect transistors and lateral double diffusion, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as easy deviation, increased self-heating effect of devices, and limited voltage of buried oxide layer, so as to improve reliability and impact ionization rate The effect of reducing and improving the output characteristic curve

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

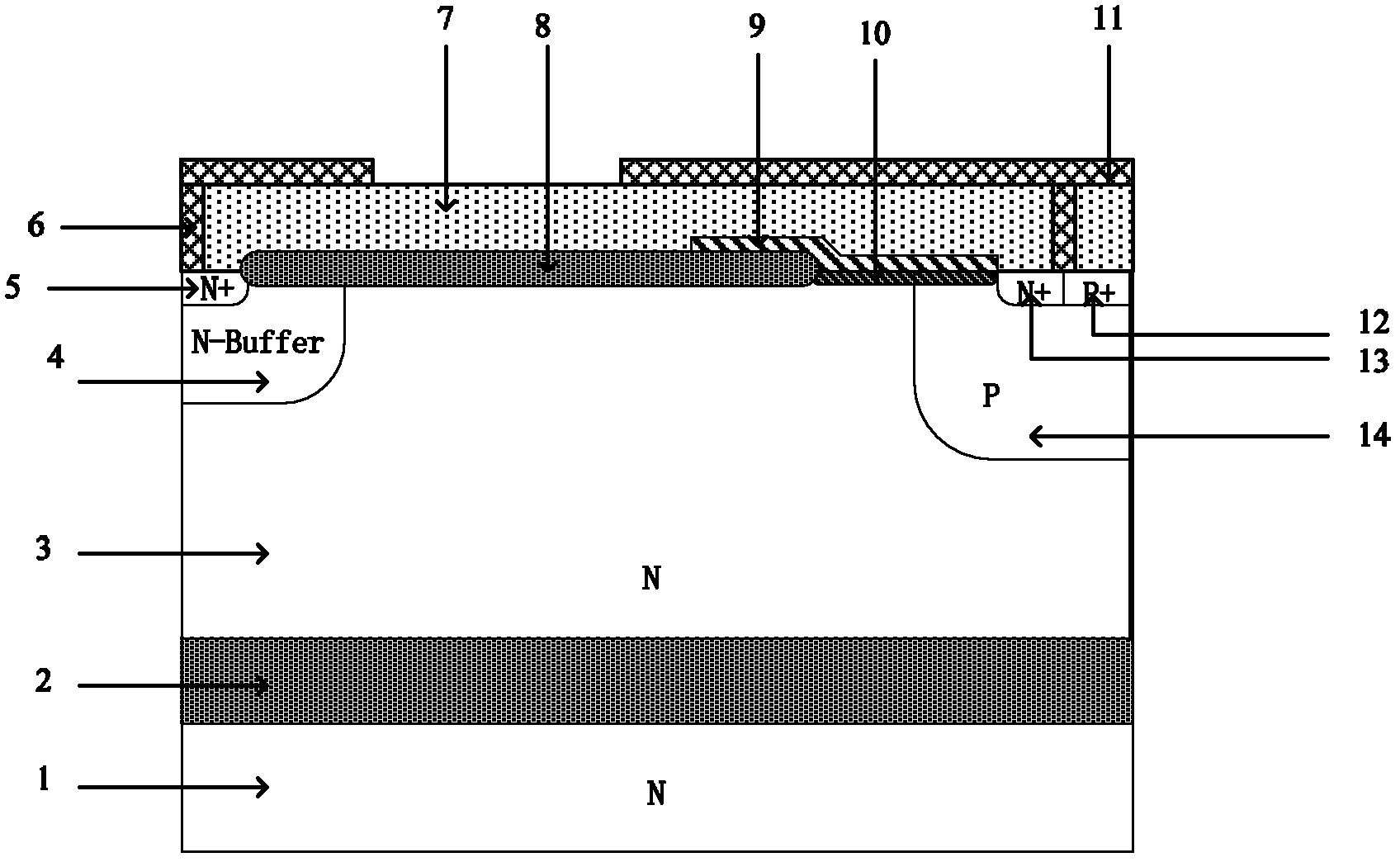

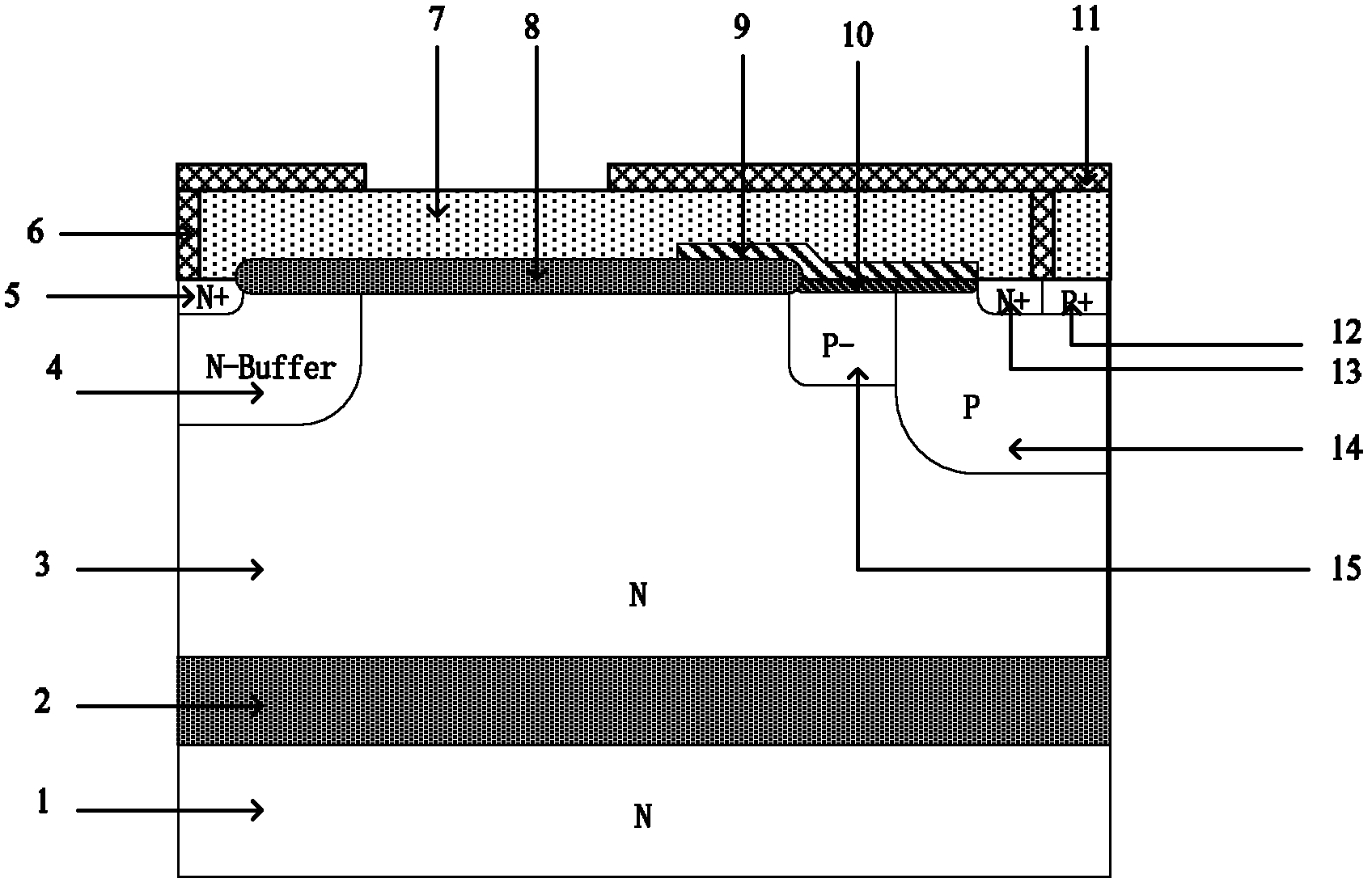

[0021] Attached below figure 2 , the present invention is described in detail, an N-type silicon-on-insulator lateral double-diffused field effect transistor, comprising: an N-type substrate 1, a buried oxygen 2 is arranged on the N-type substrate 1, and a N-type substrate is arranged on the buried oxygen 2. Type epitaxial layer 3 is provided with N-type buffer well 4 and P-type body region 14 in the inside of N-type epitaxial layer 3, is provided with N-type positive region 5 in N-type buffer well 4, is provided with in P-type body region 14 N-type negative region 13 and P-type body contact region 12 are arranged, gate oxide layer 10 and field oxide layer 8 are arranged on the surface of N-type epitaxial layer 3 and one end of gate oxide layer 10 and one end of field oxide layer 8 are offset, so The other end of the gate oxide layer 10 extends toward the N-type cathode region 13 and ends at the N-type cathode region 13, and the other end of the field oxide layer 8 extends tow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More