Data error check method, data transfer method, and semiconductor memory

A technology of error checking and storage devices, applied in the direction of error detection/correction, static memory, electrical digital data processing, etc., can solve the problems of six-level gate delay, increase of circuit area and error checking time, increase of circuit area, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Reference will now be made in detail to exemplary embodiments according to the present invention and examples illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts.

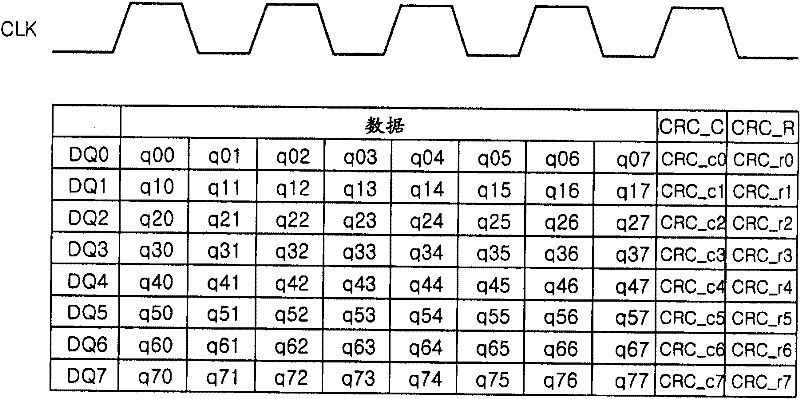

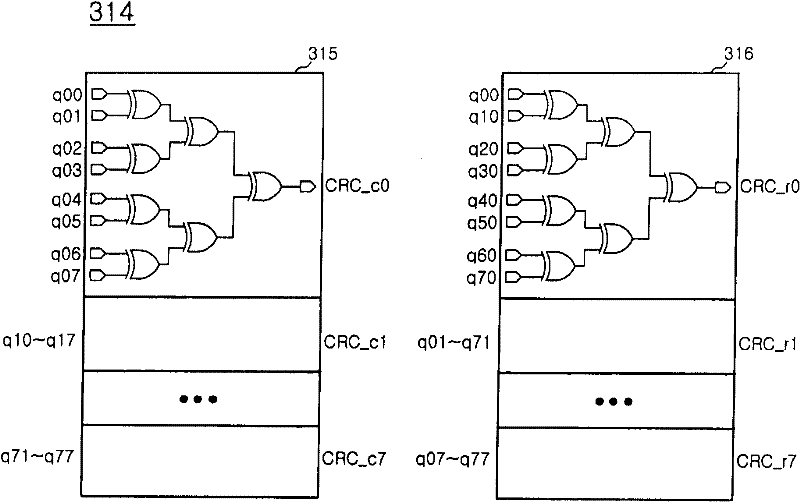

[0025] According to an exemplary embodiment, the first error check in the column direction and the second error check in the row direction are performed on the data transferred through the data input / output terminals DQ0 to DQ7 to generate corresponding error check signals, and are transmitted via the data bus Send the error check signal to the outside.

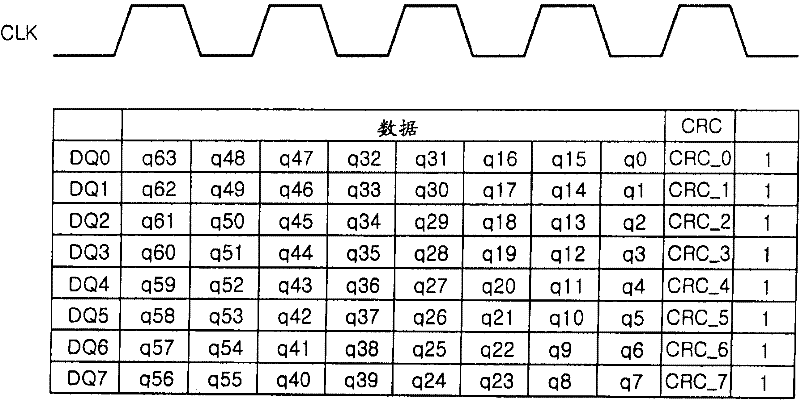

[0026] Typically, a unit time interval is allocated for error checking signals. That is, if figure 1 As shown, five clock signals CLK are used in order to transmit 8-bit data and 1-bit error check signal. Therefore, since two unit time intervals are allocated to one clock signal, the tenth unit time interval is redundant in typical practice.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com