Method for designing System on a Chip (SOC) chips with low power consumption for wireless local area network

A technology of wireless local area network and design method, which is applied in the direction of wireless communication, network topology, energy consumption reduction, etc., and can solve problems such as application obstacles, large chip work and standby power consumption, and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

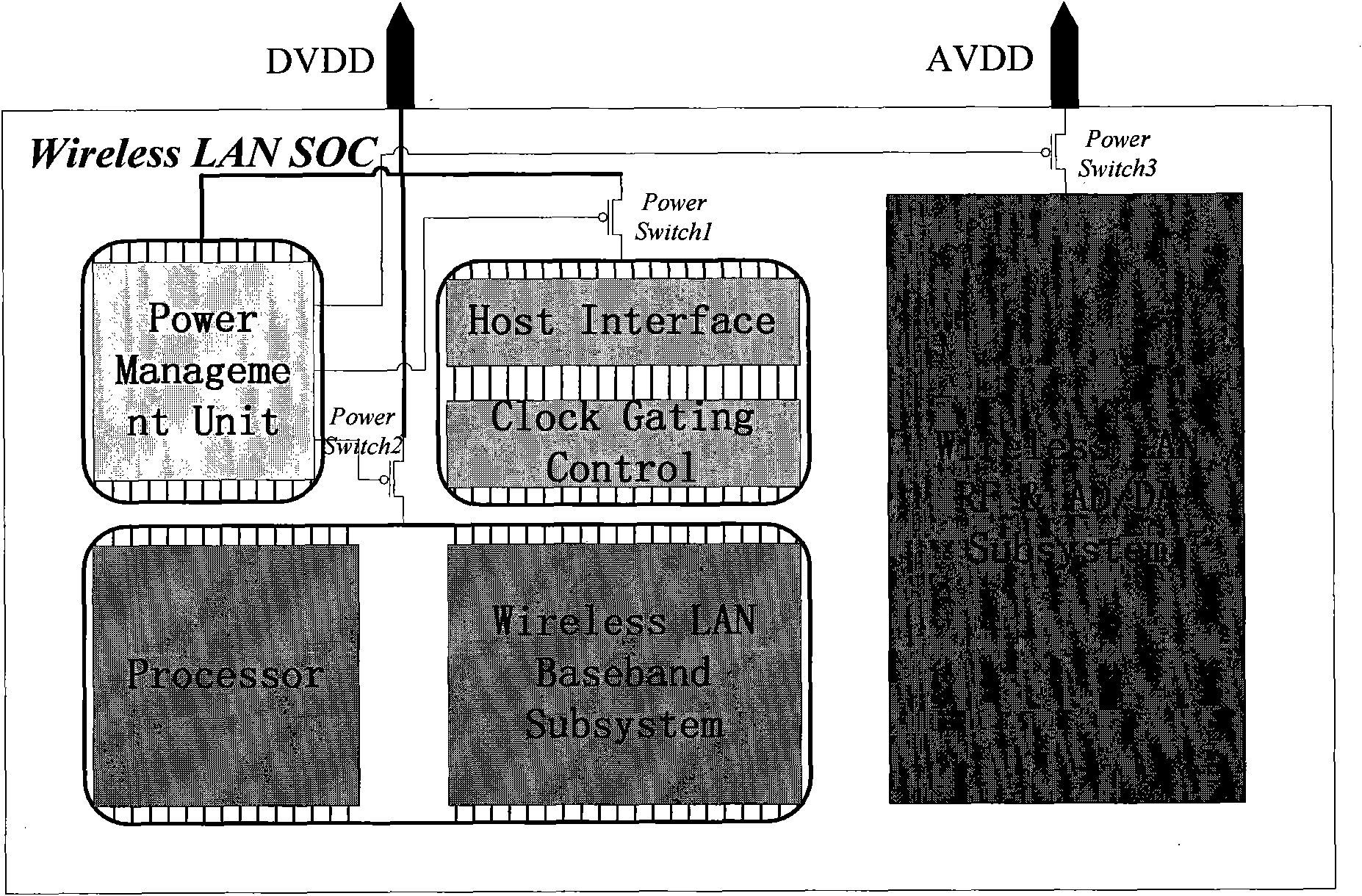

[0014] Introduction to each functional module of the chip

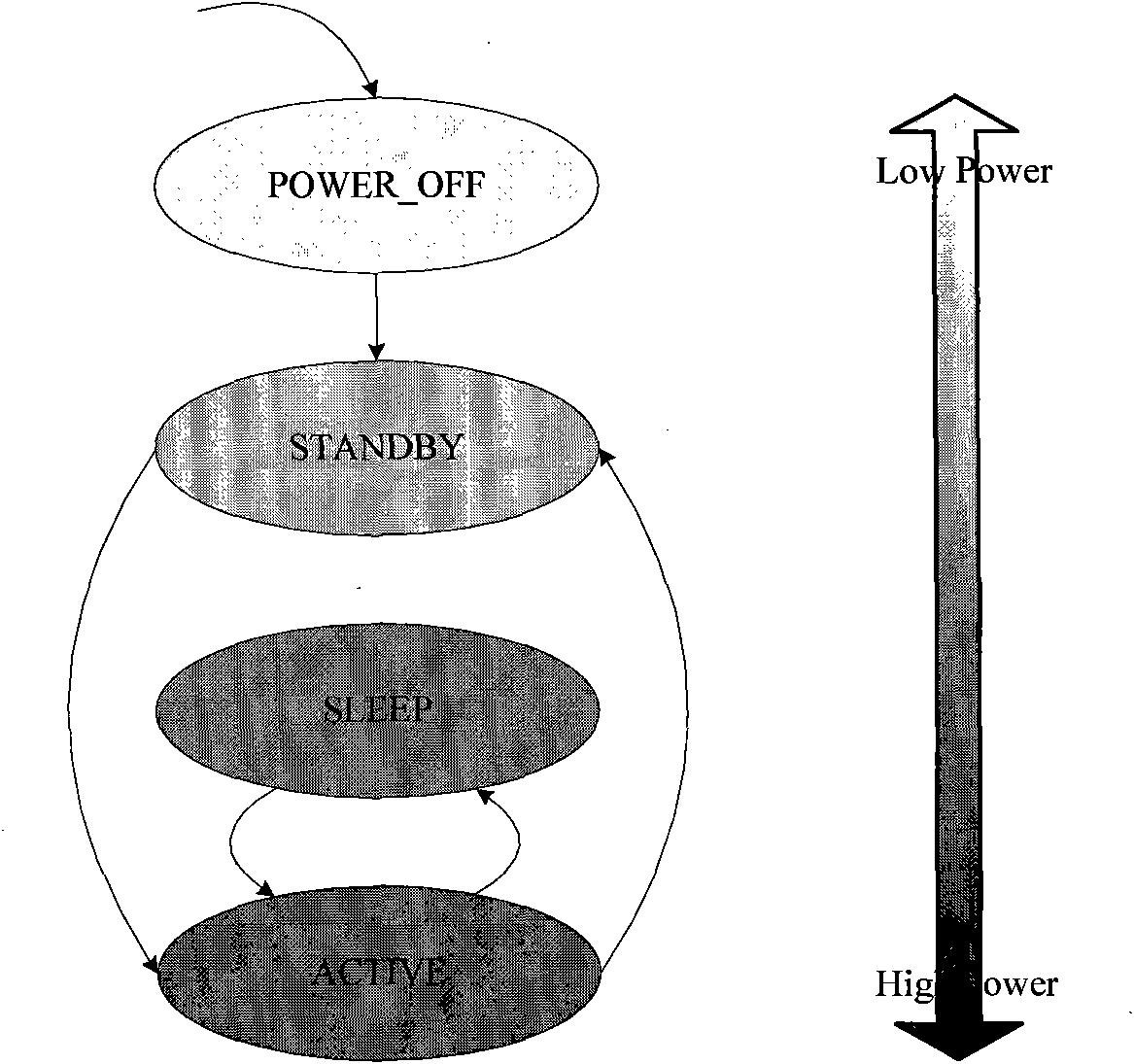

[0015] The module Power Management Unit (referred to as PMU) is powered by an off-chip normally-on 1.2V power supply, and the input clock is an optional low-frequency clock domain of 32.768KHz to 2MHz. The module implements the working state machine of the chip. In addition, during the switching process of each working state of the chip, the PMU module is responsible for completing the power switch and clock gating switch signals of all other circuits of the chip except the PMU circuit;

[0016] The module Host Interface is the protocol processor of the device interface, and the chip performs data interaction with the off-chip master device through the device interface;

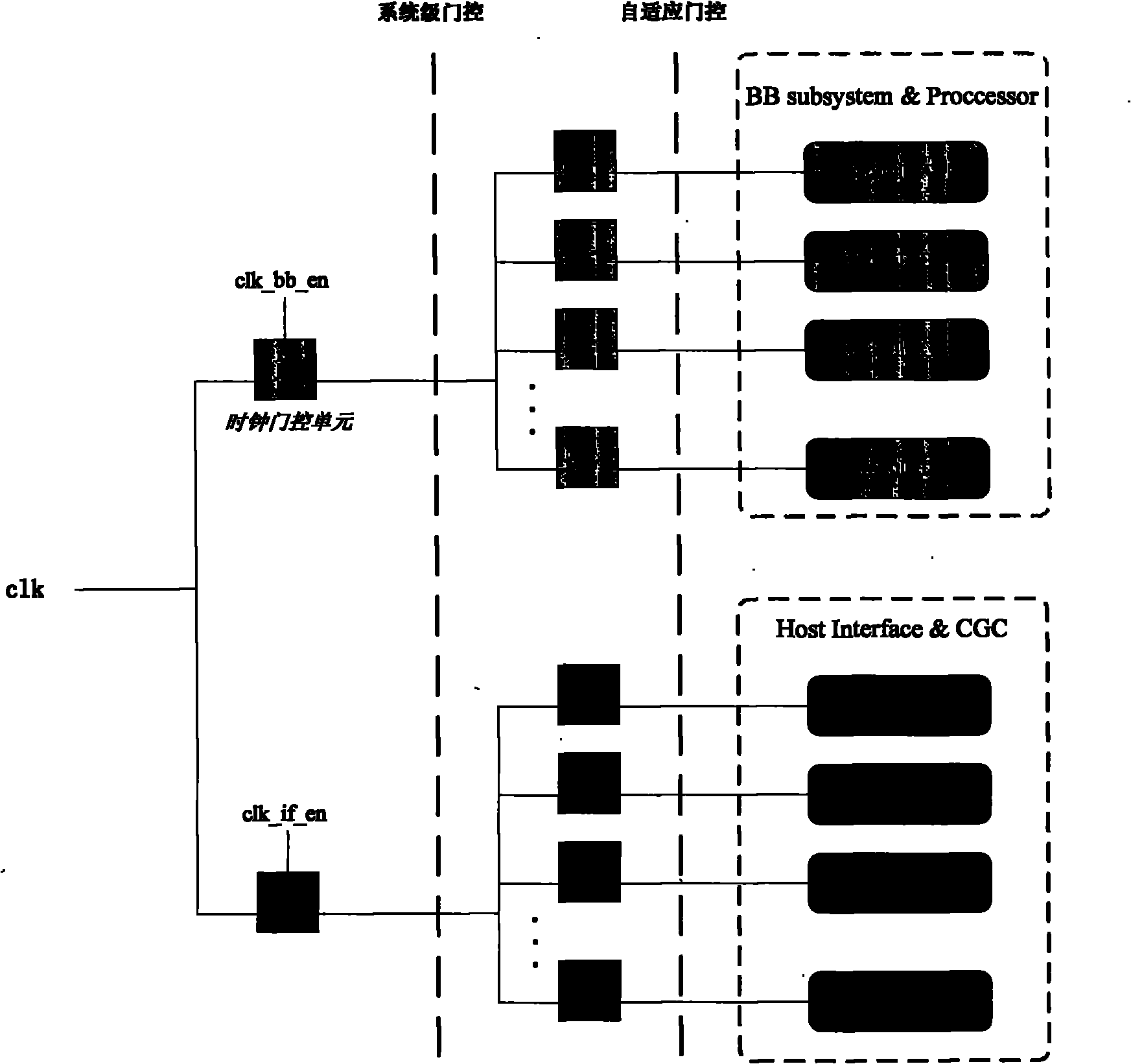

[0017] The module Clock Gating Control (CGC) completes the clock gating of each clock domain in the chip Host Interface and BB Subsystem, and completes the clock frequency switching of the Processor module.

[0018] The module Processor is an on-chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More