Method for reducing grid-induction drain leakage of semiconductor device

A semiconductor and drain leakage technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as complex processes, reduce the width of the sidewall, reduce the drain leakage current, and increase the sidewall effect of width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in combination with principle diagrams and specific operation examples.

[0025] see figure 2 As shown, the method for reducing gate-induced drain leakage of semiconductor devices in the present invention specifically includes the following steps:

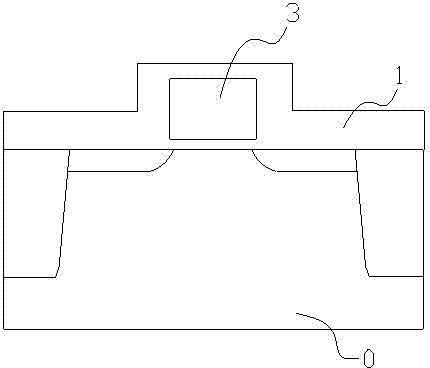

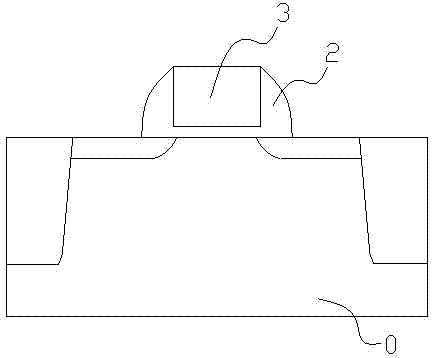

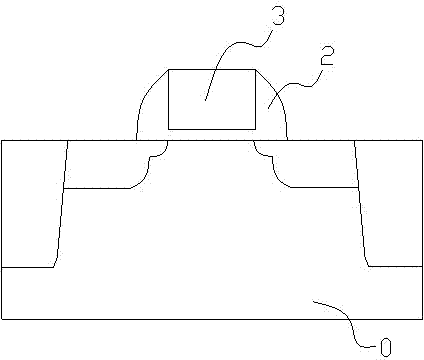

[0026] Such as Figure 3A As shown, a layer of sidewall film 1 is grown on a substrate 0 that has completed shallow trench isolation (STI) 4 on both sides. The sidewall film 1 can be a silicon oxide or silicon nitride film. There are low doped source and drain regions (LDD) 8 at the junction with the gate, and at the junction between the drain and the gate respectively. The sidewall film 1 is dry-etched, specifically, the sidewall film 1 is dry-etched using anisotropic plasma, and the introduced etching plasma 5 is incident on the source electrode 7. point and form a certain angle α with the vertical direction to form a spacer 2 on the gate 3 of the semiconductor devi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More