Interrupt handling method, interrupt controller and processor

A processing method and processor technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of large software overhead, and achieve the effect of small software overhead and reduced software overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

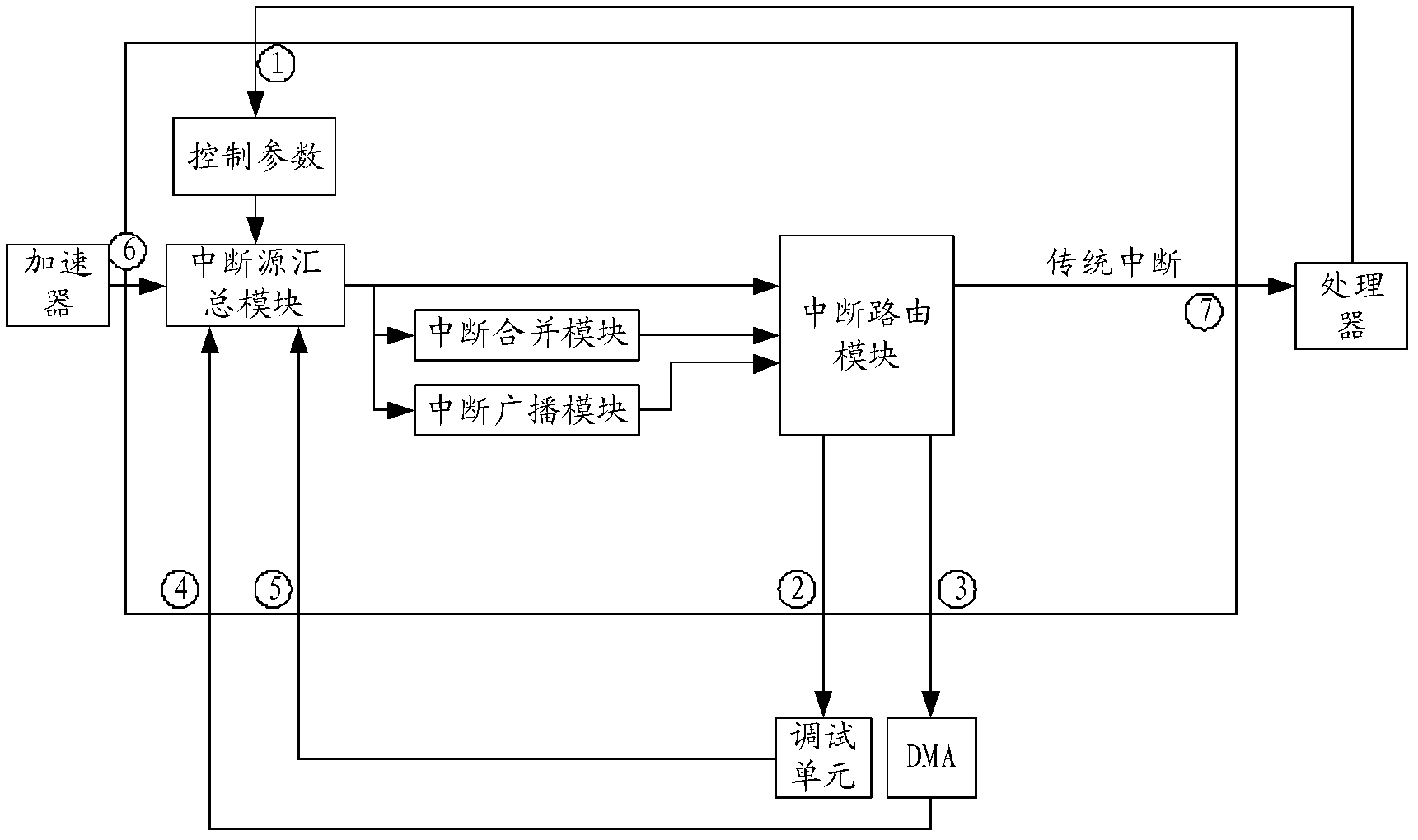

[0091] Based on the above, an implementation manner of step 503 includes:

[0092] The first grouping module divides each interrupt in the first interrupt group into different queues according to the interrupt response unit corresponding to each interrupt in the first interrupt group (that is, whether each interrupt is output to the processor, accelerator or DMA, etc.). Wherein, a queue corresponds to an interrupt response unit. If the interrupts in the first interrupt group correspond to interrupt response units as processors and accelerators, the first grouping module may divide the interrupts in the first interrupt group into two queues, which are processor queues and accelerator queues. After the interrupts in the first interrupt group are divided into different queues, the first grouping module outputs the interrupt status of the current highest priority interrupt in each queue to the status queue corresponding to the queue in the interrupt controller according to the pri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More