Patents

Literature

147results about How to "Increase processing function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

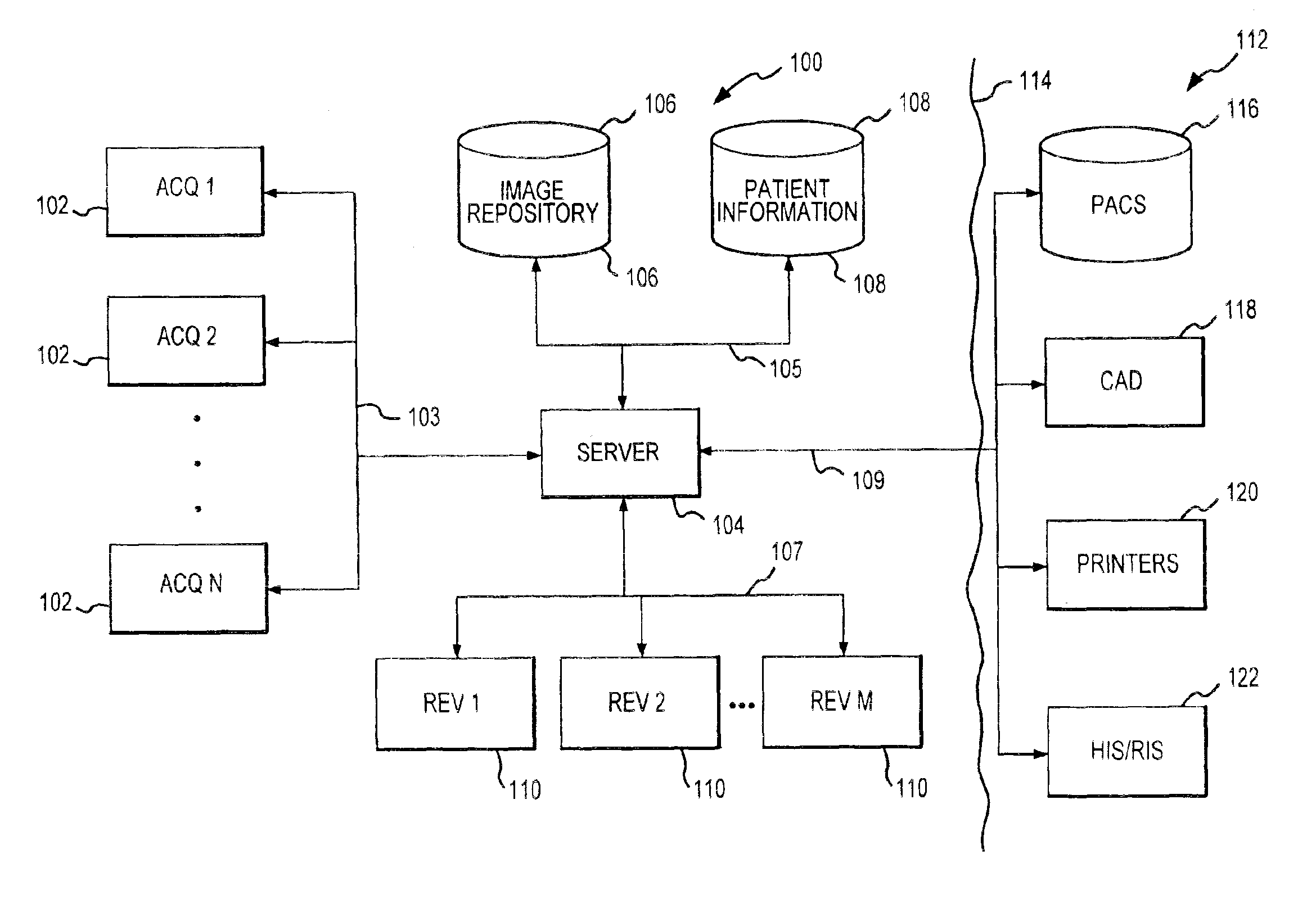

Automated background processing mammographic image data

InactiveUS6891920B1Improve efficiencyQuick displayPatient positioning for diagnosticsCharacter and pattern recognitionRapid accessDigital image

Disclosed is a mammographic imaging system and tools for processing mammographic images to enhance image acquisition and review workflow. The systems and tools enable rapid access to digital image information providing for improved workflow management and identification of images, upon initial review. The system and tools also allow for background processing of image information to reduce workflow delay. Specifically, digital images are processed in the background, i.e., they are automatically processed, free from specific task-orientated direction by a user, using resources that are not otherwise occupied addressing user-directed tasks. Background processing that may be supported includes preprocessing and interim processing. Preprocessing refers to processing of an image that occurs prior to initial review of that image by a physician. Interim processing refers to background processing that occurs during a review session, e.g., in a time period between initial review and a subsequent review of an image.

Owner:HOLOGIC INC

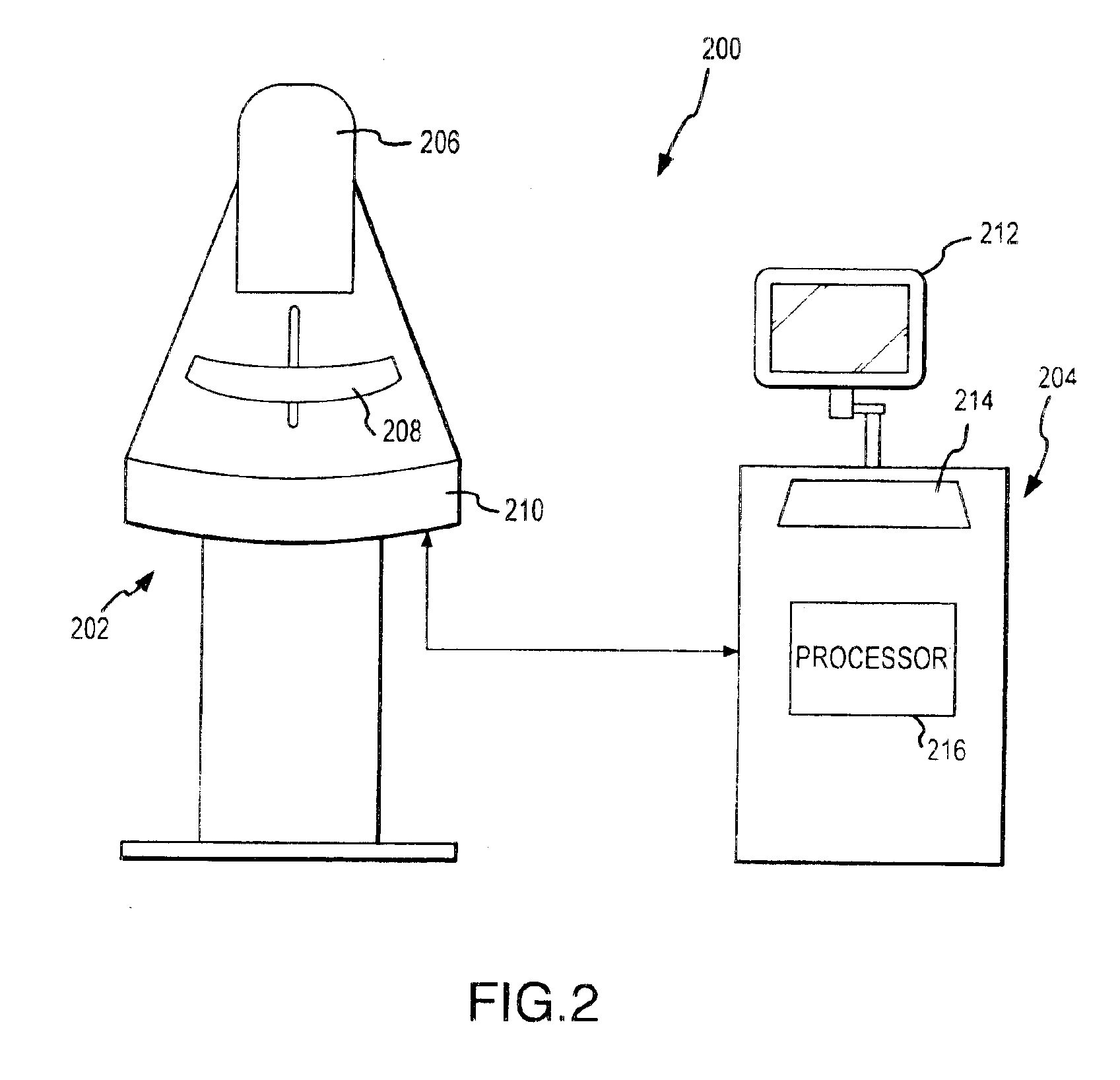

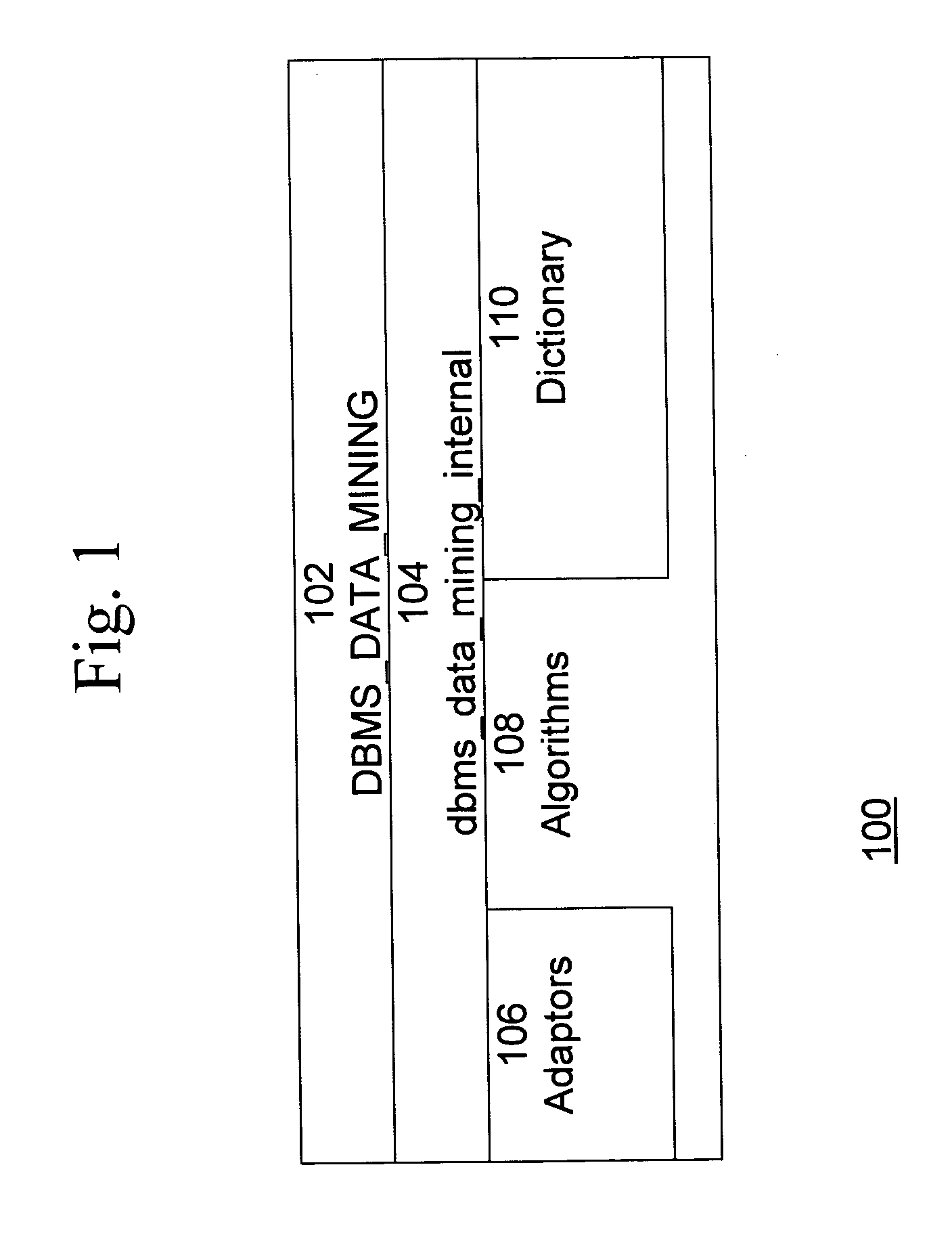

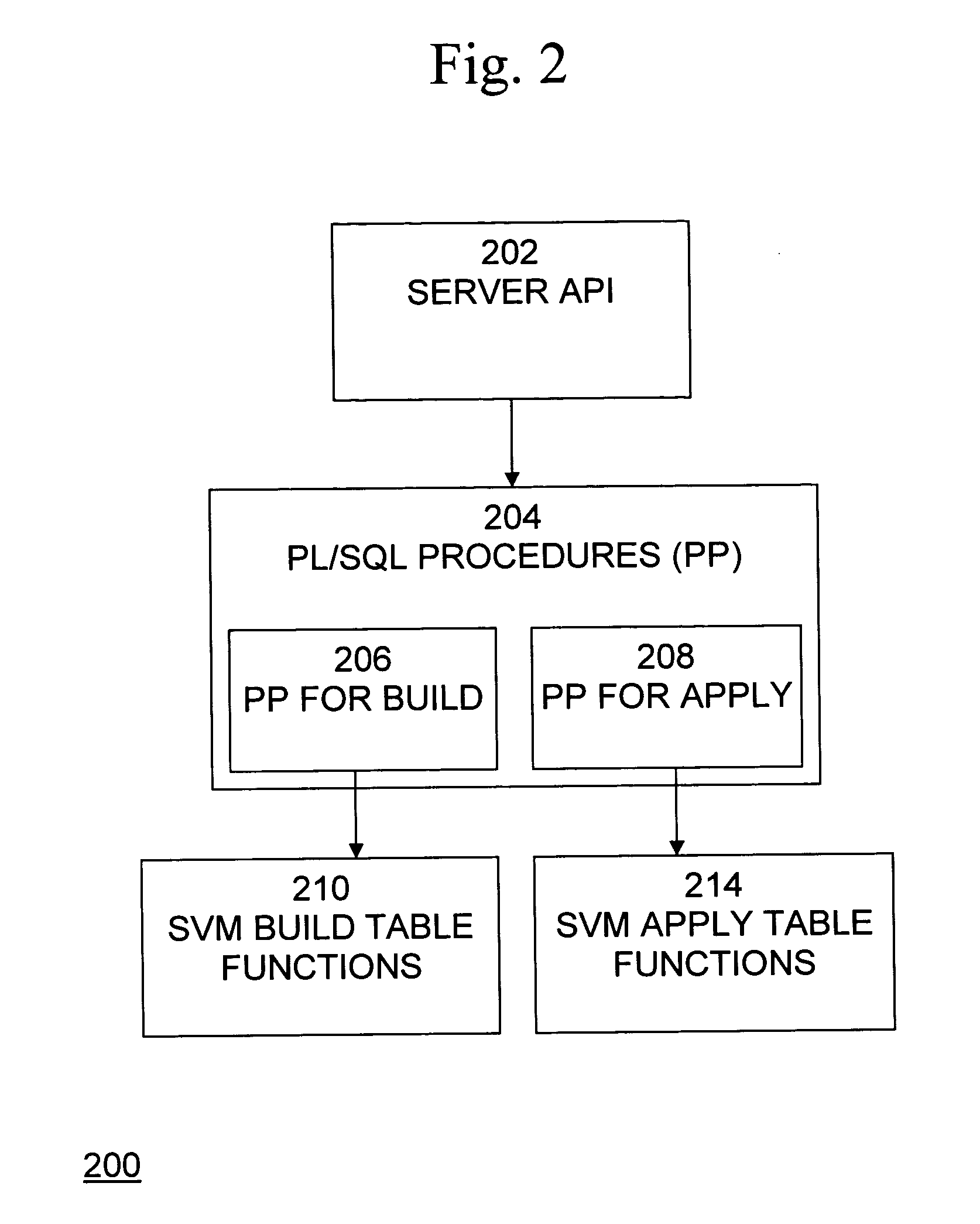

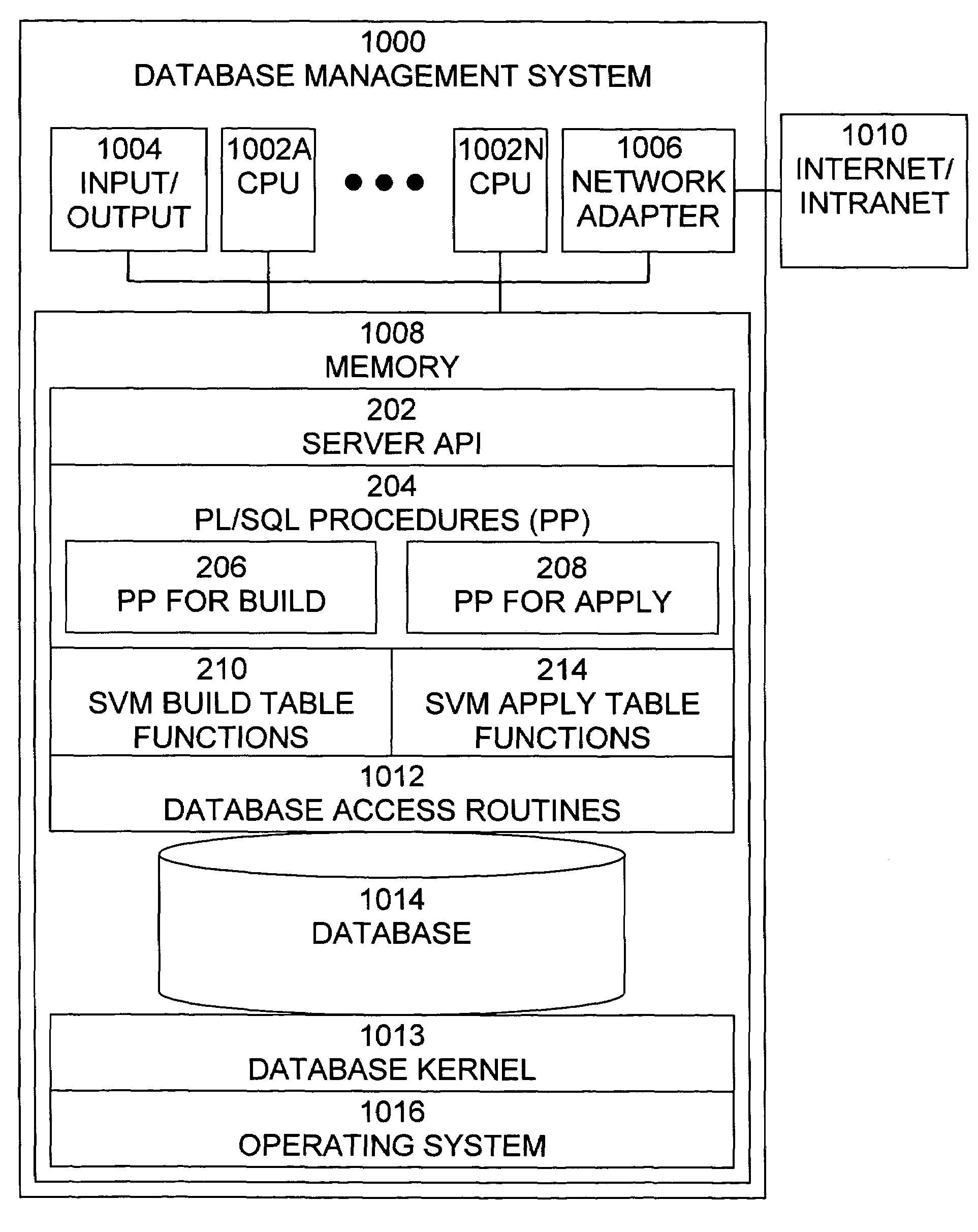

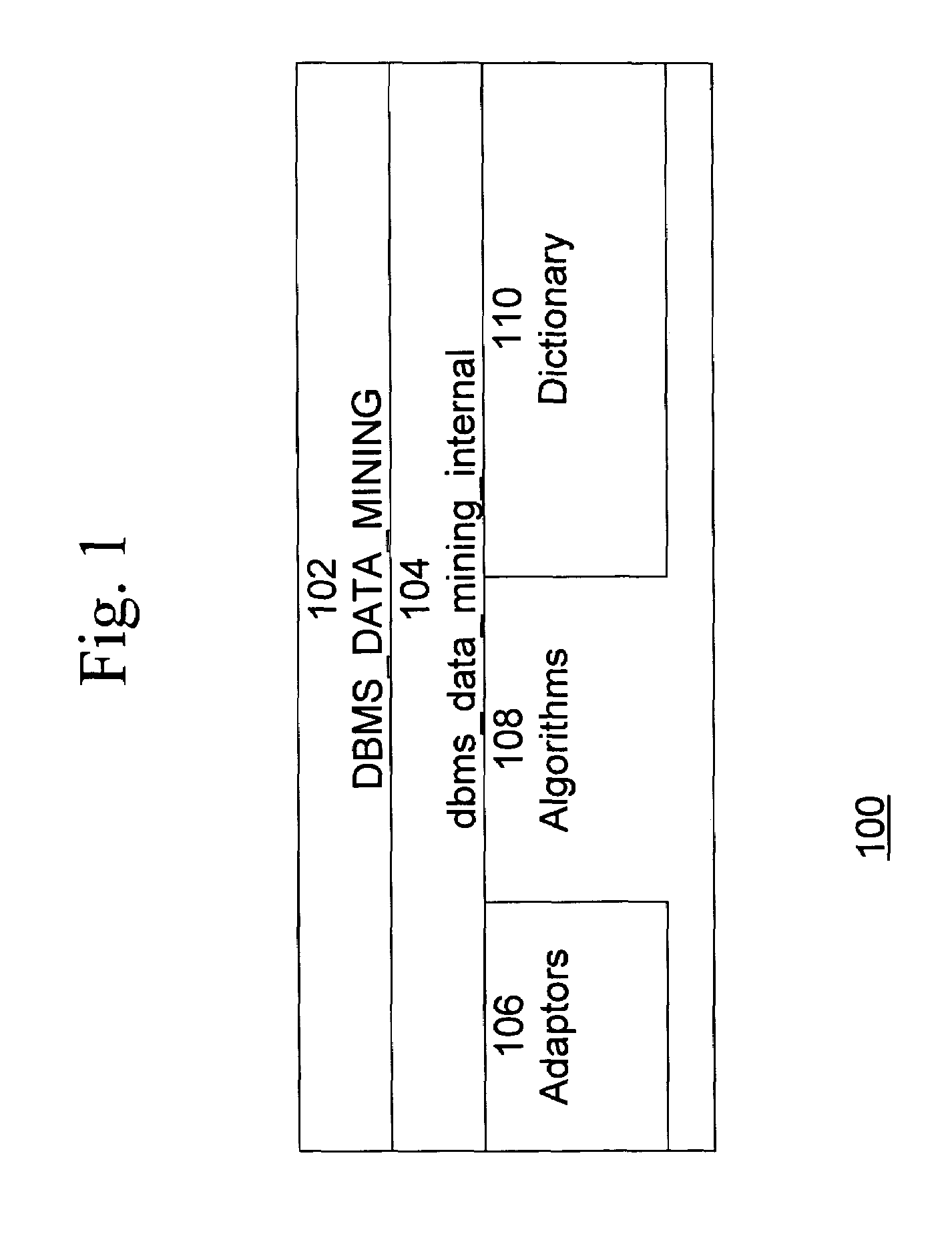

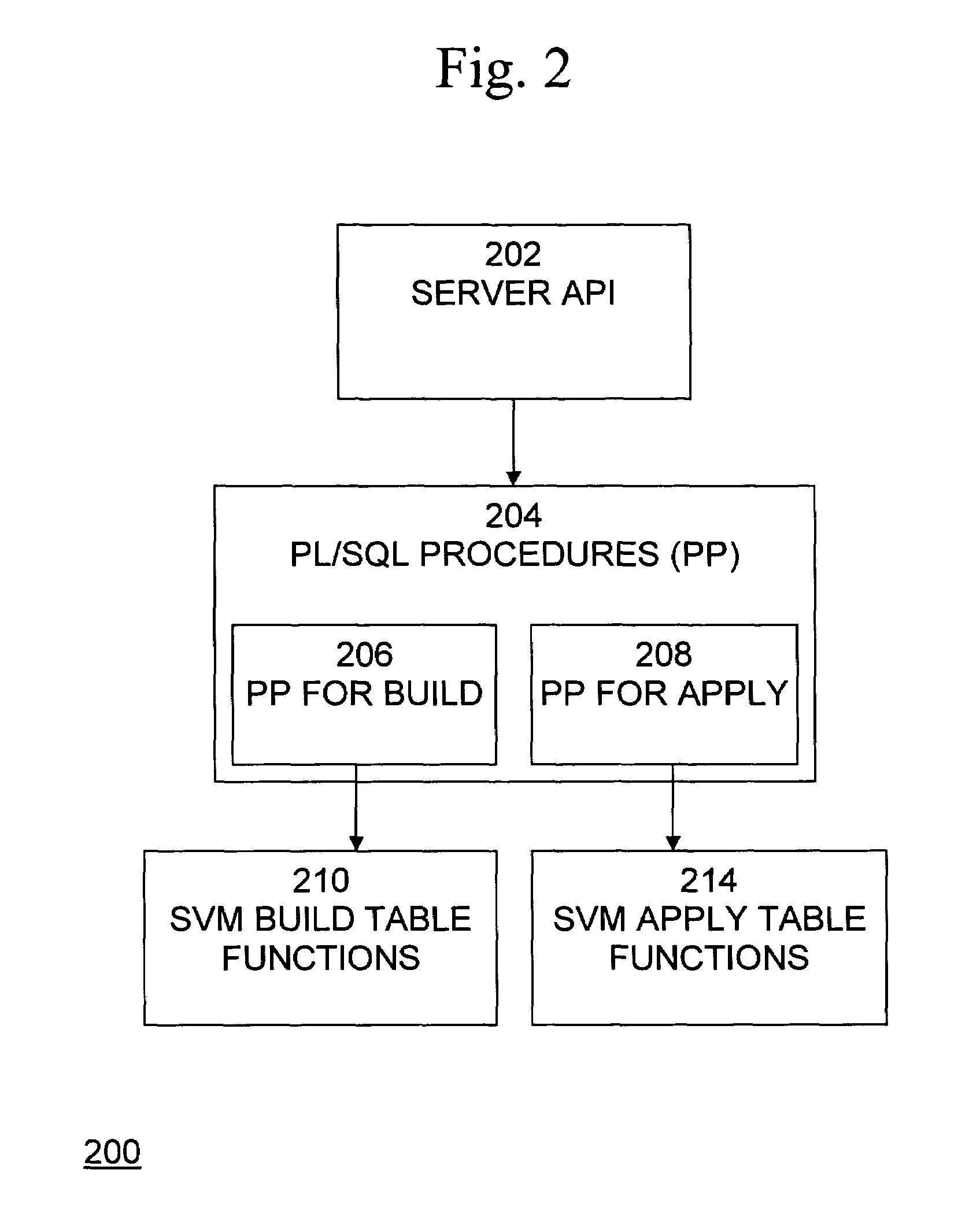

Support vector machines processing system

ActiveUS20050049990A1Reduce computational costReduce data movementDigital data processing detailsDigital computer detailsClient-sideData security

An implementation of SVM functionality improves efficiency, time consumption, and data security, reduces the parameter tuning challenges presented to the inexperienced user, and reduces the computational costs of building SVM models. A system for support vector machine processing comprises data stored in the system, a client application programming interface operable to provide an interface to client software, a build unit operable to build a support vector machine model on at least a portion of the data stored in the system, based on a plurality of model-building parameters, a parameter estimation unit operable to estimate values for at least some of the model-building parameters, and an apply unit operable to apply the support vector machine model using the data stored in the system.

Owner:ORACLE INT CORP

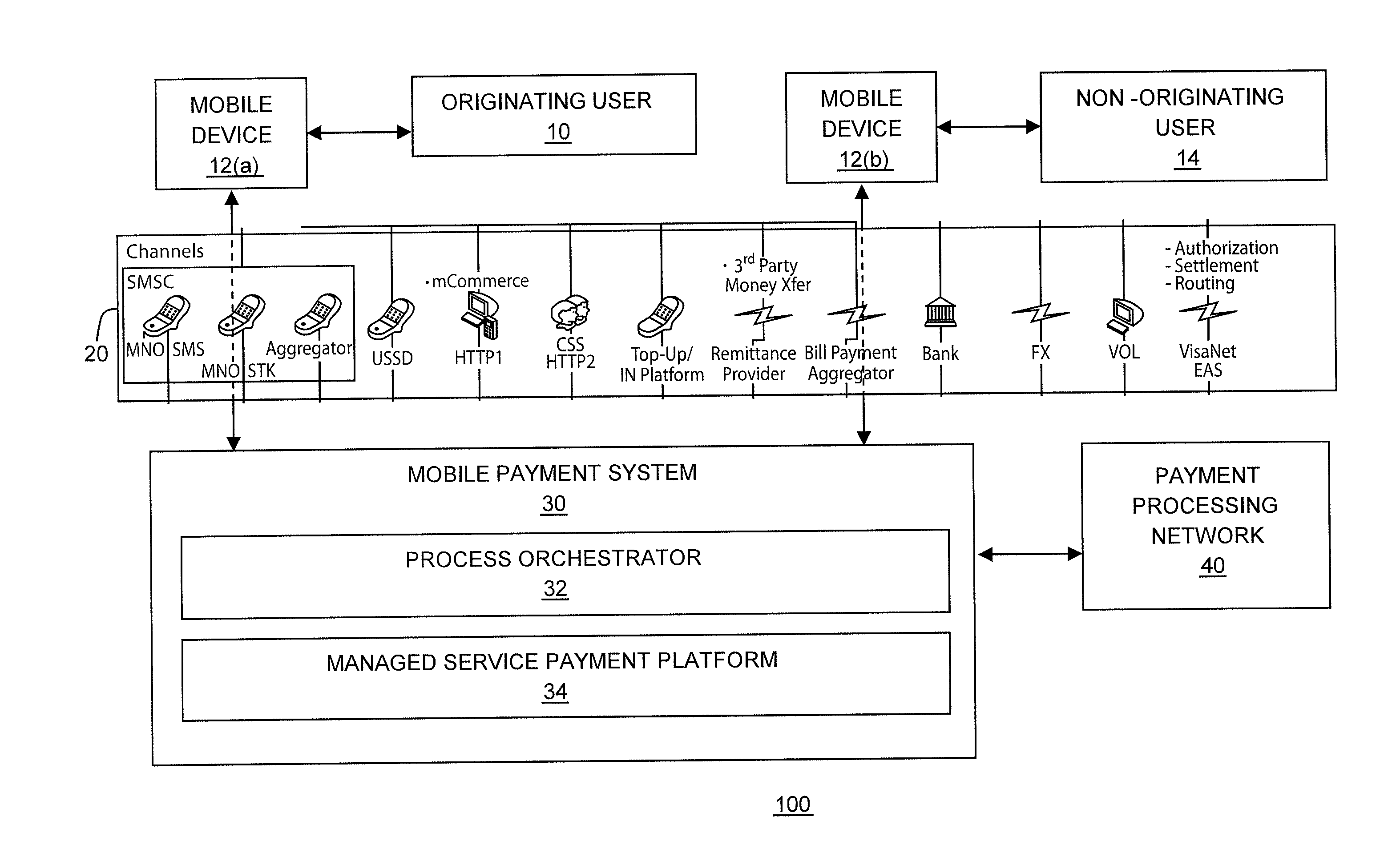

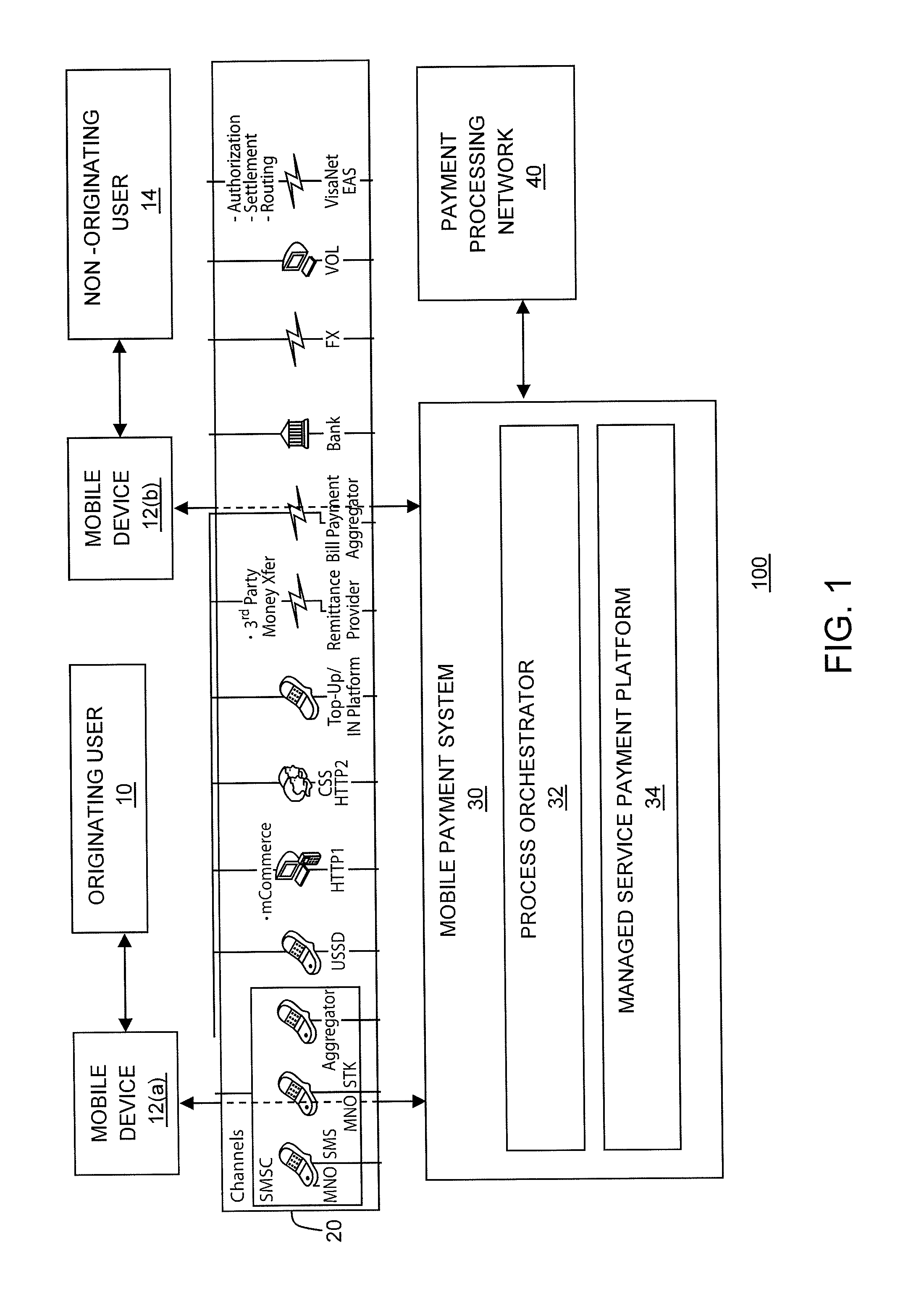

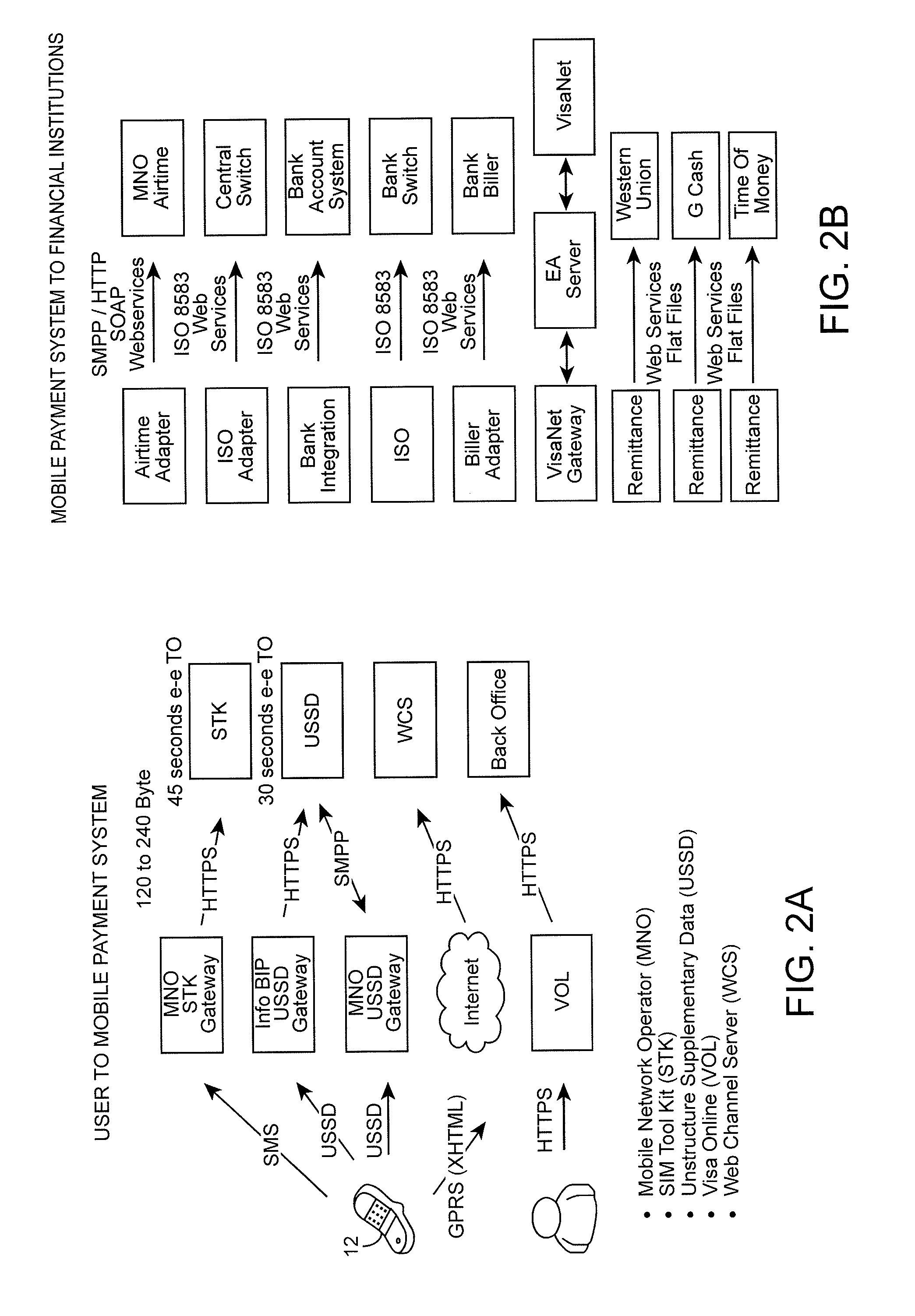

Mobile managed service

InactiveUS20130204785A1Reduce chanceIncrease processing functionFinancePayment architectureFinancial transactionMobile device

One embodiment of the invention is directed to a method comprising receiving, at a mobile payment system, transaction information from a mobile device operated by an originating user. The method further comprises generating, by the mobile payment system, a transaction request message using the transaction information from the mobile device operated by the originating user and analyzing, by the mobile payment system, the transaction request message to determine a type of the transaction. The method further comprises processing, by the mobile payment system, the transaction based on the type of the transaction, wherein the mobile payment system is configured to integrate at least two of an issuer, acquirer, and payment processing network functional modules.

Owner:VISA INT SERVICE ASSOC

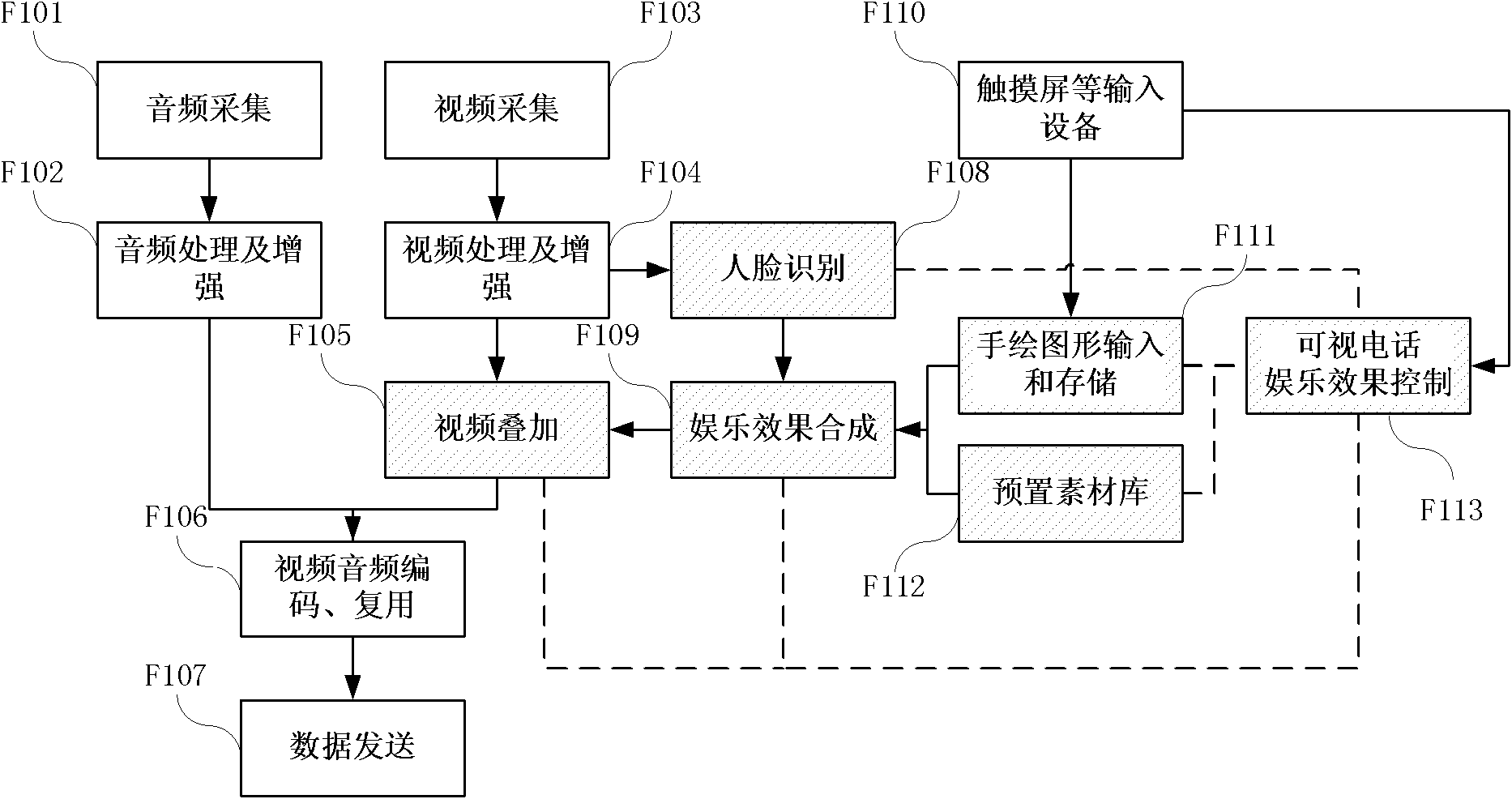

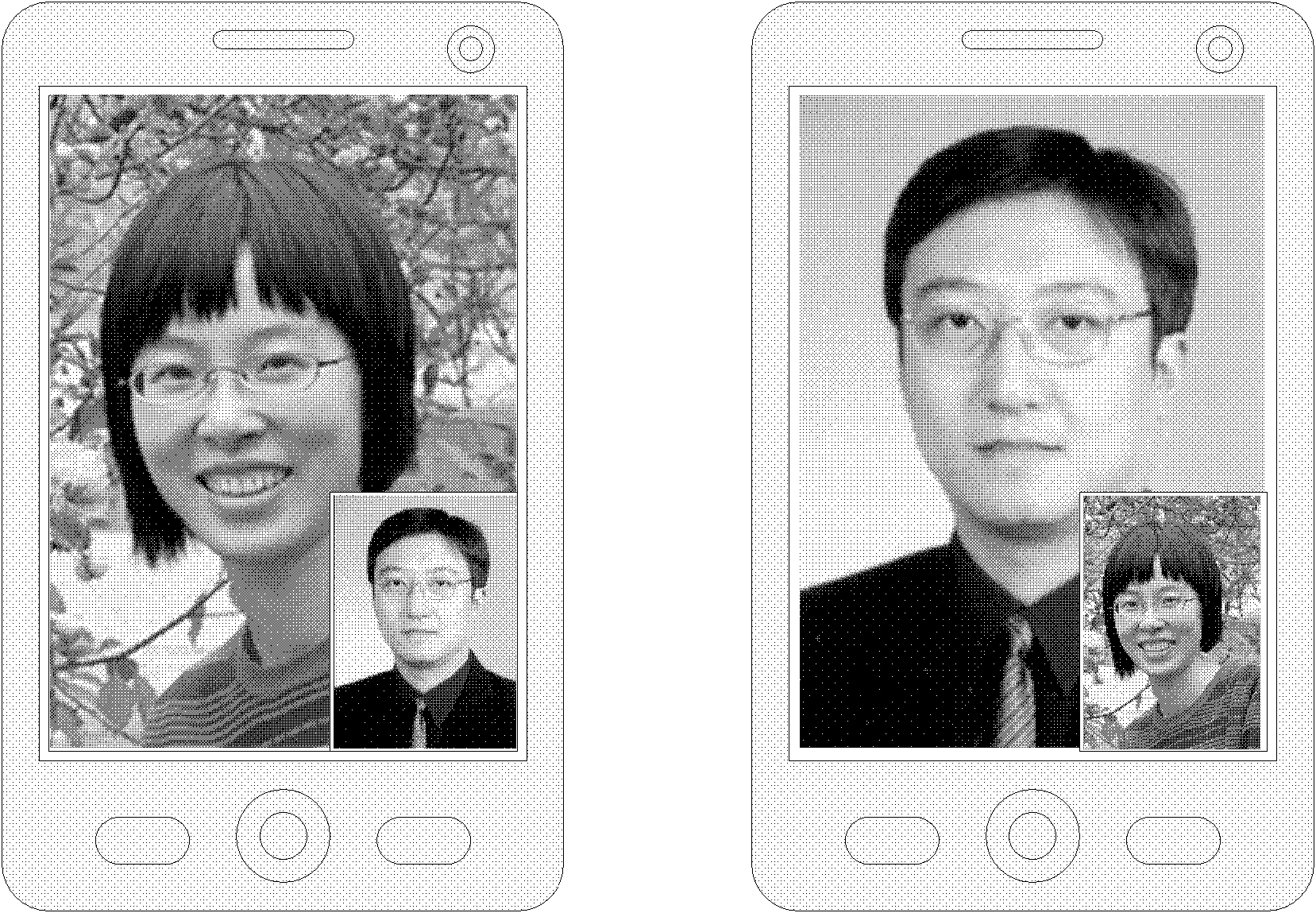

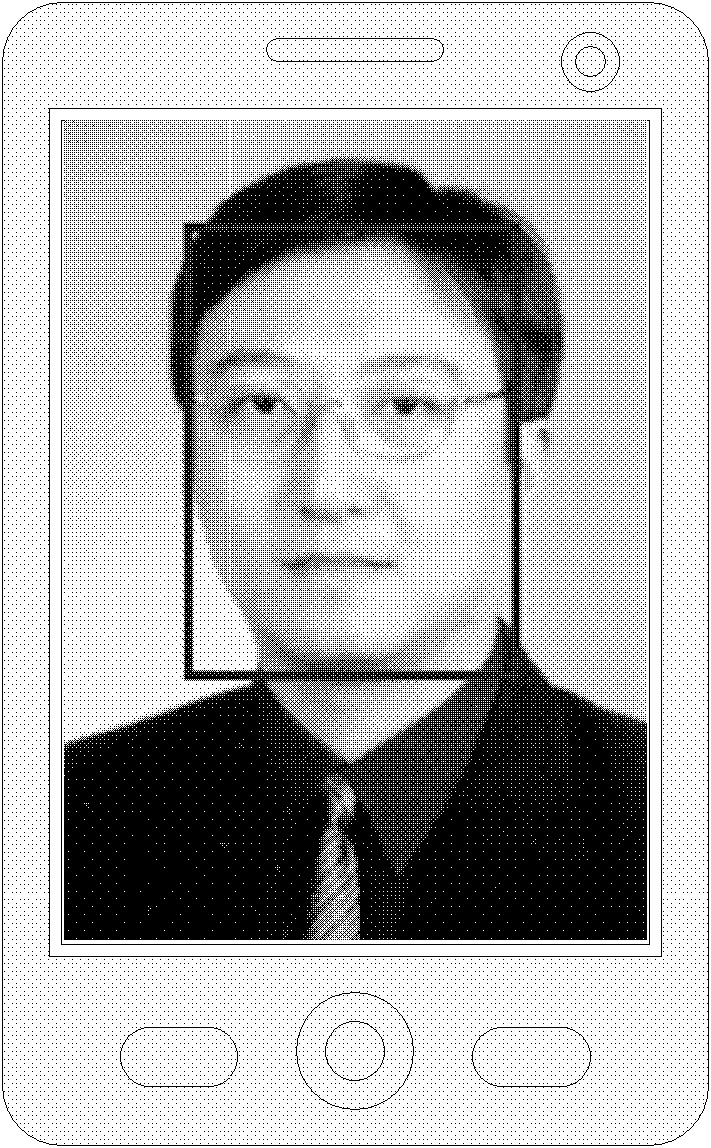

Method and device for processing images in videophone

InactiveCN102075727AAdd funImprove profit growth pointTelevision system detailsColor television detailsGrowth pointImage processing

The invention discloses a method and a device for processing images in a videophone. The method comprises the following steps of: acquiring a video image of a near-end user; adding graphs and / or characters to the video image to obtain the processed video image; and transmitting the processed video image to a far-end user. The device comprises an image acquisition module, an image entertainment enhancement module and a transmission module, wherein the image acquisition module is used for acquiring the video image of the near-end user; the image entertainment enhancement module is used for adding graphs and / or characters to the video image to obtain the processed video image, and transmitting the processed video image to the transmission module; and the transmission module is used for transmitting the processed video image to the far-end user. On the basis of video call, the video image processing function is increased, and the interest and playability of the video call are improved; and compared with the prior art, the invention can attract more videophone users and improves profit growth points of operators.

Owner:ZTE CORP

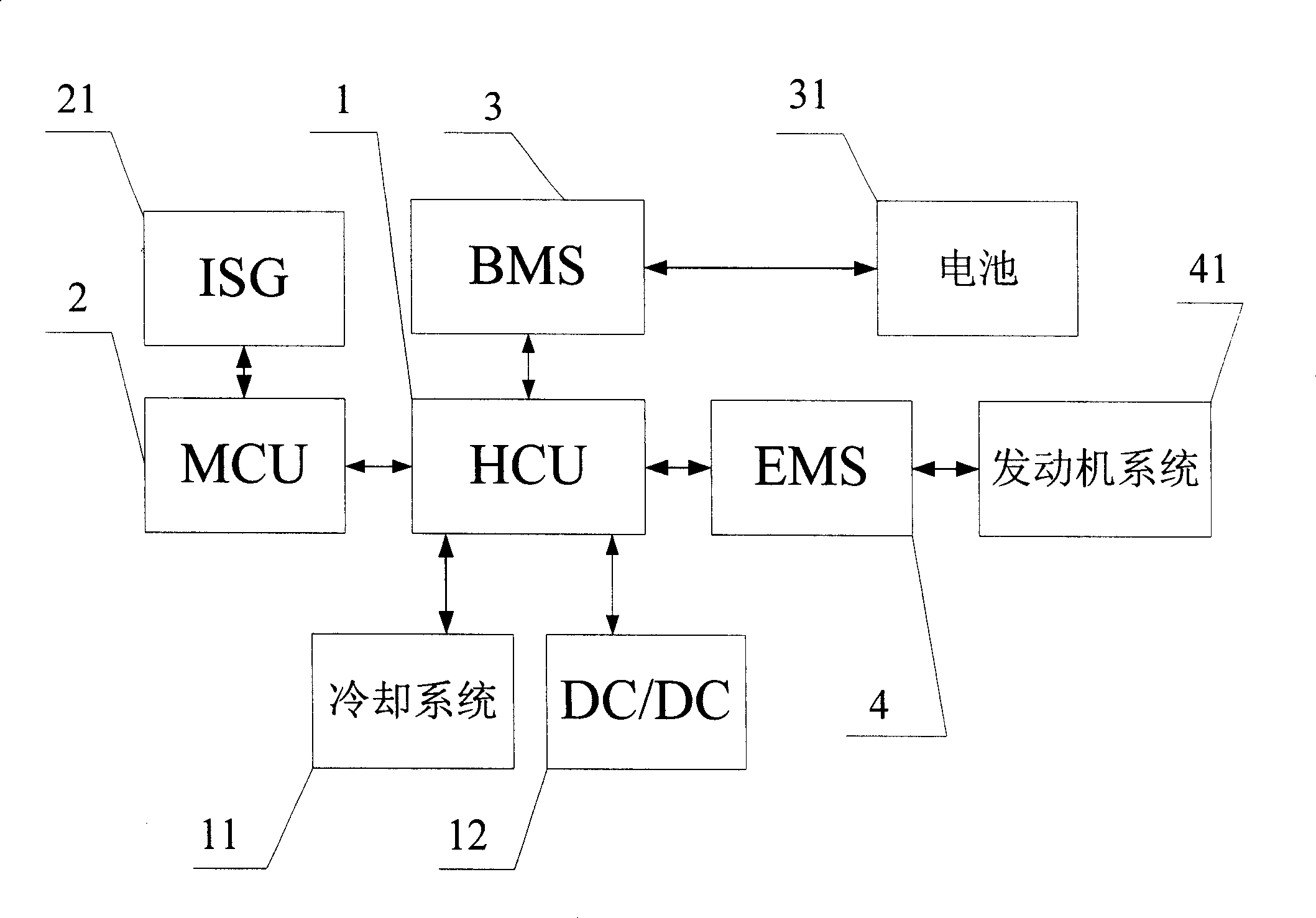

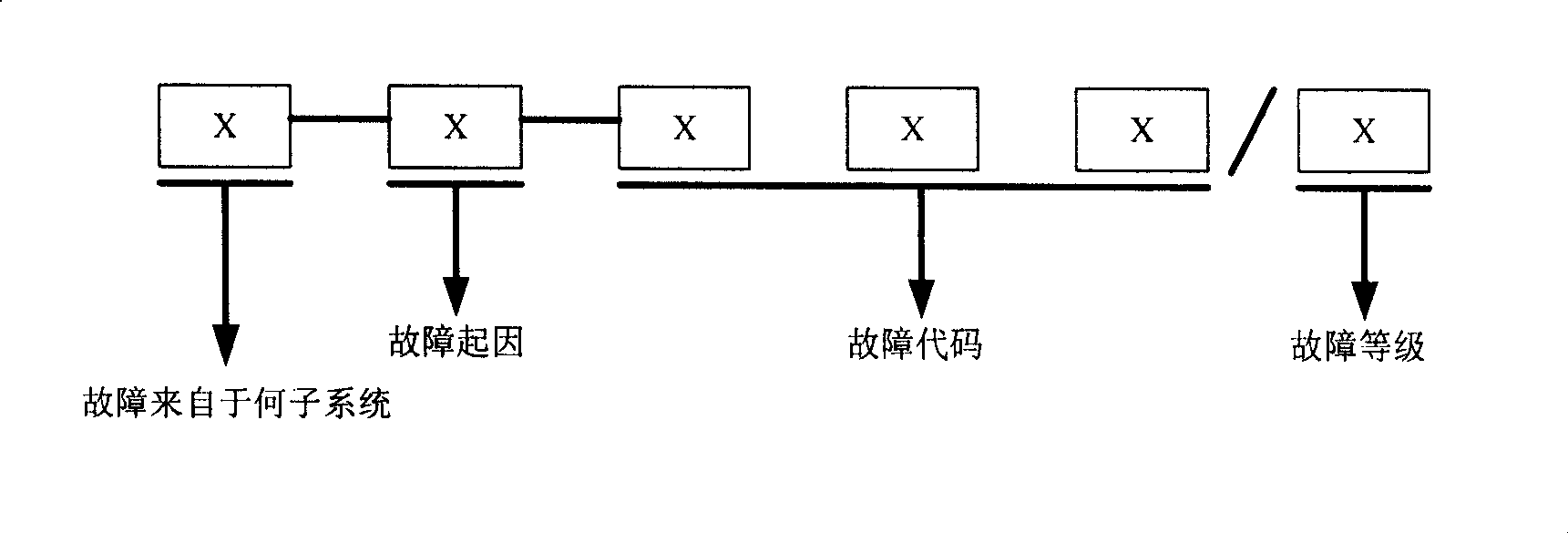

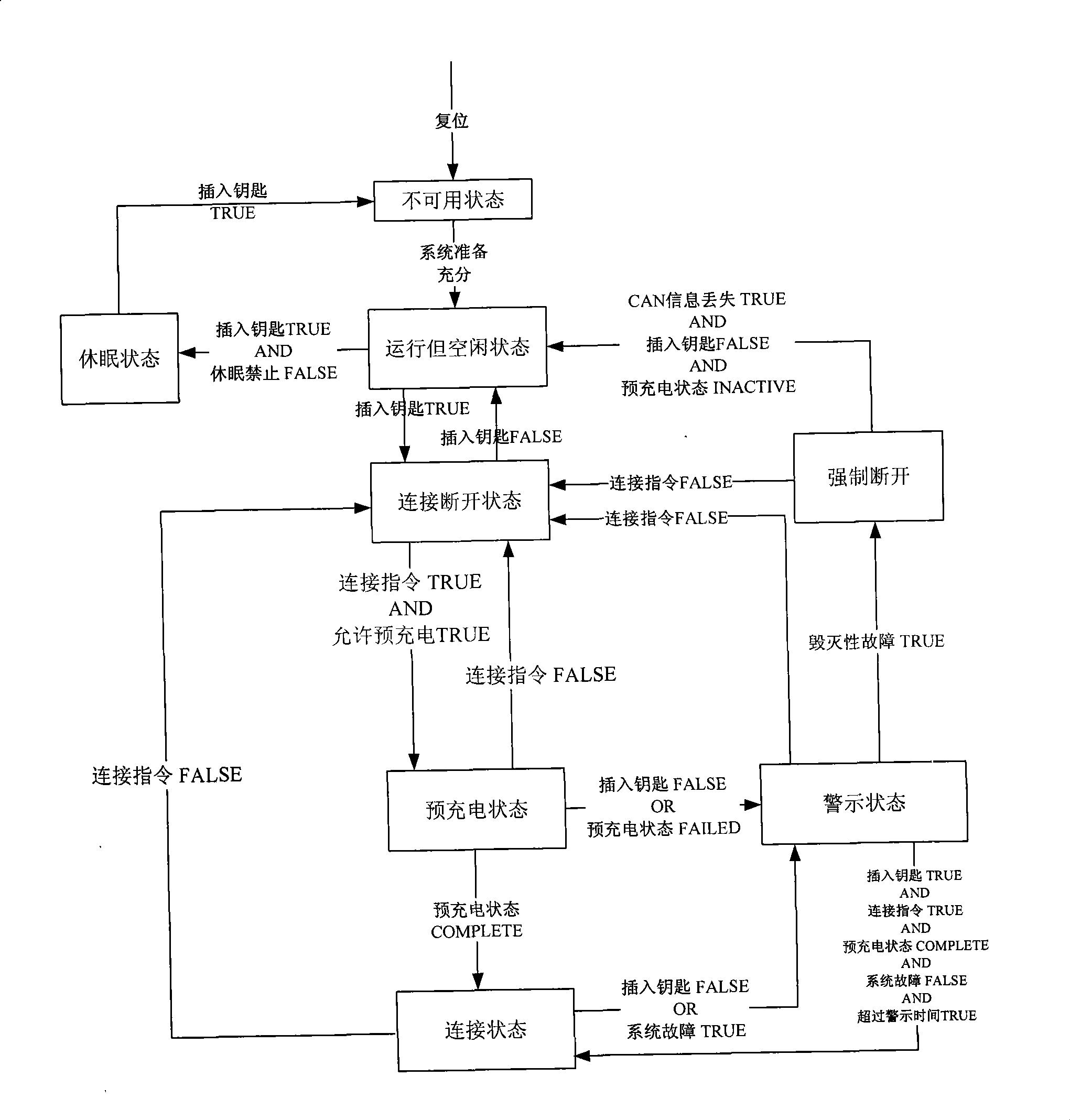

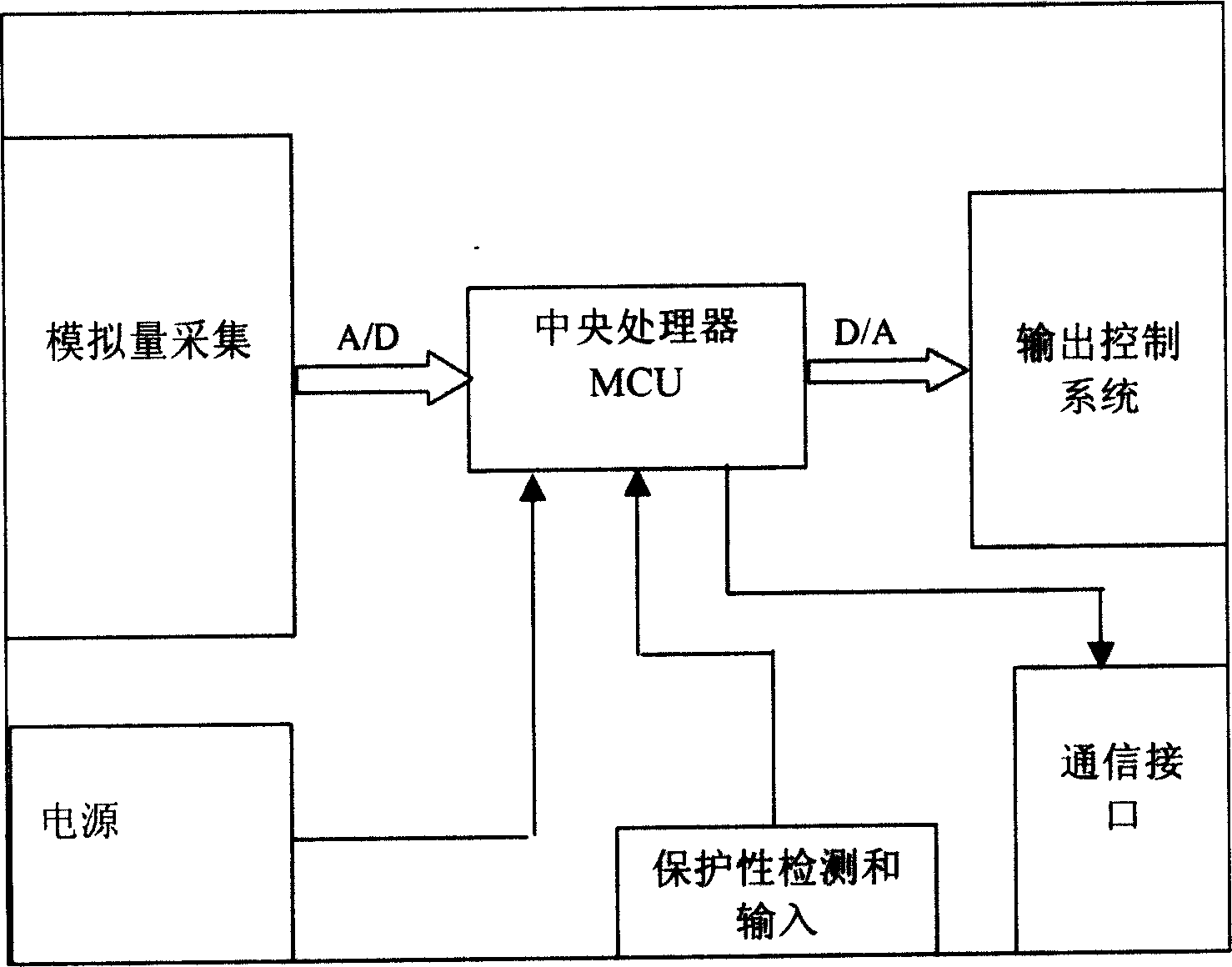

Fault detecting and processing method for hybrid vehicle

InactiveCN101364111AIncrease detection functionIncrease processing functionElectric testing/monitoringElectrical batteryHandling system

The invention discloses a fault detecting and handling method for a hybrid vehicle and a fault detecting and handling system using the method. The technical proposal is as follows: the method adopts the intelligent control modules of the hybrid vehicle, wherein the intelligent control modules include a hybrid power control unit, an electrical control unit, a battery management system and an engine management system; the fault handling system of the hybrid power control unit is adopted as the fault handling decision center, and the fault handling units of the electrical control unit, the battery management system and the engine management system are adopted as the sub-systems; the decision center and the subsystems cooperate to detect and handle the fault. The system and the method are applicable in the control system of the vehicle (particularly hybrid vehicle) to enhance the fault detection and handling capability.

Owner:CHERY AUTOMOBILE CO LTD

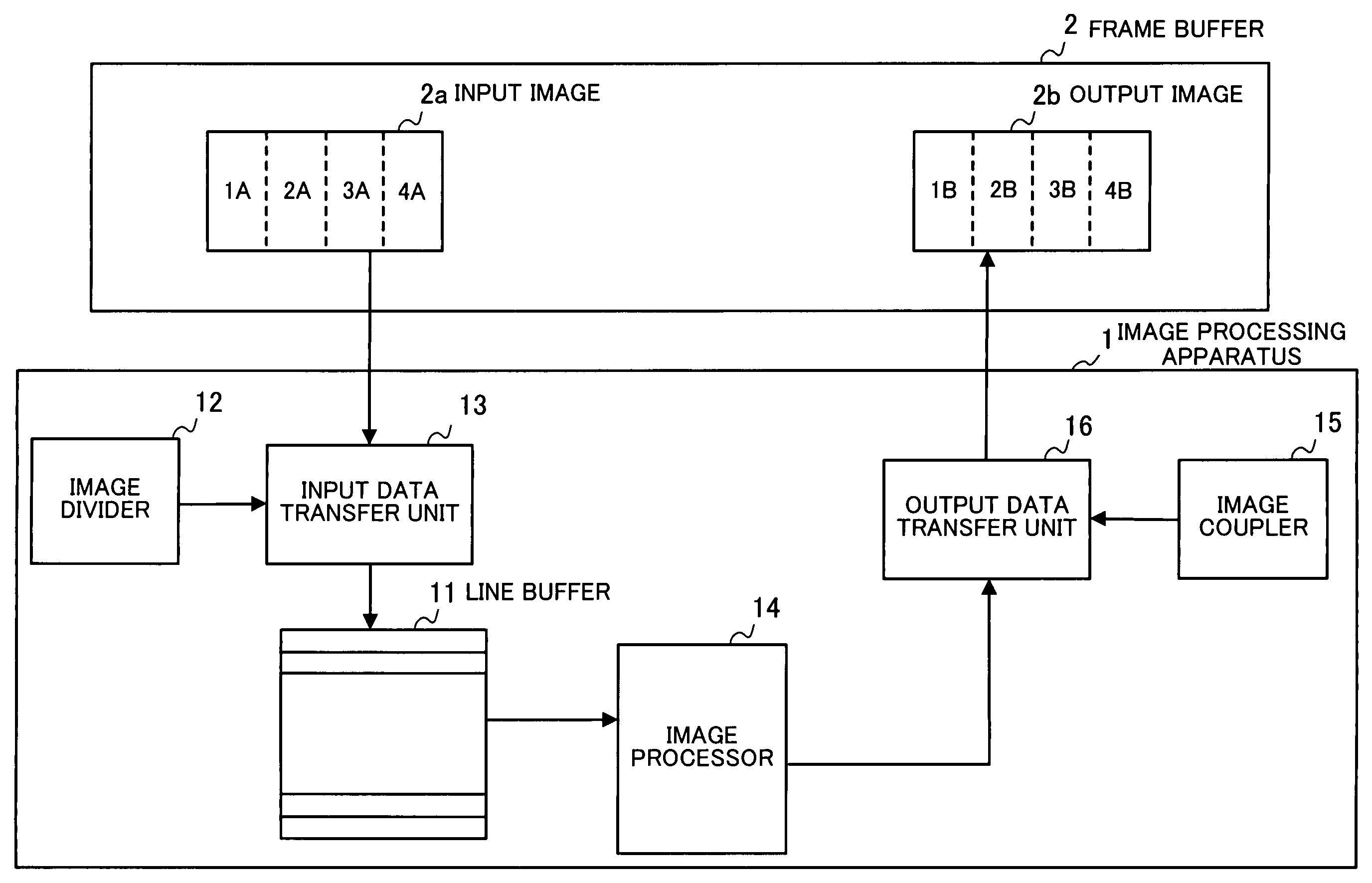

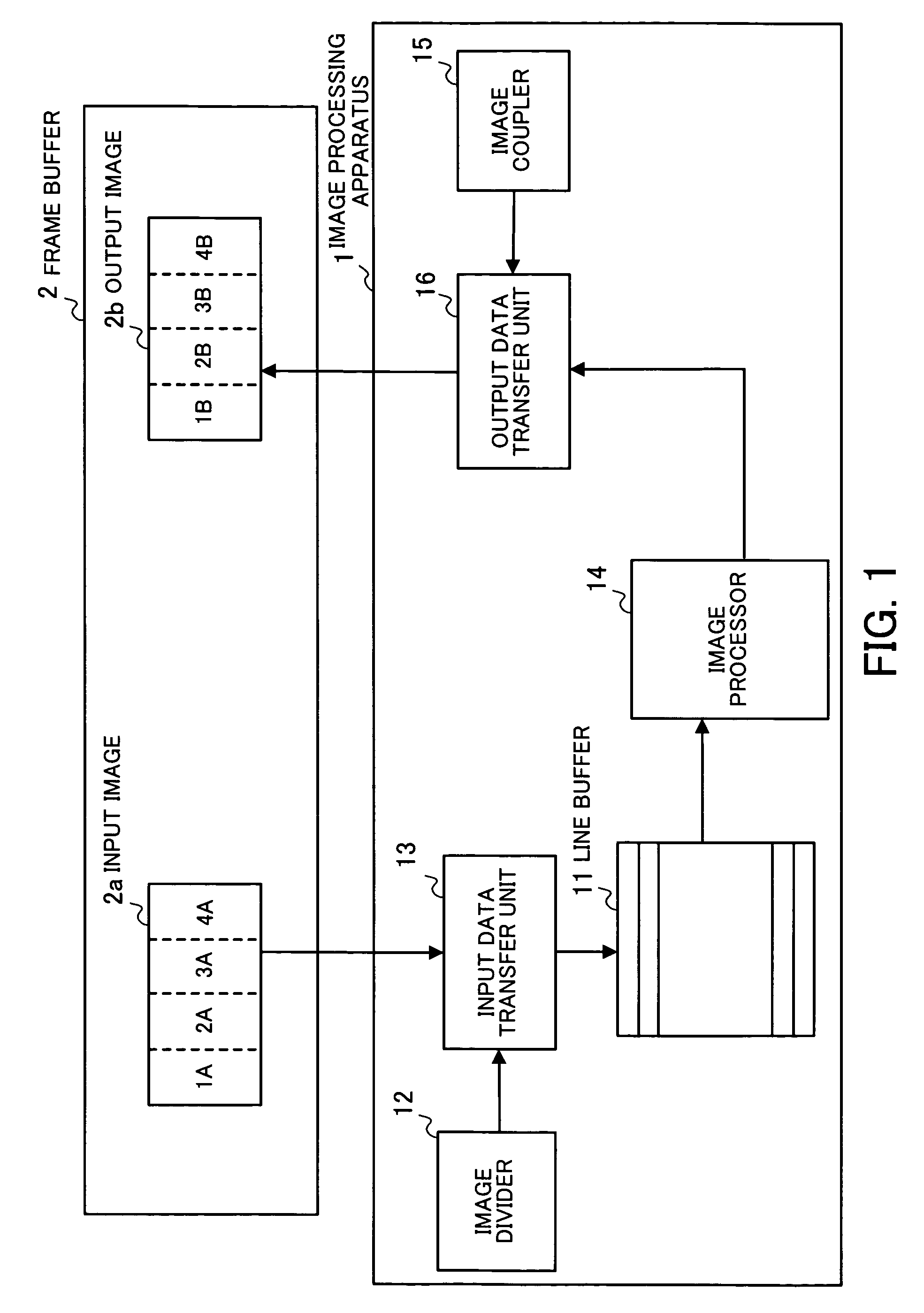

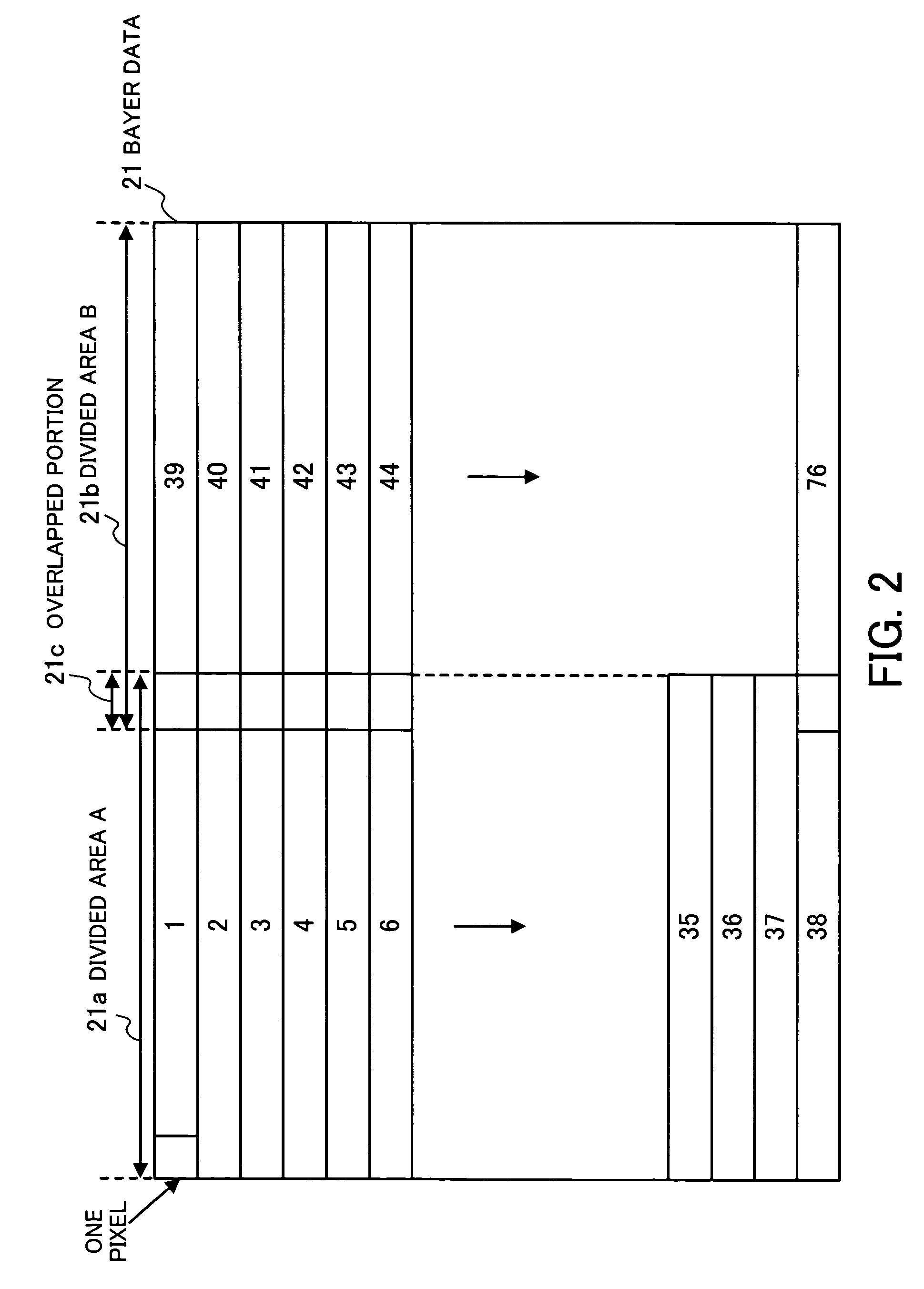

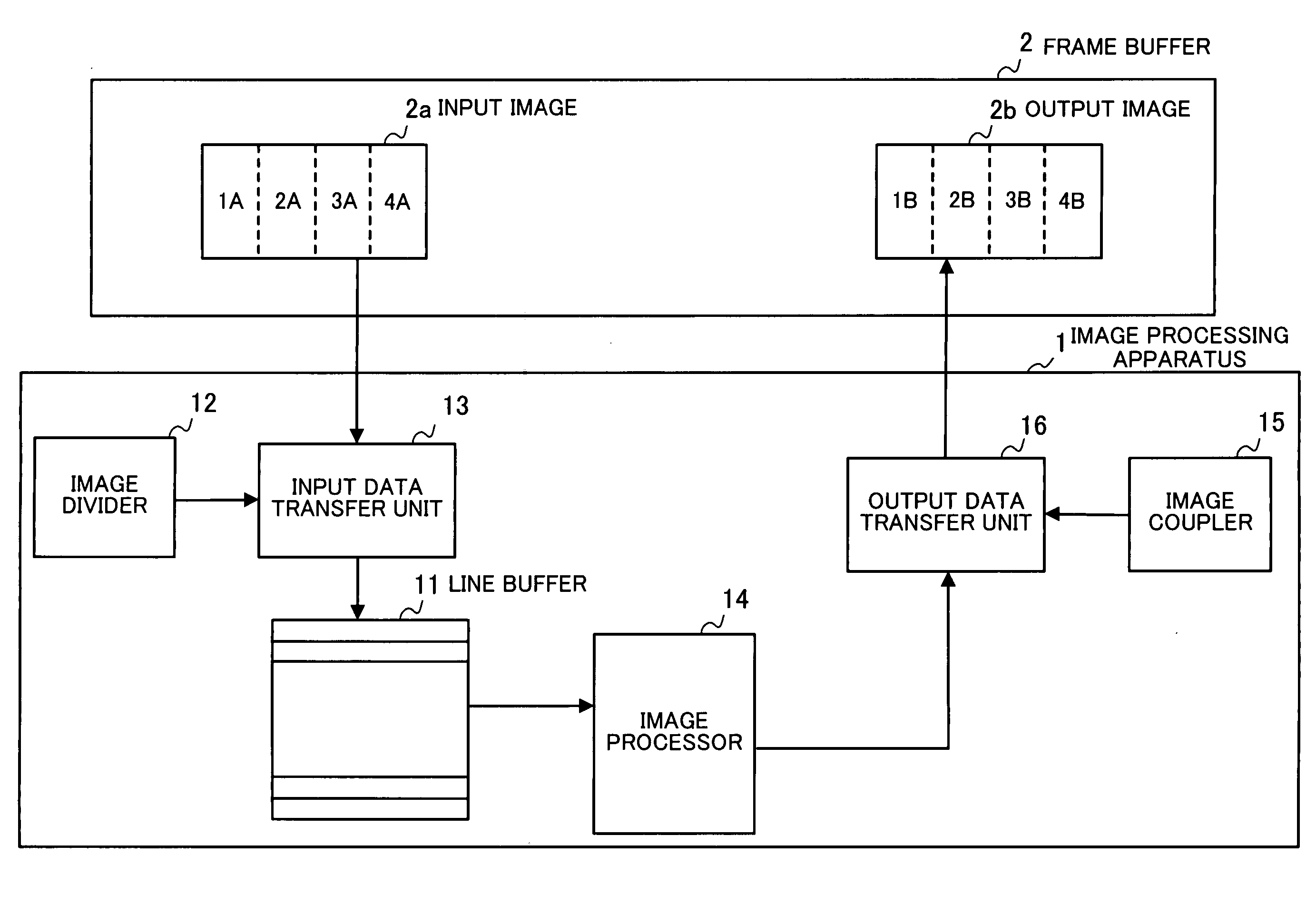

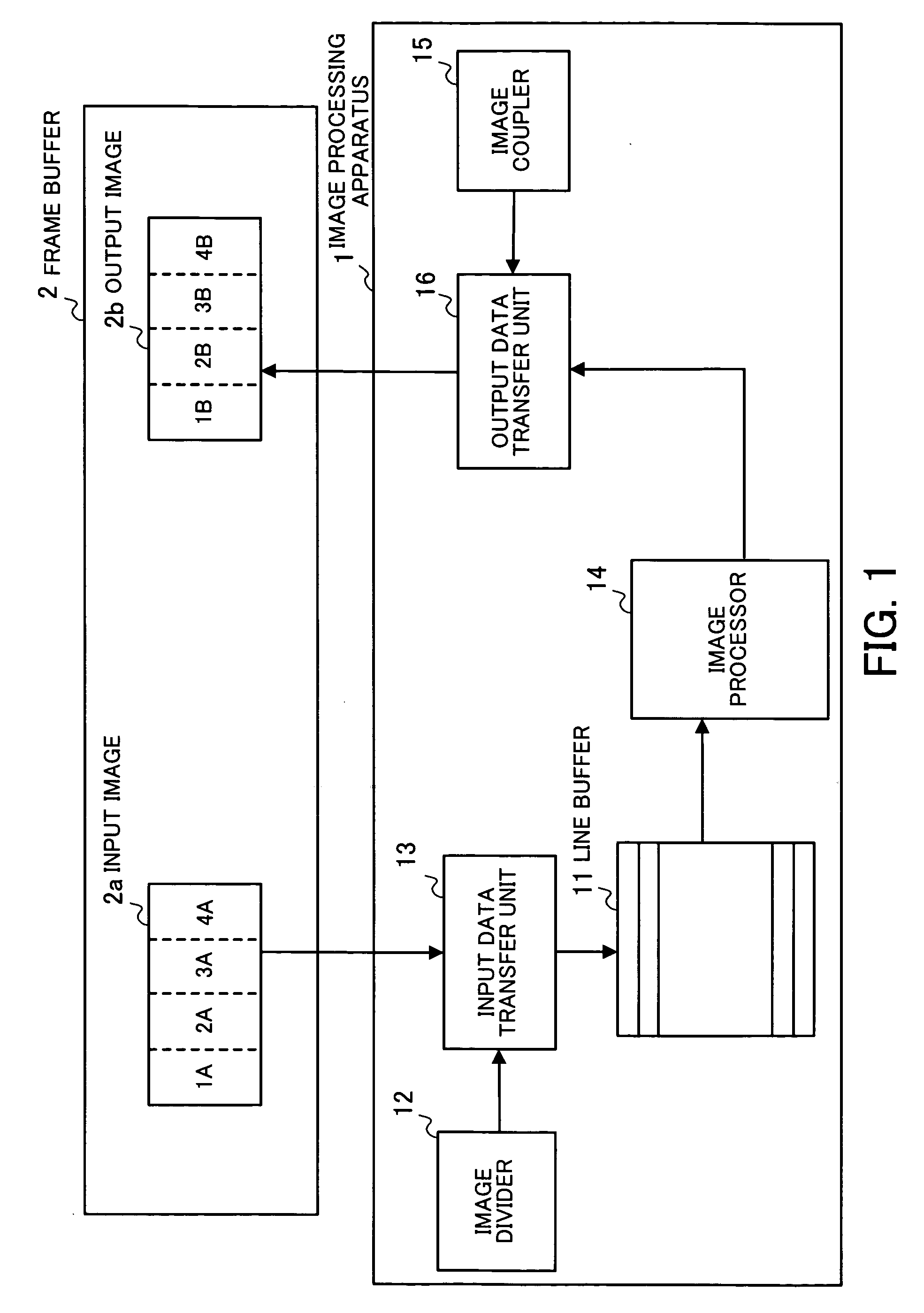

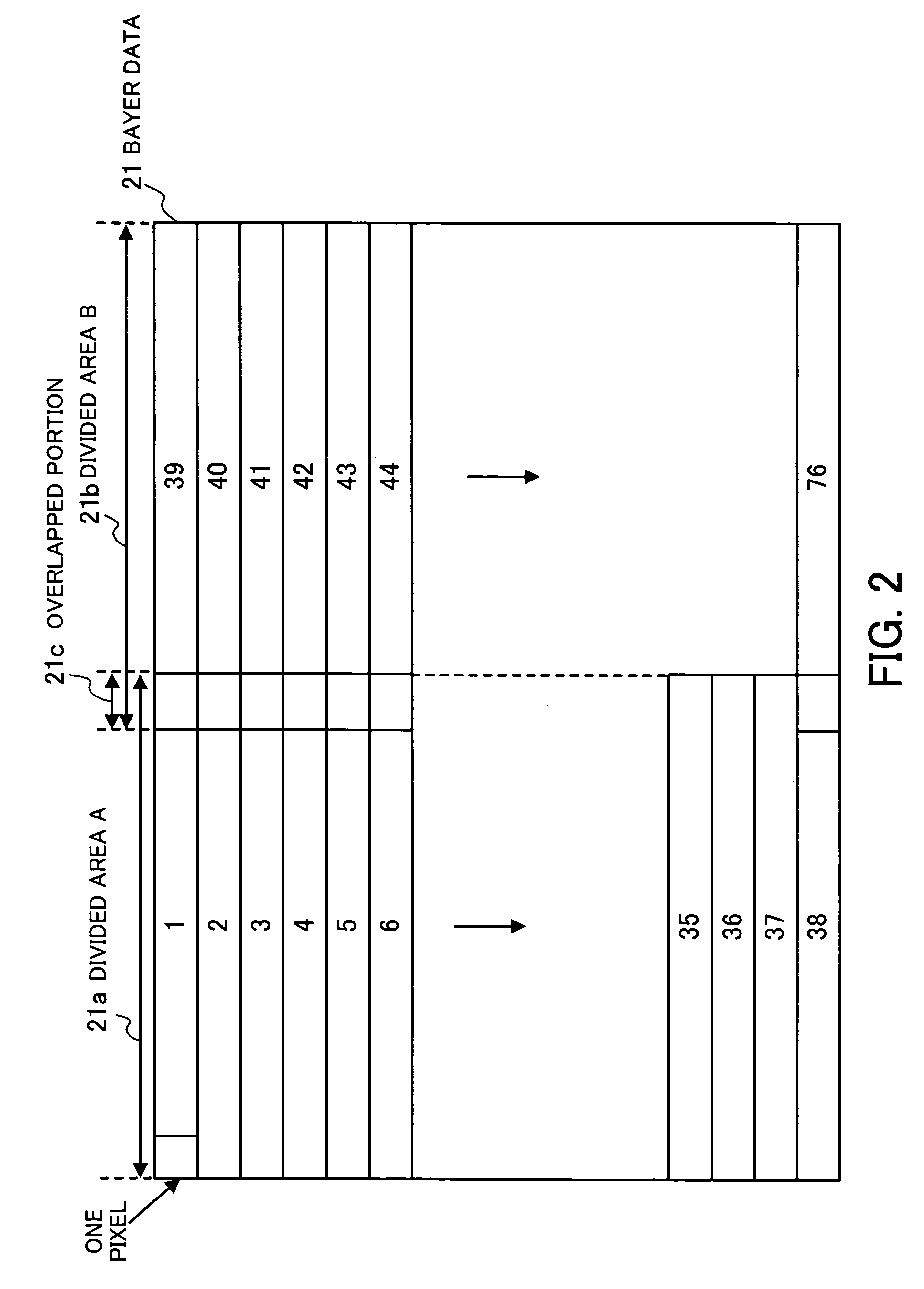

Apparatus and method for processing an image

InactiveUS7583851B2Increase in circuit sizeIncrease processing functionImage memory managementCharacter and pattern recognitionImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

Apparatus and method for processing an image

InactiveUS20060140498A1Improve image processing capabilitiesIncrease in circuit sizeImage memory managementElectric controllersImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

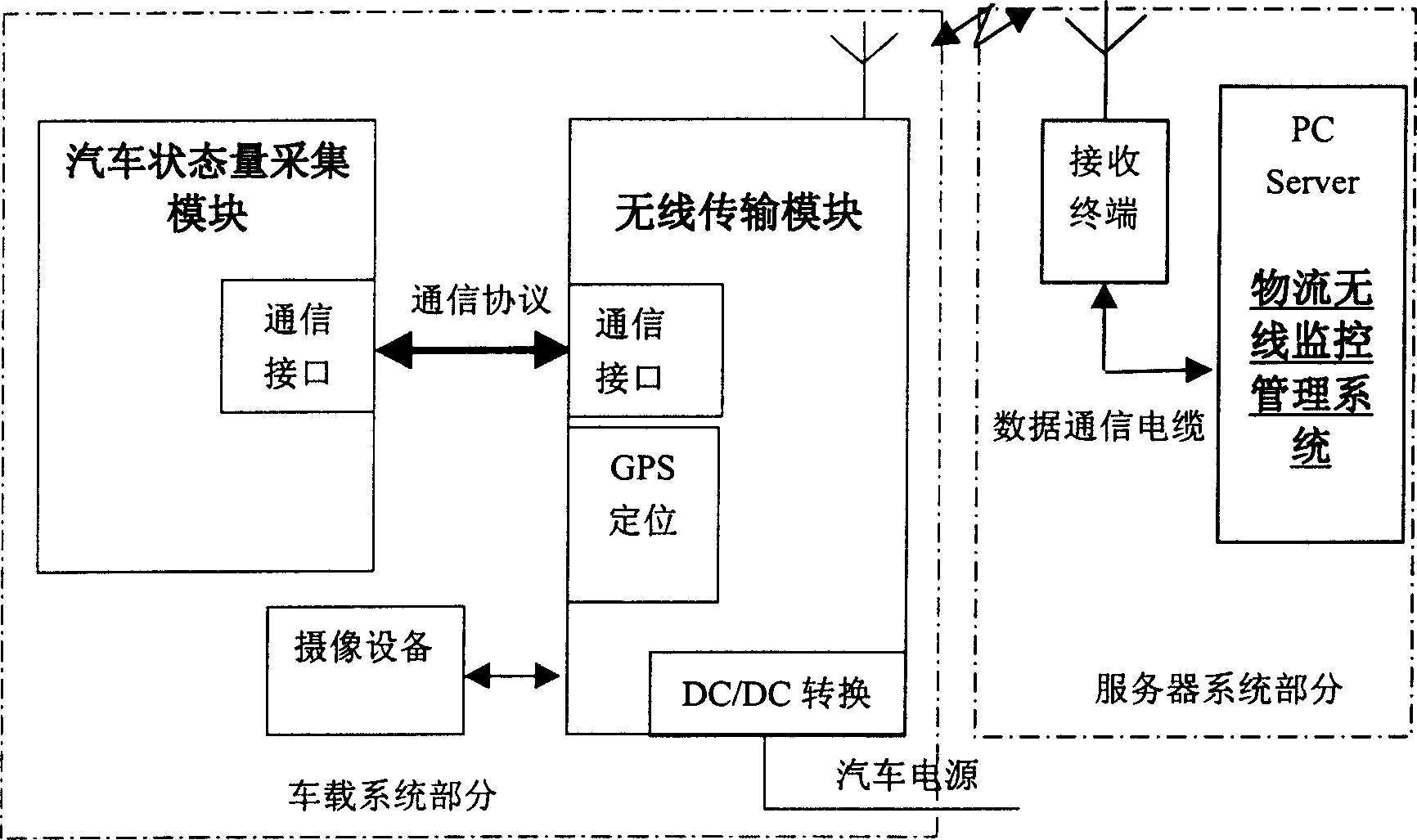

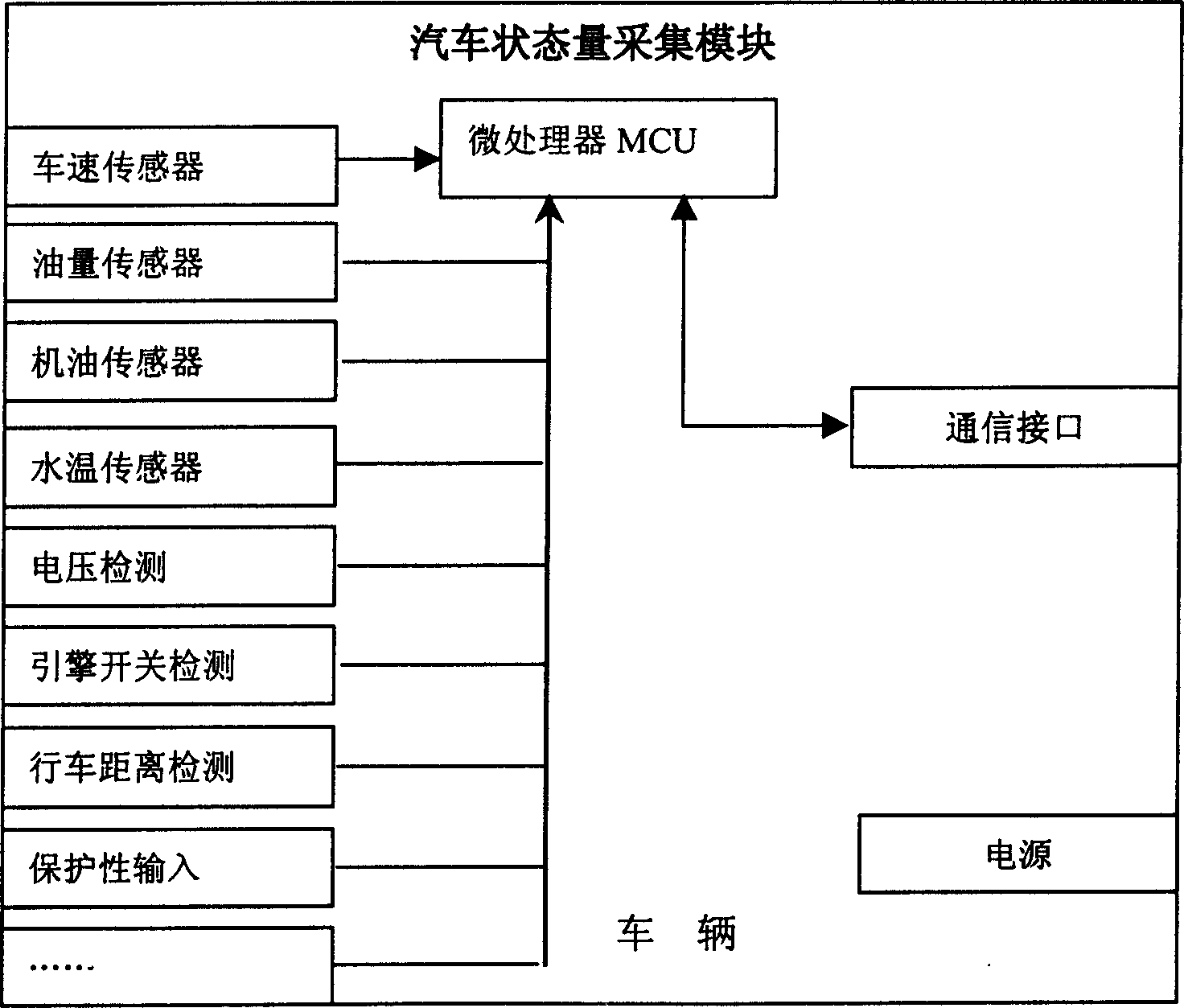

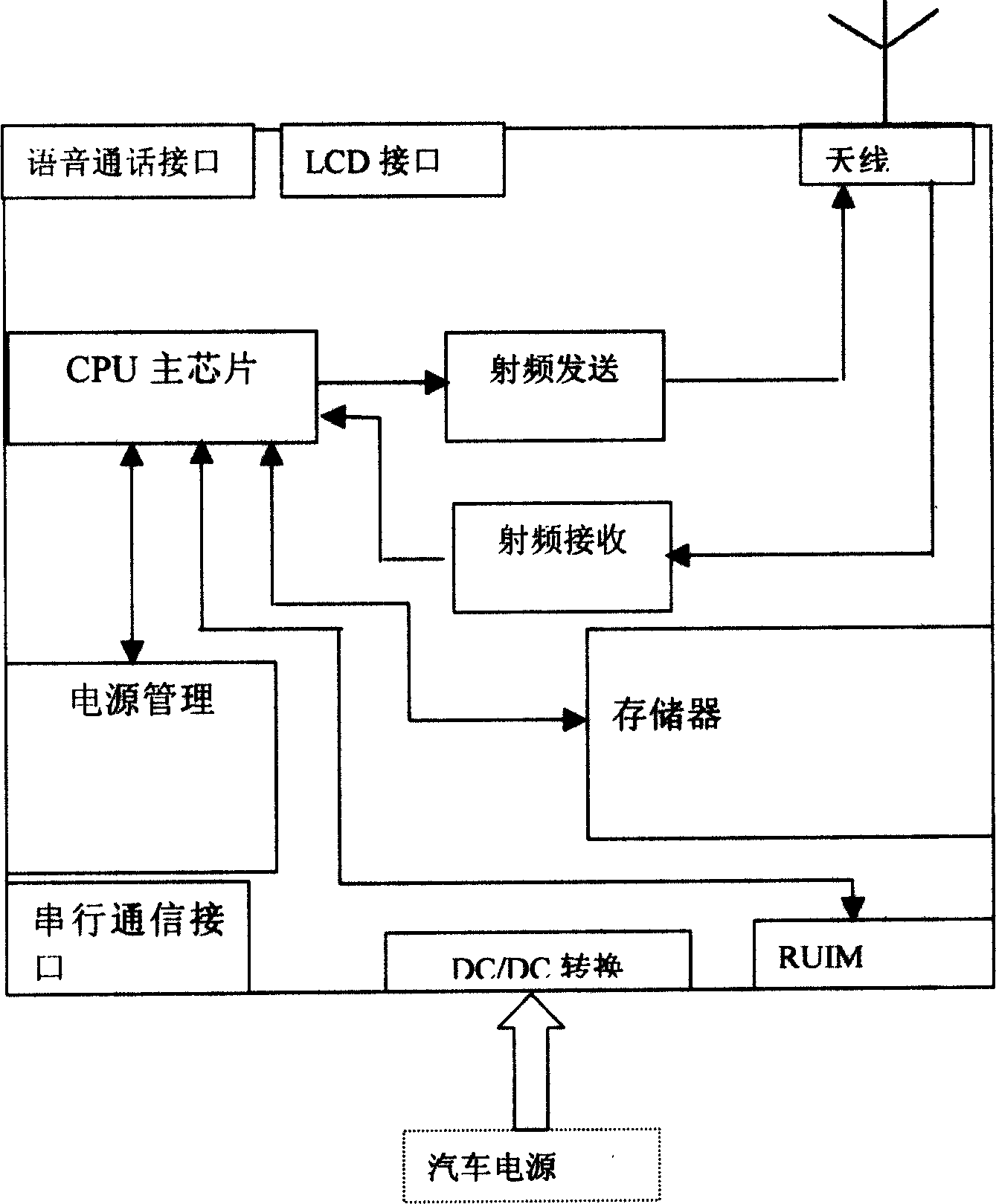

Logistic wireless monitoring management system

InactiveCN1528619AControl Shipping CostsControl Shipping StatusRoad vehicles traffic controlVehicle componentsData informationNetwork Communication Protocols

The invention is a material-flow wireless monitor and management system, including car state quantity collecting module, wireless transmission positioning module and material-flow information management server, where the car state quantity collecting module is added with serial communication interface and connected with the wireless transmission positioning module through the communication protocol, the wireless transmission positioning module transmits the data information through the wireless mobile net to the receiving terminal, which is connected with the material-flow information management server through the data communication cable, the wireless transmission positioning module has functions of positioning, shooting and monitoring, and voice calling. It can provide the needed information for the material-flow management, and better control transport costs of vehicle and cargo state, heightening the management level and efficiency of material-flow company.

Owner:HISENSE +1

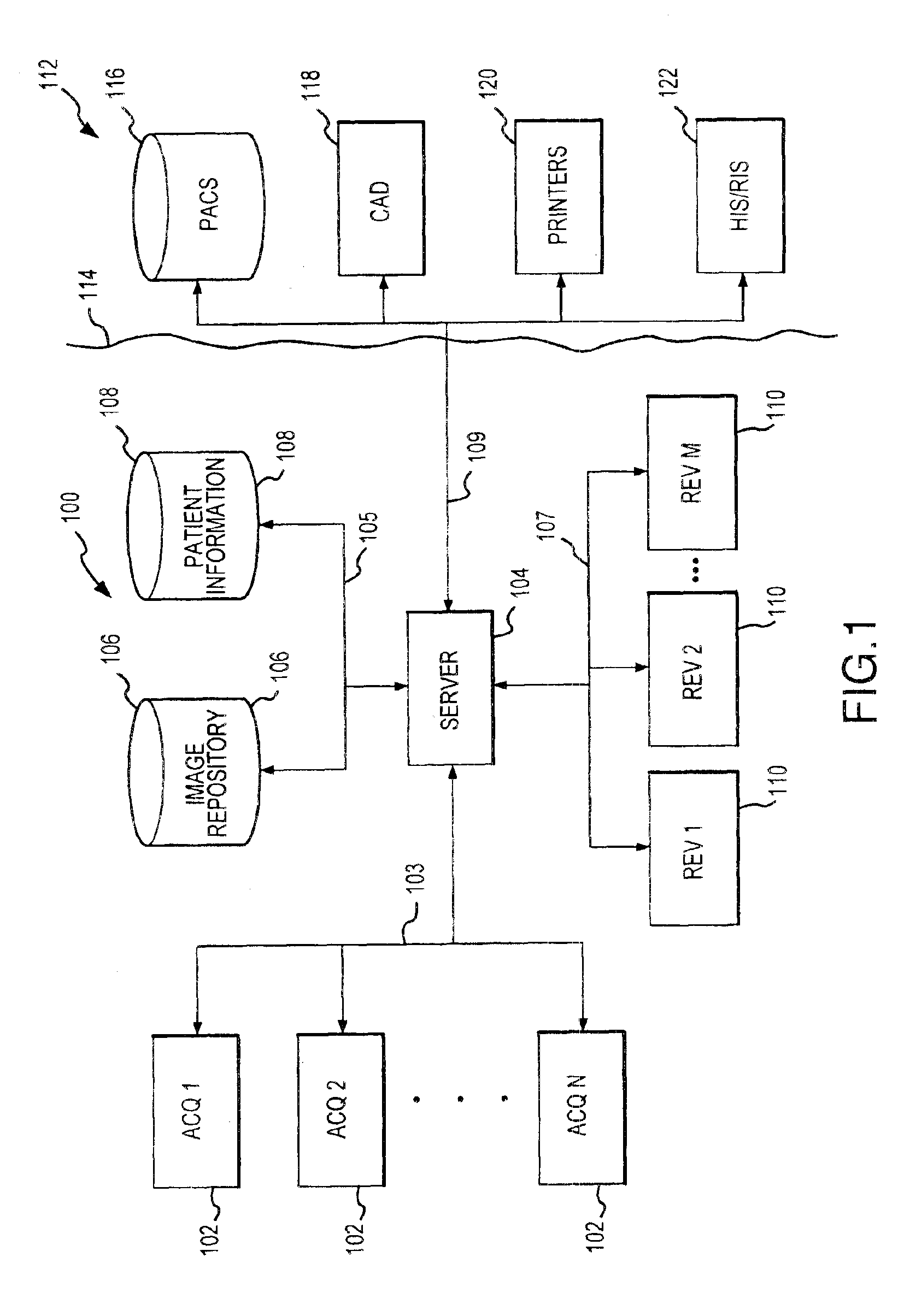

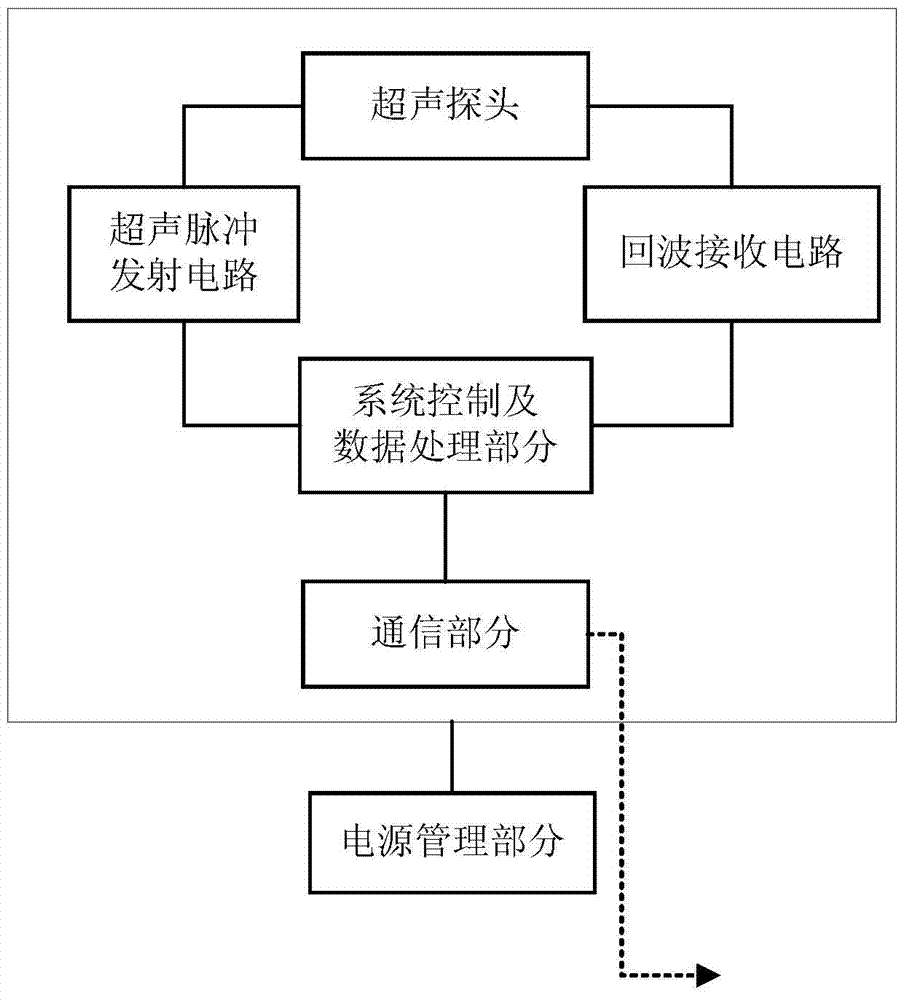

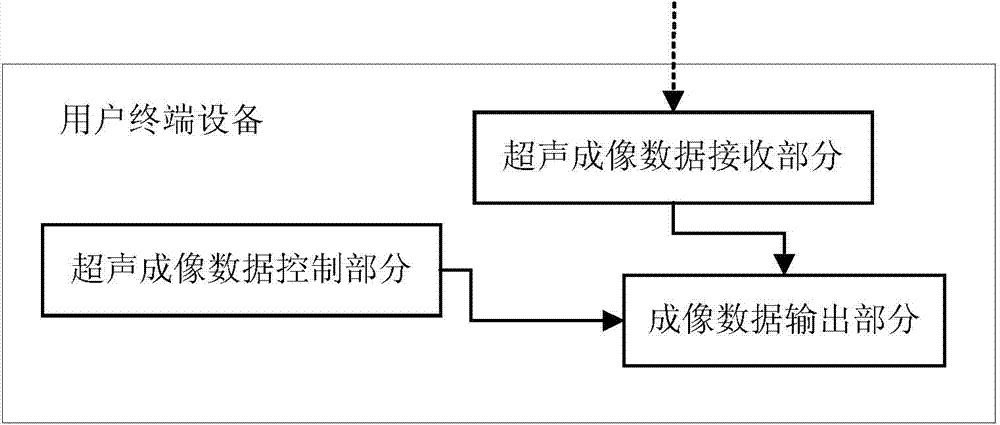

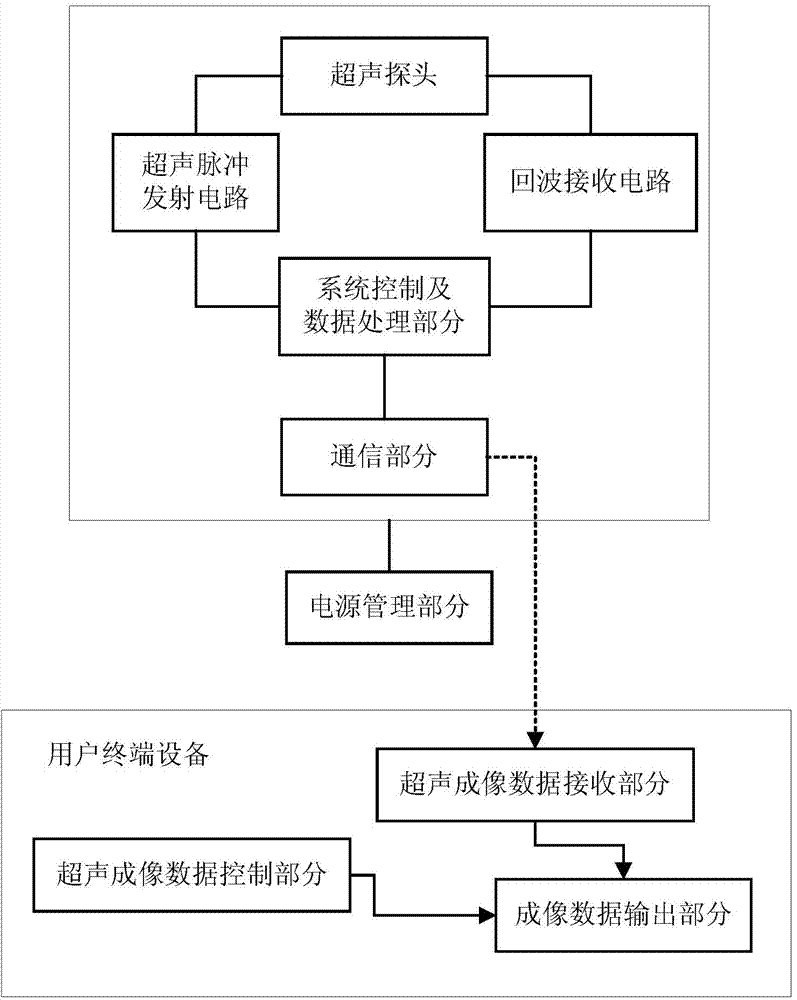

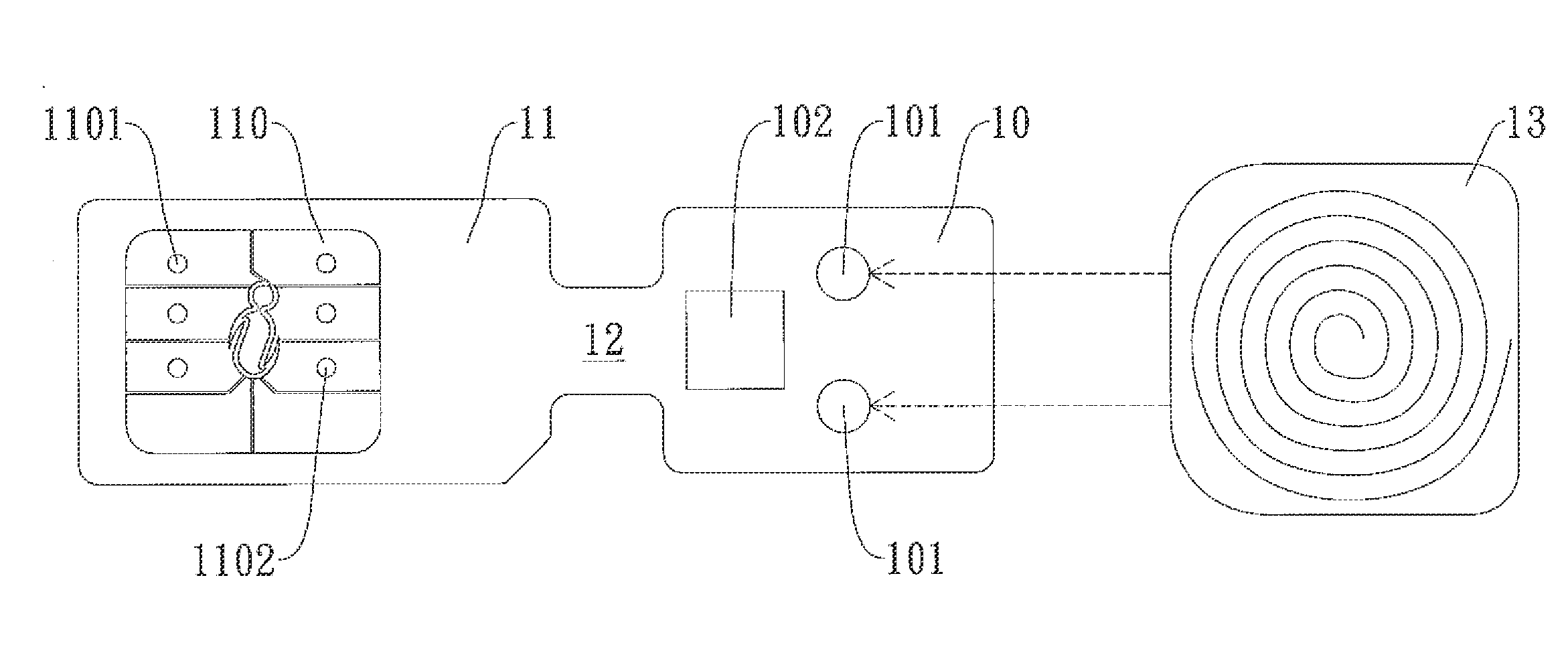

Portable ultrasonic imaging equipment and portable ultrasonic imaging system

InactiveCN104840217AHighly integratedReduce power consumptionInfrasonic diagnosticsSonic diagnosticsThe InternetImaging data

The invention discloses portable ultrasonic imaging equipment and a portable ultrasonic imaging system. The portable ultrasonic imaging equipment comprises an ultrasonic probe, a system control and data processing unit and a communication unit. The ultrasonic probe is used for converting electric signals into ultrasonic waves, emitting the ultrasonic waves, receiving ultrasonic echoes, converting the ultrasonic echoes into electric signals and sending the electric signals to the system control and data processing unit. The system control and data processing unit is used for controlling ultrasonic wave emission and ultrasonic echo reception and performing imaging processing on the electric signals acquired after conversion of the ultrasonic echoes according to an ultrasonic imaging algorithm to acquire imaging data. The communication unit is used for sending the imaging data acquired by the system control and data processing unit to receiving equipment. The receiving equipment is used for performing ultrasonic image displaying on the received imaging data and sending images via the internet. Mobile terminal equipment has a networking communication function of a split type ultrasonic imaging system, so that a user can upgrade and update the networking communication function via a client side conveniently and rapidly; the portable ultrasonic imaging equipment has the advantages of low cost, small size, low power consumption and the like.

Owner:UNIV OF SCI & TECH OF CHINA

Signal Processing Device

InactiveUS20100190528A1Avoid formingPermit usePorous dielectricsCircuit bendability/stretchabilityIntegrated circuitElectricity

The present disclosure provides a signal processing device comprising: a first substrate, one side surface thereof being provided with at least a first contact and a second contact while the other side surface thereof being provided with at least a third contact and a fourth contact, there being an electrical connection between the first and third contacts; a second substrate, one side surface thereof being provided with at least an integrated circuit or an antenna; and a first connecting portion for connecting the first and second substrates; wherein the second and fourth contacts are electrically connected to the integrated circuit or antenna via the first connecting portion.

Owner:PHYTREX TECH CORP

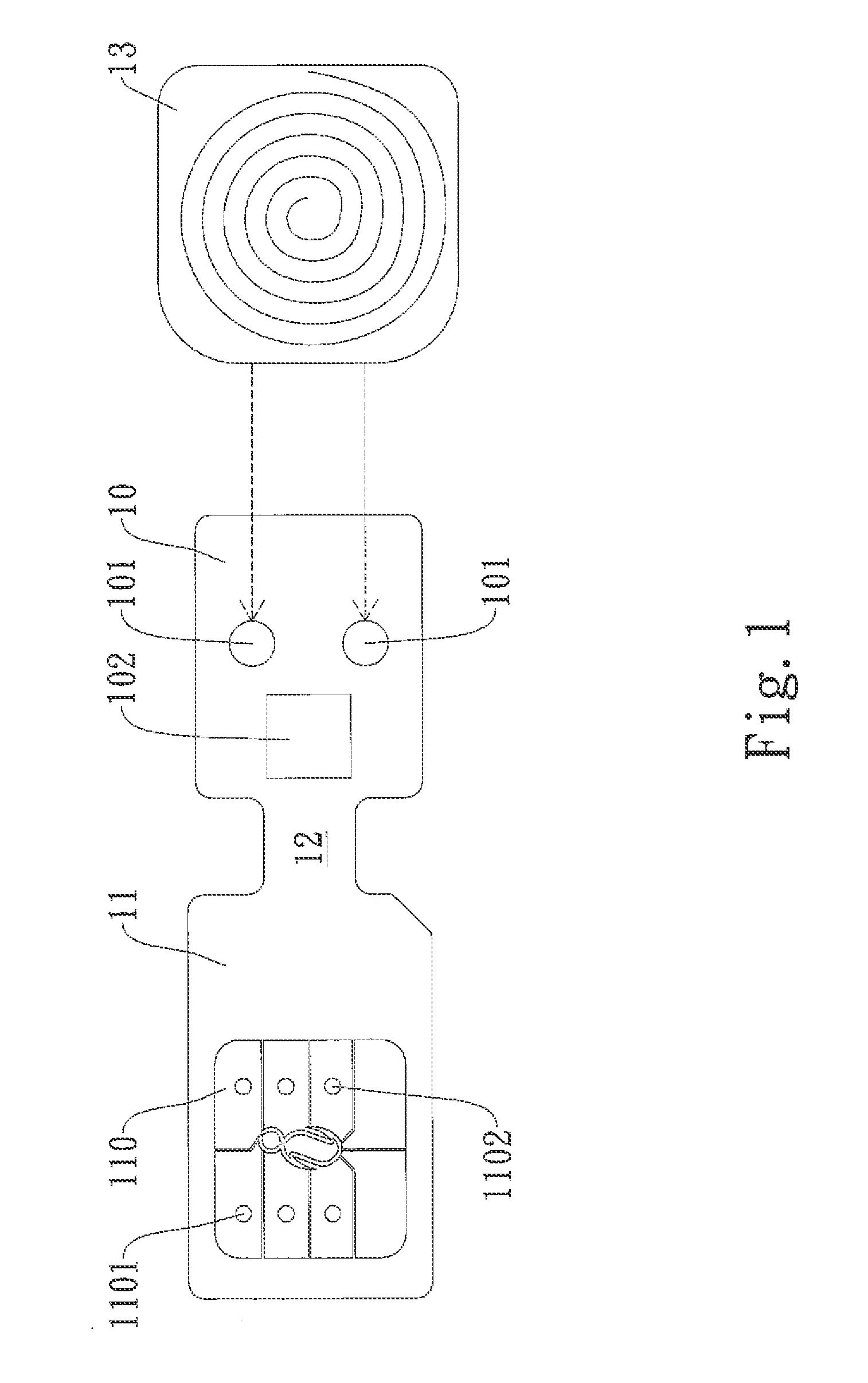

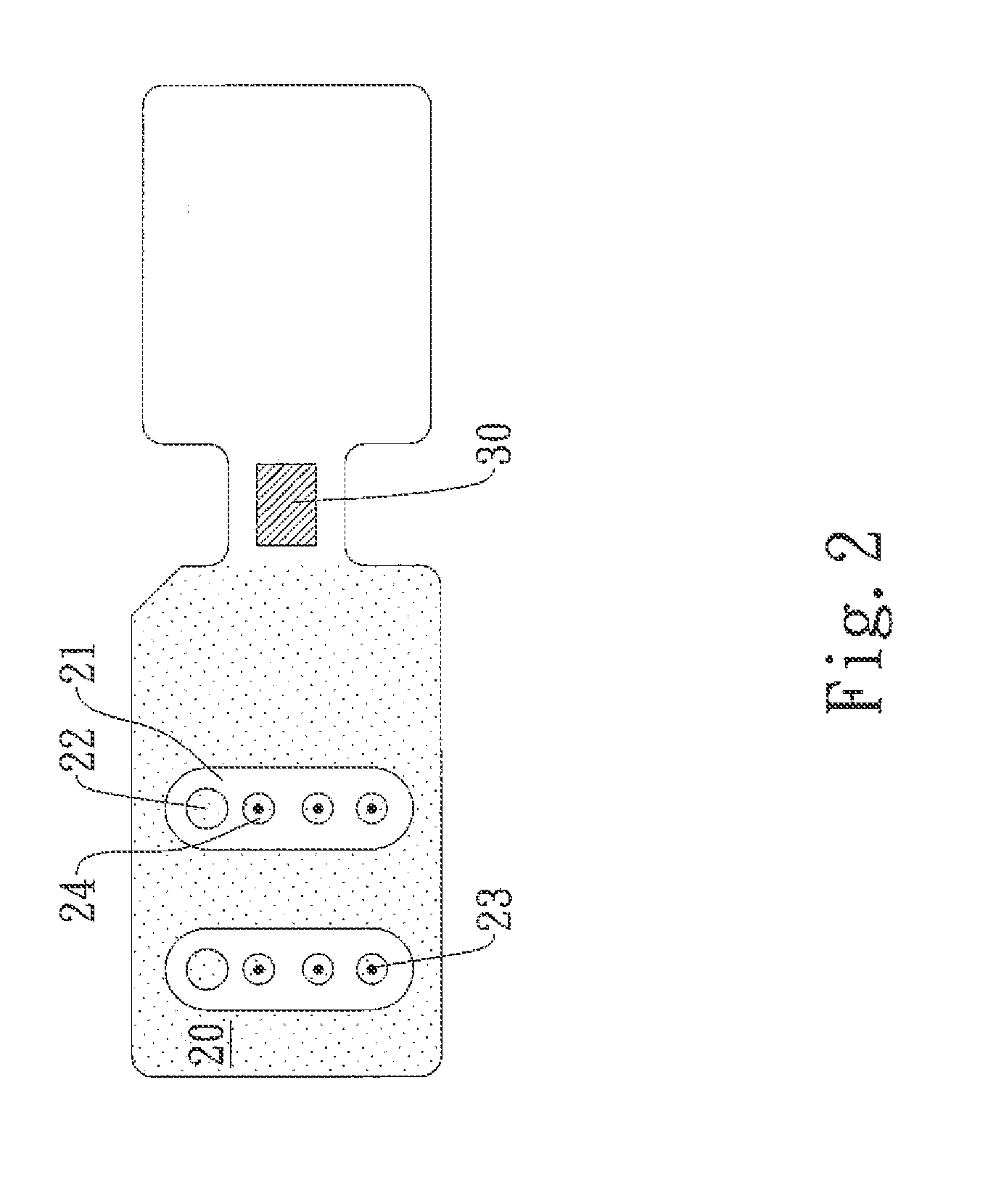

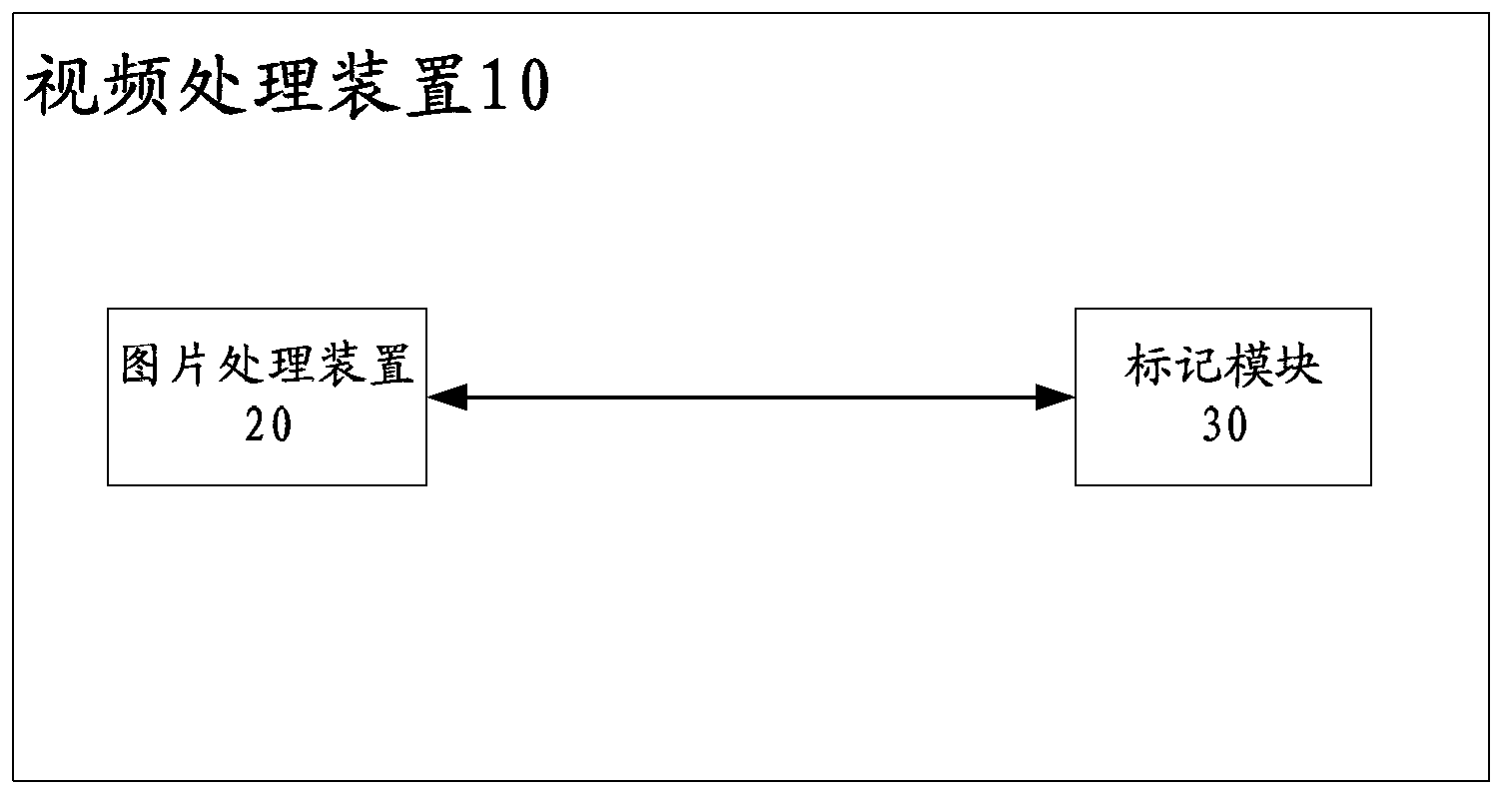

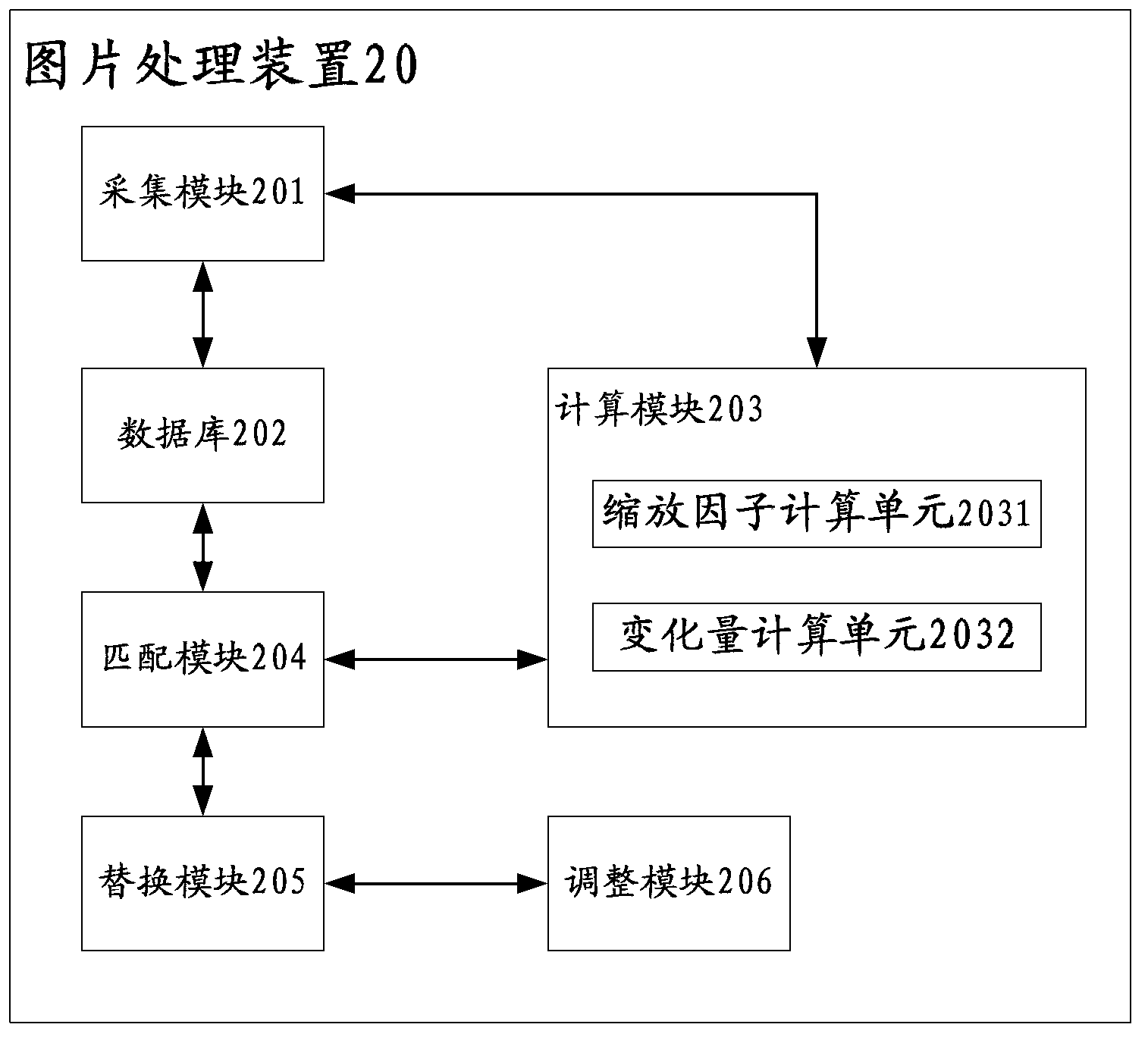

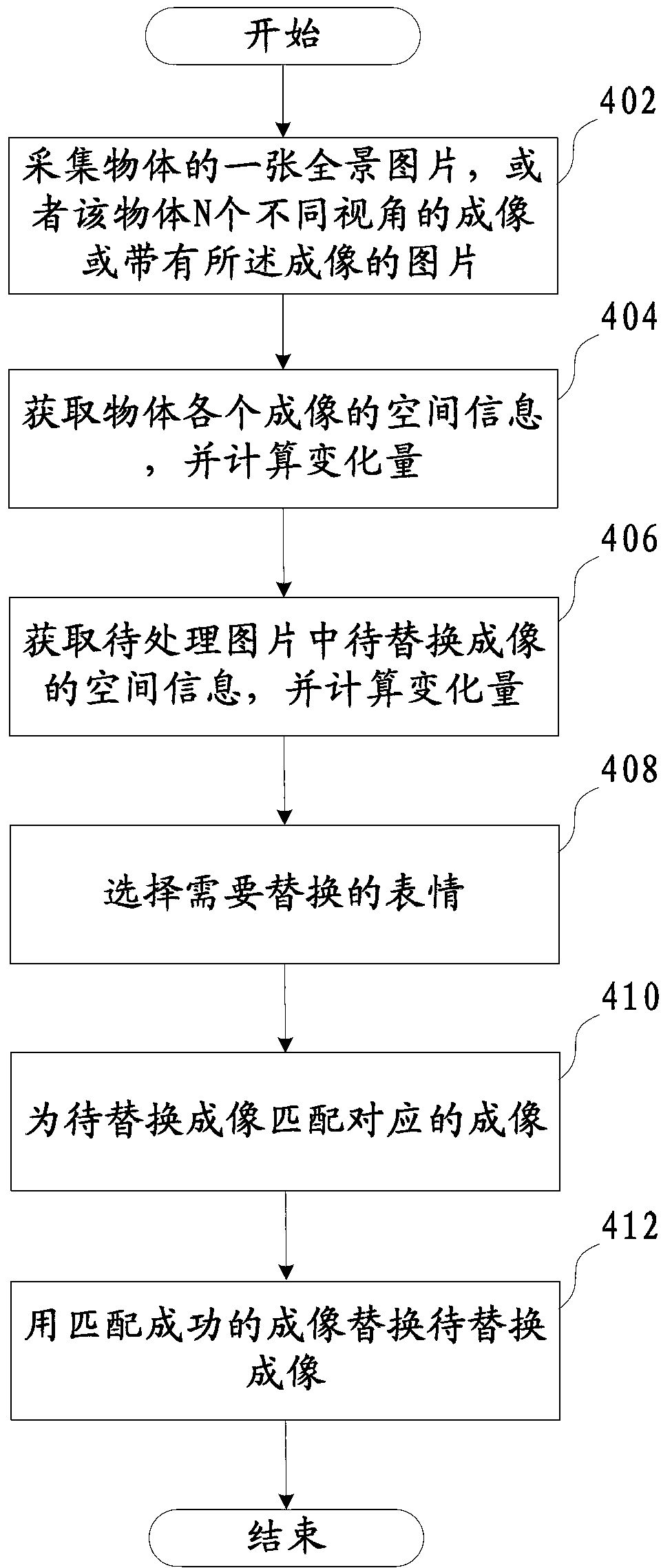

Method and device for picture processing

ActiveCN103258316AFor quick replacementAchieve precise replacementImage analysisGeometric image transformationImage processingData library

The invention discloses a method for picture processing and a device for picture processing. A plurality of images or pictures with images at different perspectives of the same object are collected and then stored in a database in advance; variation quantity of the space information of the images to be replaced and variation quantity of the standard space information of the standard images are calculated; the corresponding images are matched so that the images to be replaced can be replaced. Appointed objects in each picture or each video can be replaced rapidly. In addition, calculation of the variation quantity of the space information of the images to be displaced is added, so that the replaced images are more close to the images to be replaced and the accurate replacement of the appointed objects is achieved. Meanwhile, the requirement for replacing an original expression by other expressions by a user is satisfied through the arrangement of different expression parameters, so that the diversity of the replacement of the appointed objects is improved, the degree of user experience is further improved, and the function of processing the videos and the pictures is expanded.

Owner:DONGGUAN YULONG COMM TECH +1

Support vector machines processing system

ActiveUS7490071B2Alleviate challengeImprove usabilityDigital data processing detailsDigital computer detailsSupport vector machineAlgorithm

An implementation of SVM functionality improves efficiency, time consumption, and data security, reduces the parameter tuning challenges presented to the inexperienced user, and reduces the computational costs of building SVM models. A system for support vector machine processing comprises data stored in the system, a client application programming interface operable to provide an interface to client software, a build unit operable to build a support vector machine model on at least a portion of the data stored in the system, based on a plurality of model-building parameters, a parameter estimation unit operable to estimate values for at least some of the model-building parameters, and an apply unit operable to apply the support vector machine model using the data stored in the system.

Owner:ORACLE INT CORP

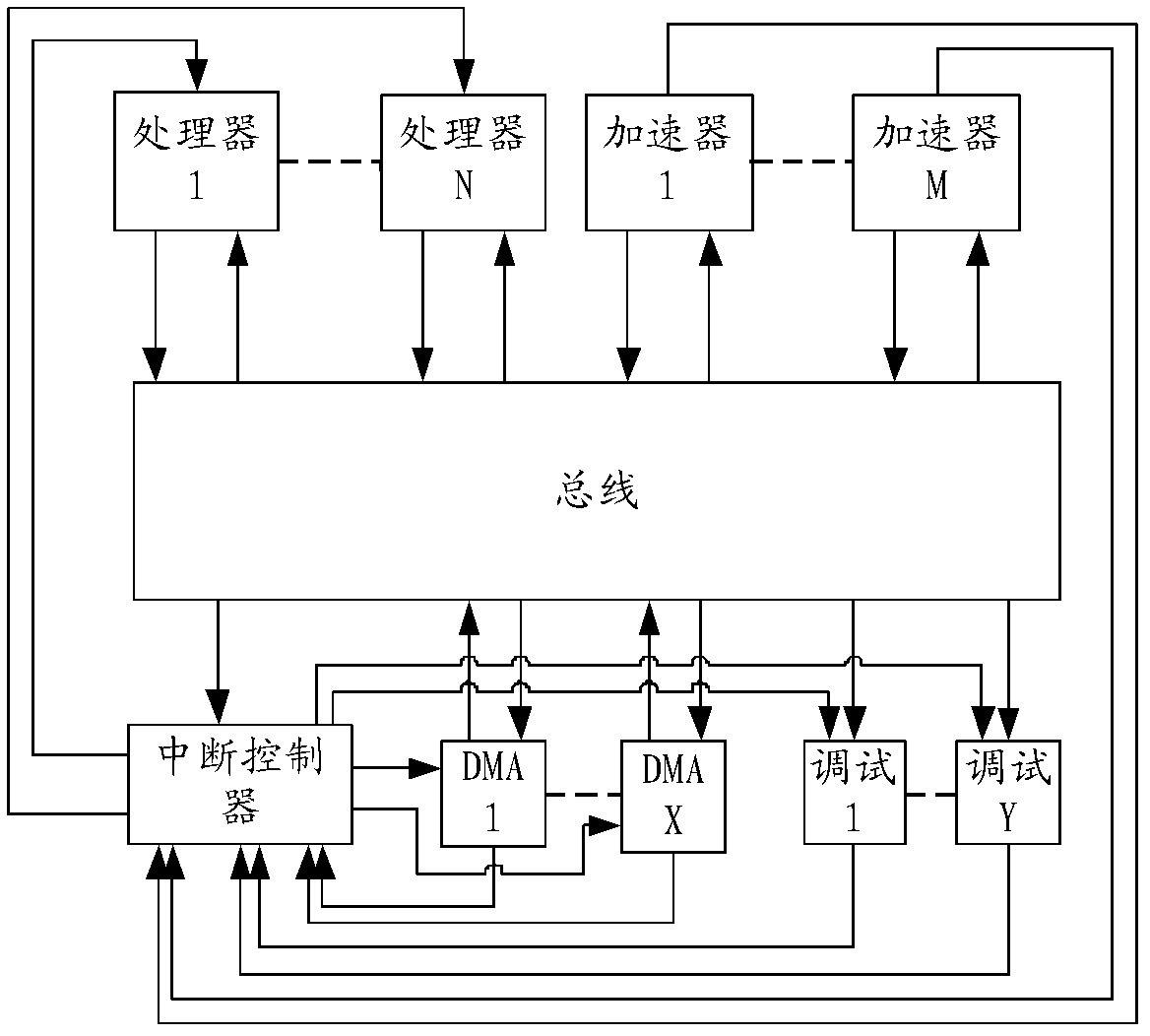

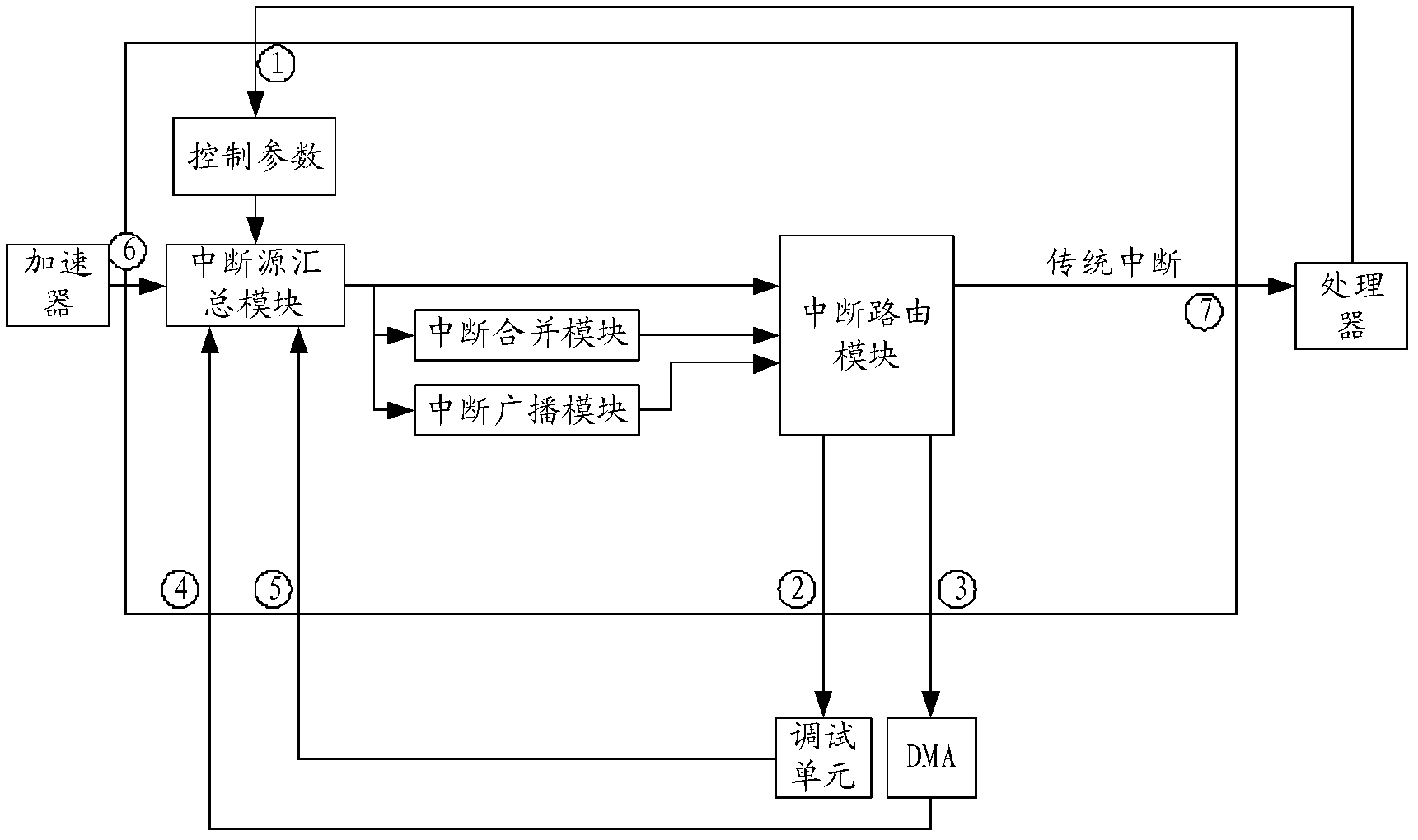

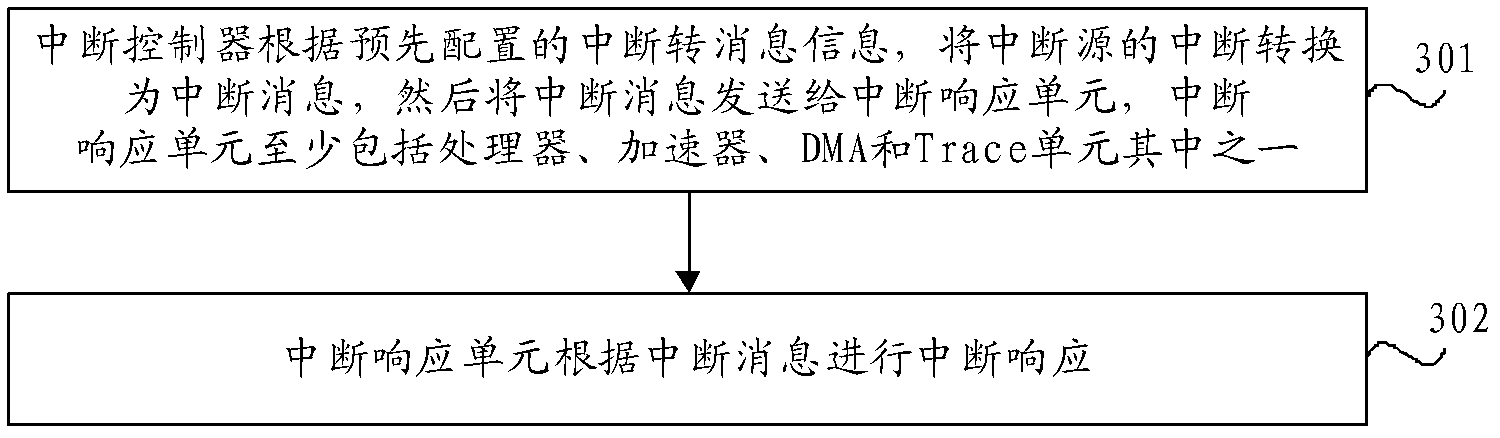

Interrupt handling method, interrupt controller and processor

InactiveCN102662889AIncrease processing functionReduce overheadElectric digital data processingDirect memory accessEmbedded system

The invention provides an interrupt handling method, an interrupt controller and a processor. The interrupt handling method includes that the interrupt controller converts interruption of an interrupt source into an interrupt message according to interrupt conversion message information, then the interrupt message is sent to an interrupt response unit, and the interrupt response unit at least comprises one of the processor, an accelerator, a direct memory access (DMA) and a trace unit. The interrupt response unit conducts interrupt response according to the interrupt message. The interrupt controller outputs the interrupt message to all interrupt response units through an interrupt conversion message, software overhead consumed by the interrupt response is reduced.

Owner:HUAWEI TECH CO LTD

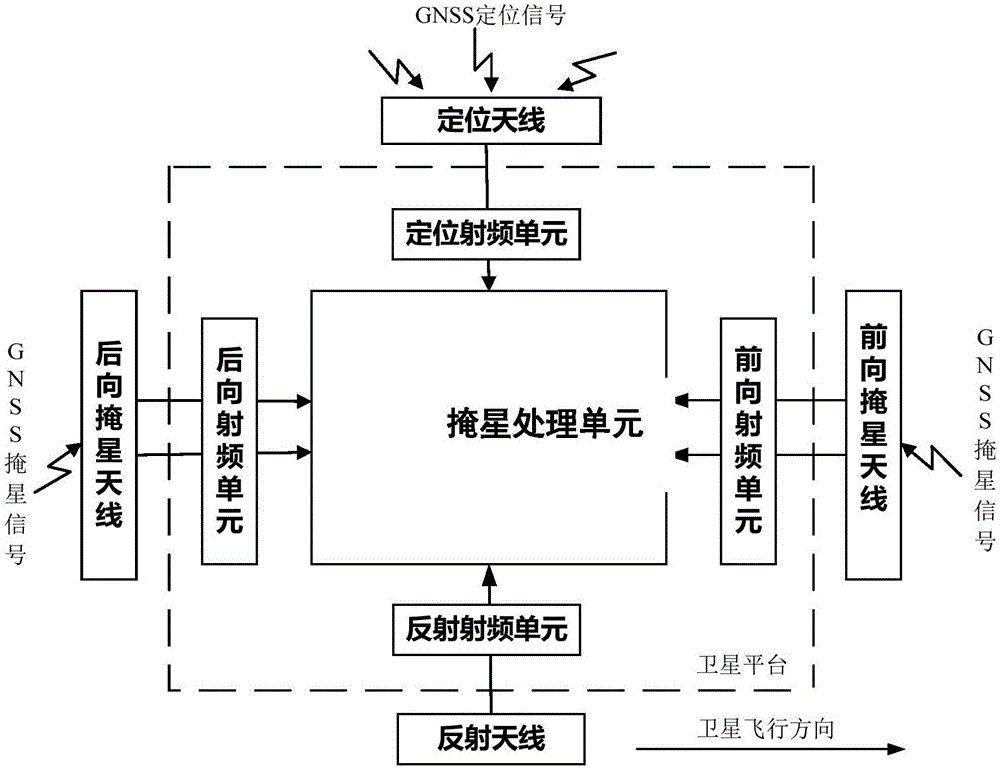

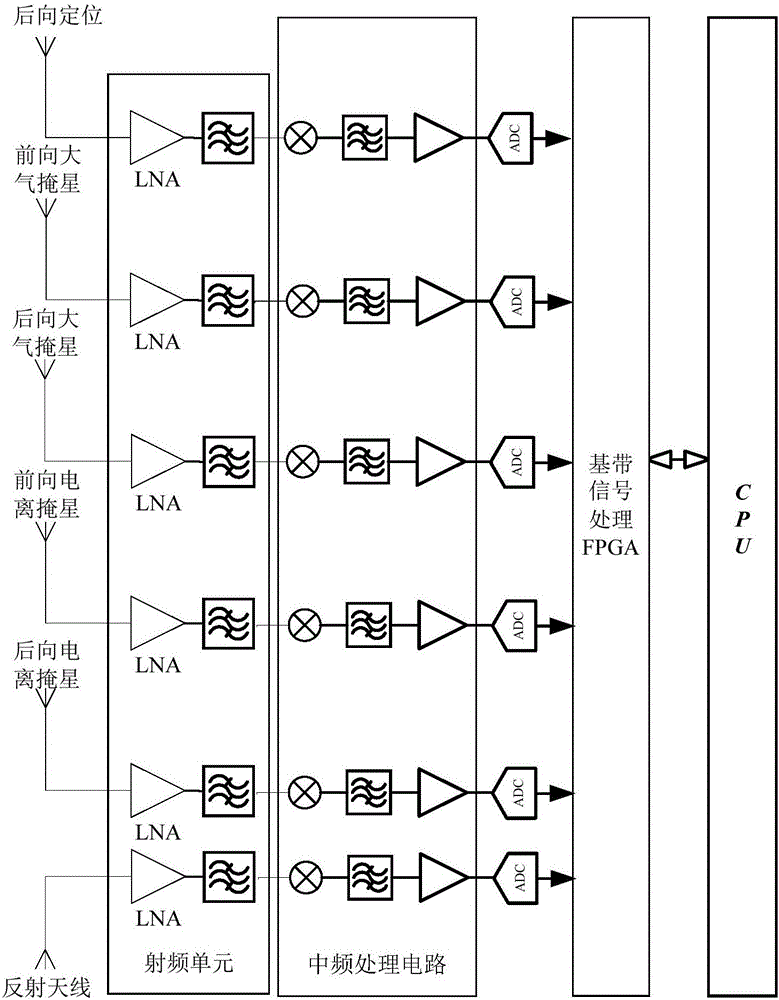

GNSS wireless occultation detecting instrument compatible with GNSS-R detection technology

InactiveCN106291560ASave space and energyHigh precisionSatellite radio beaconingRadio wave reradiation/reflectionPhysicsVIT signals

The invention provides a GNSS wireless occultation detecting instrument compatible with GNSS-R detection technology. The detecting instrument comprises a positioning antenna, an occultation antenna, a reflecting antenna, a radio frequency unit and an occultation processing unit, wherein the radio frequency unit is used for carrying out amplification and radio frequency filtration processing on signals received by the positioning antenna, the reflecting antenna, atmospheric occultation antenna and ionospheric occultation antenna, and inputting the generated radio frequency signals to the occultation processing unit; the occultation processing unit is used for GNSS satellite capturing and tracking through the received radio frequency signals, and calculating by utilizing the tracked signals to obtain the satellite position and speed information, carrier phase and amplitude of GNSS occultation signals, and two-dimensional delay Doppler graph of GNSS-R reflecting signals. The GNSS wireless occultation detecting instrument can achieve the purpose that GNSS occultation detection and GNSS-R sensing detection are implemented simultaneously by the same load and the same satellite.

Owner:NAT SPACE SCI CENT CAS

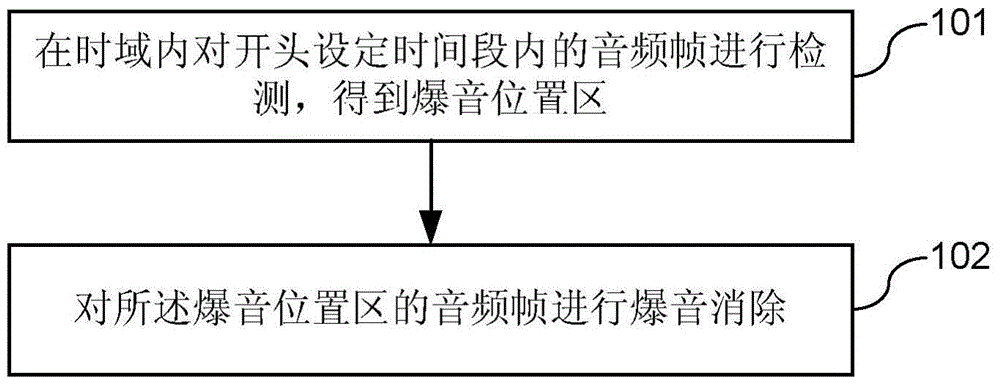

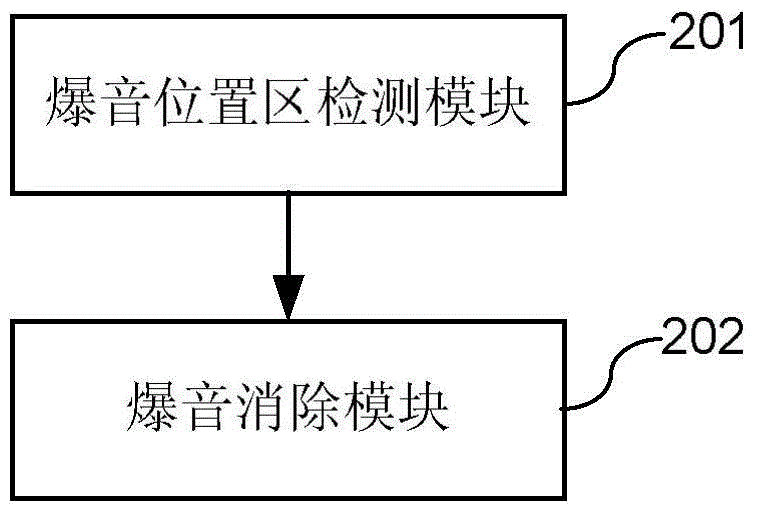

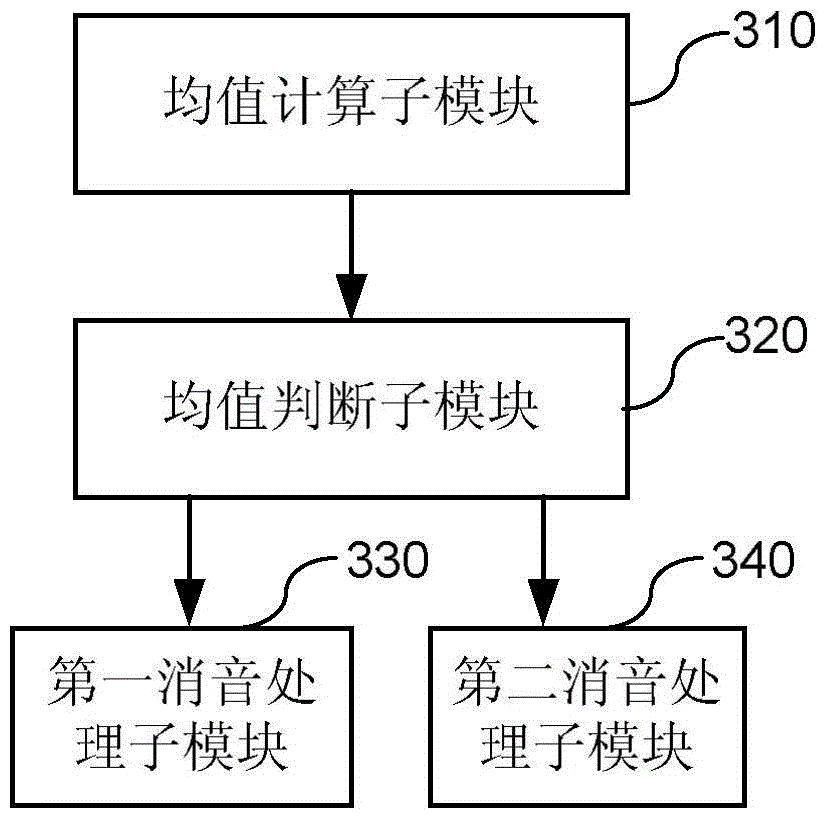

Elimination method and device of audio beginning sonic boom

ActiveCN105118520AEliminate the opening popImprove playback qualitySpeech recognitionFrequency response correctionTime domainTime segment

The embodiment of the present invention discloses an elimination method and device of an audio beginning sonic boom, wherein the method comprises the steps of detecting an audio frame within a beginning set time quantum in a time domain to obtain a sonic boom position area; carrying out the sonic boom elimination on the audio frame in the sonic boom position area. According o the technical scheme of the embodiment of the present invention, the playing quality of the audio data can be improved, and a processing function of a server system is enhanced.

Owner:TENCENT TECH (SHENZHEN) CO LTD

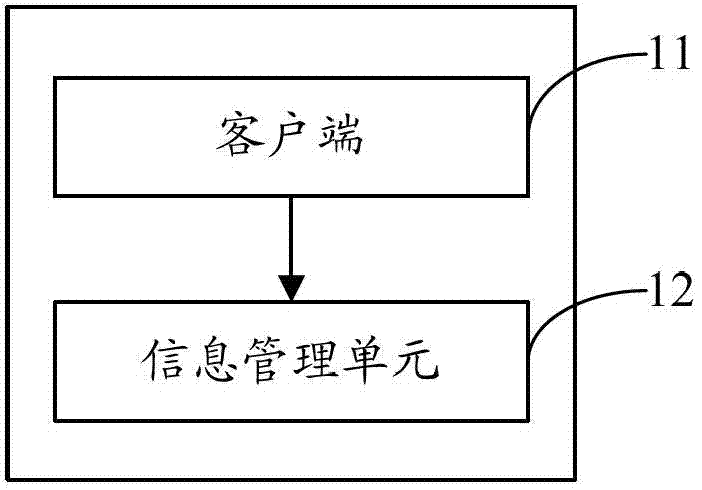

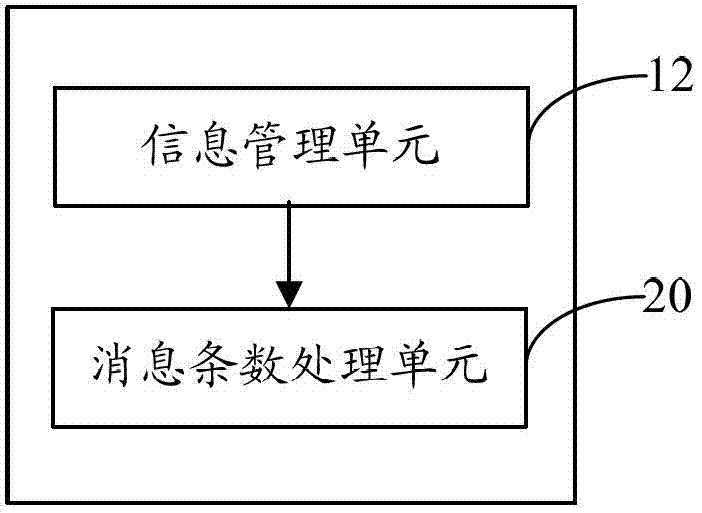

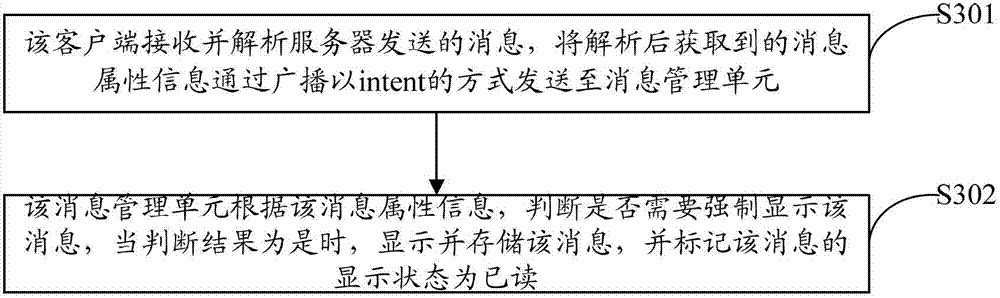

Television and message processing method and system

ActiveCN102811379AUnified managementIncrease processing functionSelective content distributionData switching networksComputer hardwareManagement unit

The invention is applied to the field of televisions, and provides a television, a message processing method and a message processing system. The television comprises a client and an information management unit, wherein the client is used for receiving and resolving a message which is transmitted by a server, and transmitting message attribute information which is acquired by resolving the message to the message management unit by broadcasting in an intent way; and the message management unit is used for judging whether the message is required to be forcedly displayed according to the message attribute information, when a judgment result is that the message is required to be forcedly displayed, the message is displayed and stored, and the state of the message is marked as read. According to the television, the method and the system, the message is received and resolved by the client, and is stored and checked by the message management unit, so that the television can have functions such as unified management of the message which is pushed by the server.

Owner:TCL CORPORATION

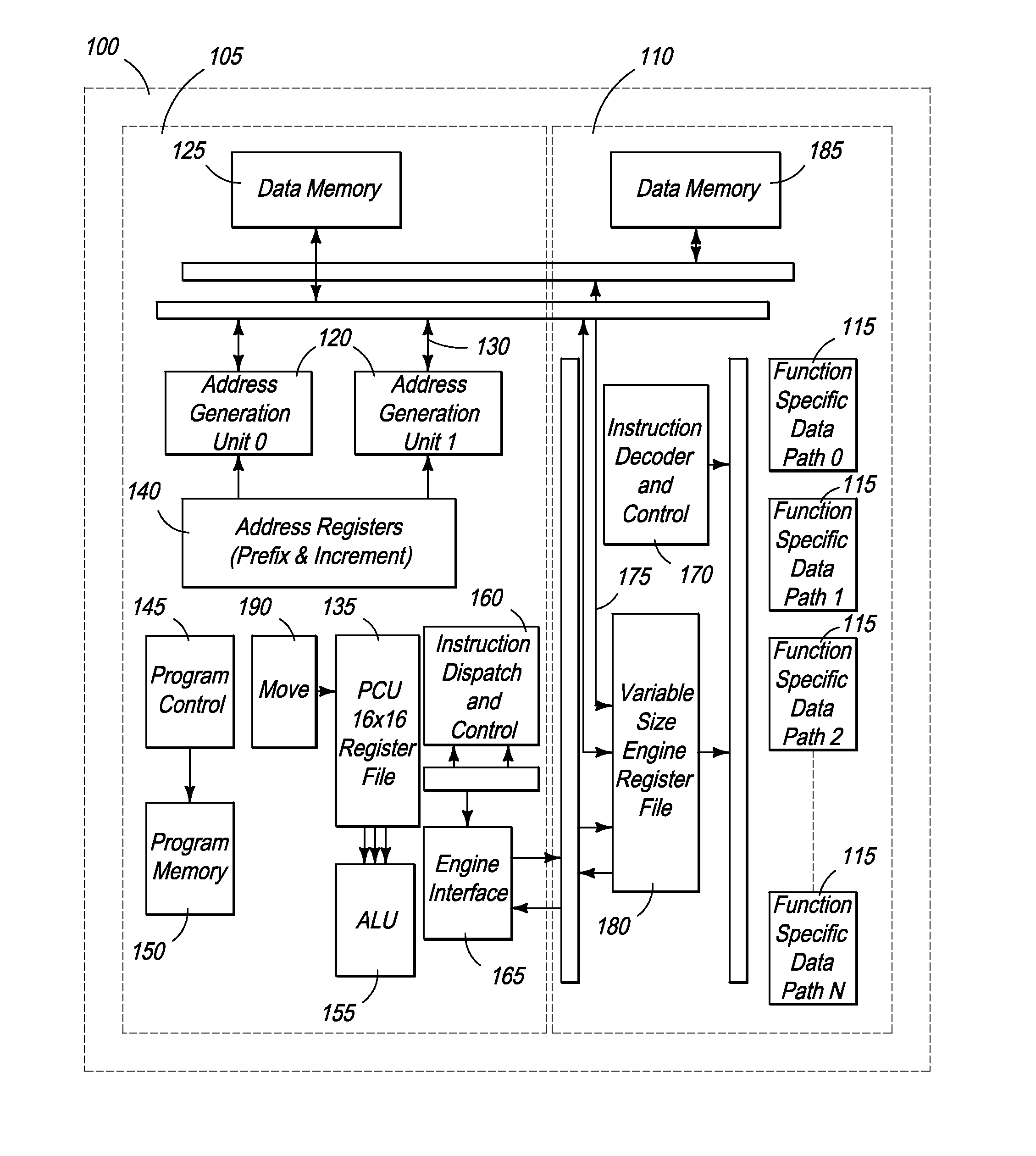

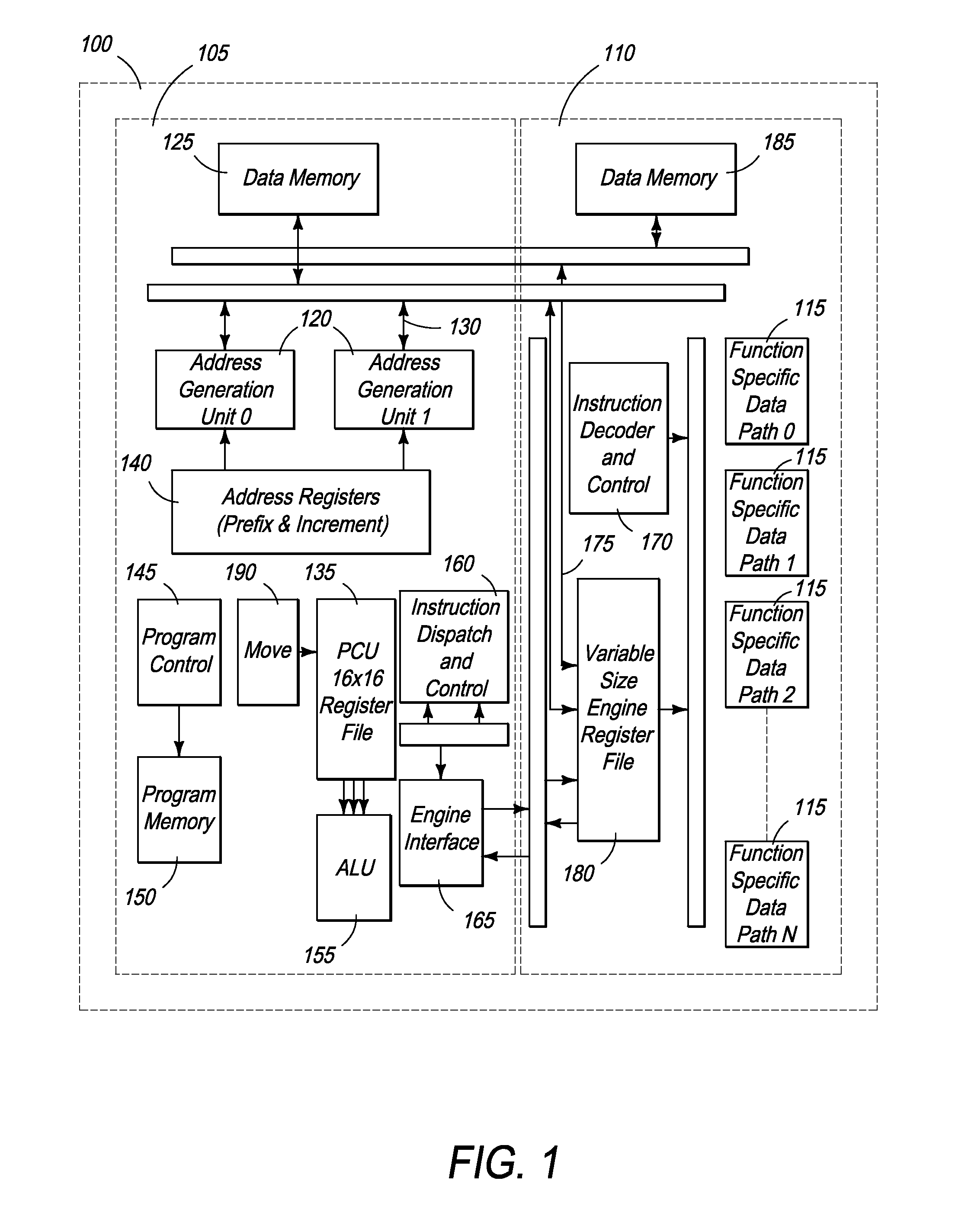

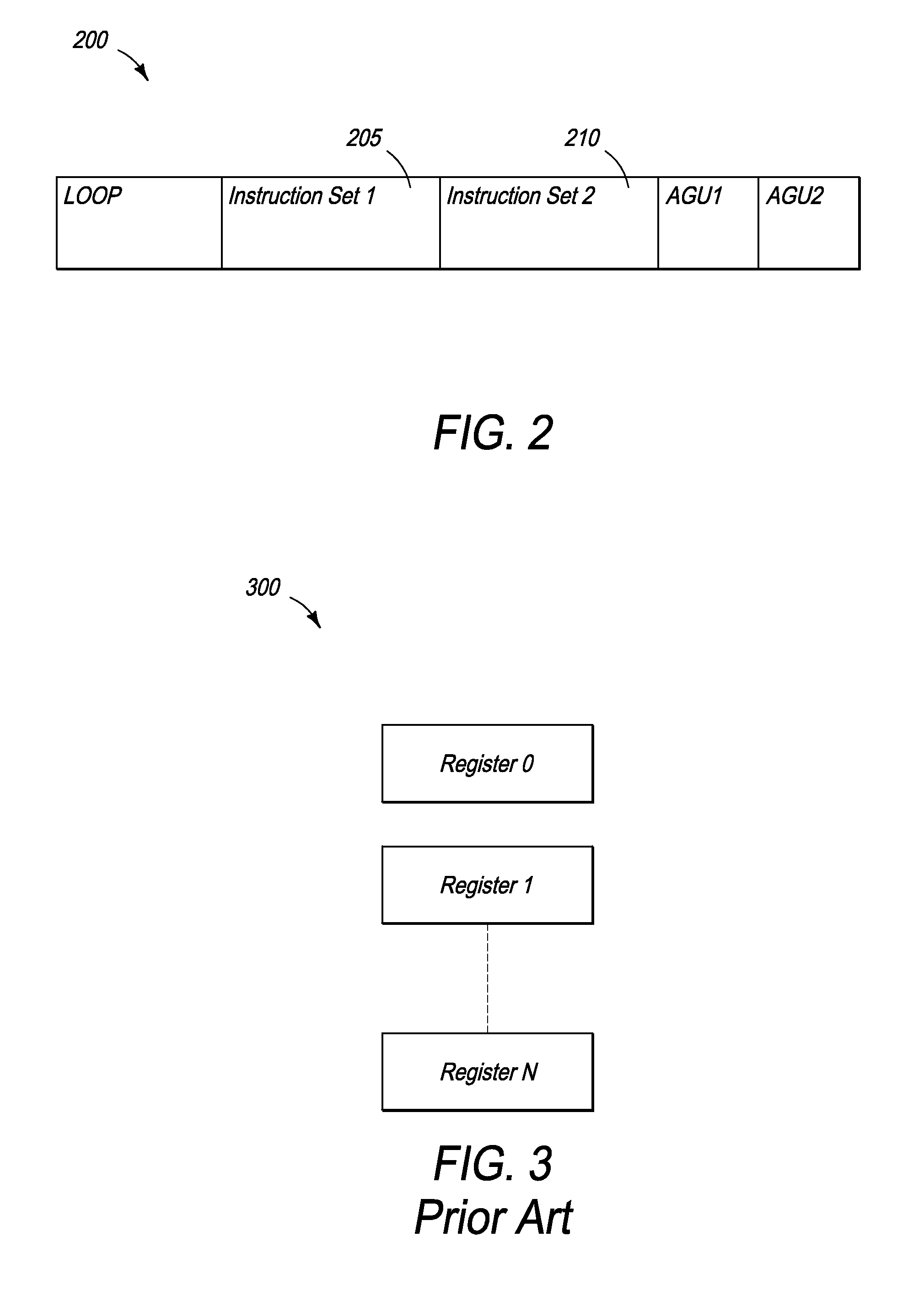

Front End Processor with Extendable Data Path

InactiveUS20100321579A1Easy to processIncrease processing functionTelevision system detailsProgram control using wired connectionsData memoryDiscrete cosine transform

The present specification discloses a processing architecture that has multiple levels of parallelism and is highly configurable, yet optimized for media processing. At the highest level, the architecture is structured to enable each processor, which is dedicated to a specific media processing function, to operate substantially in parallel. In addition to processor-level parallelism, each processing unit can operate on multiple words in parallel, rather than just a single word per clock cycle. Moreover, at the instruction level, the control data memory, data memory, and function specific dath paths can be controlled all within the same clock cycle. Additionally, the processor has multiple layers of configurability, with the extendable data path of the processor being capable of being configured to perform specific processing functions, such as entropy encoding, discrete cosine transform (DCT), inverse discrete cosine transform (IDCT), motion compensation, motion estimation, de-blocking filter, de-interlacing, de-noising, quantization, and dequantization.

Owner:QUARTICS

Thermoplastic elastomer surface treating agent

The thermoplastic elastomer surface treating agent consists of toluene 50-65 weight portions, butanone 5 -12 weight portions, ethyl acetate 5-12 weight portions, natural rubber 6-9 weight portions, chlorinated polypropylene 1-2.5 weight portions, methyl methacrylate 1-3 weight portions, vinyl acetate )1-3 weight portions, benzoyl peroxide 0.05-0.1 weight portion, and antioxidant BHP 0.05-0.1 weight portion. The present invention has practicability, high stability, powerful adhesion force and other advantages.

Owner:GOOD CHEM SCI & TECH

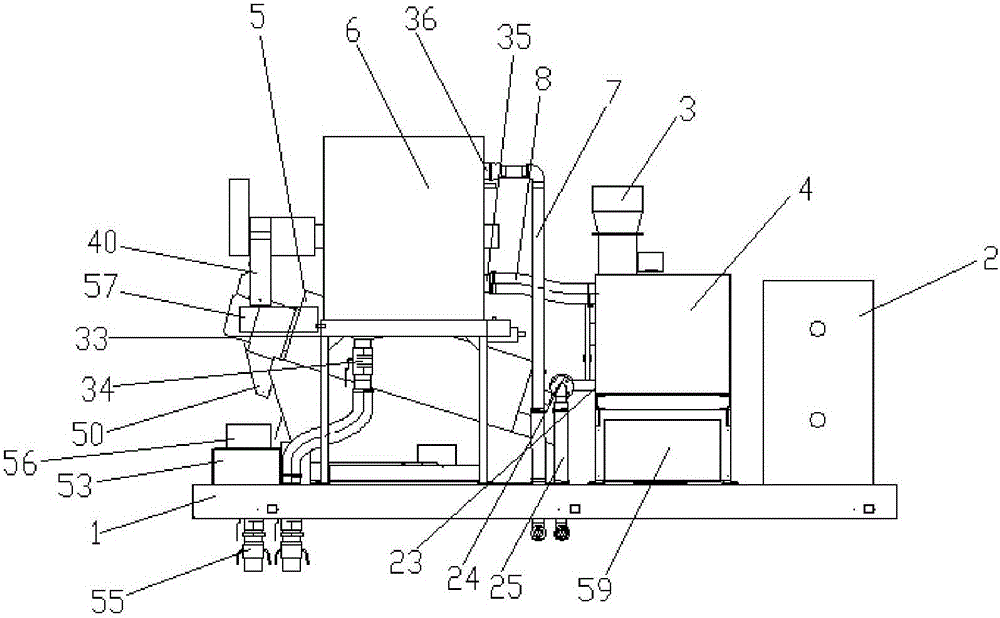

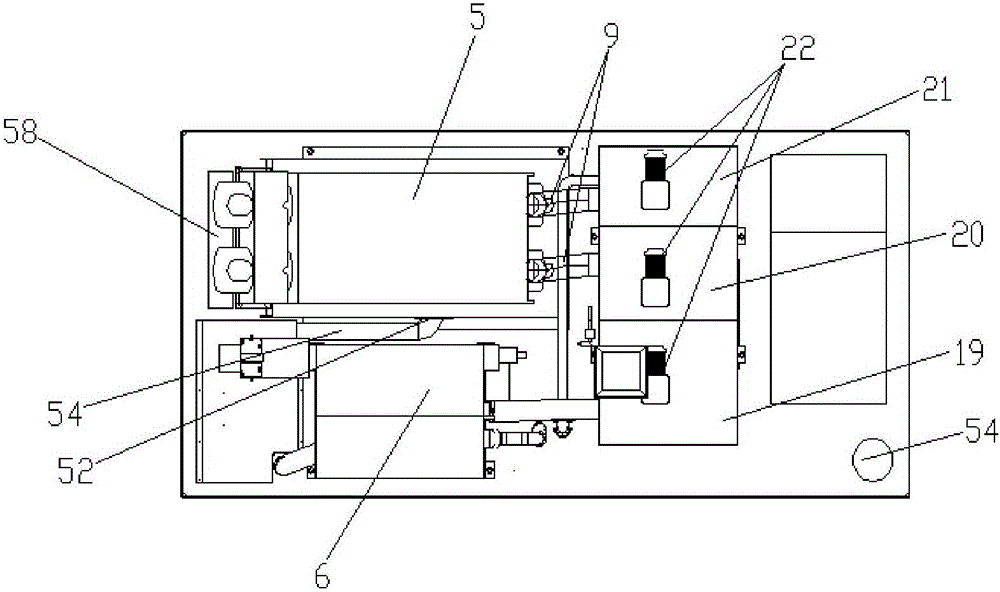

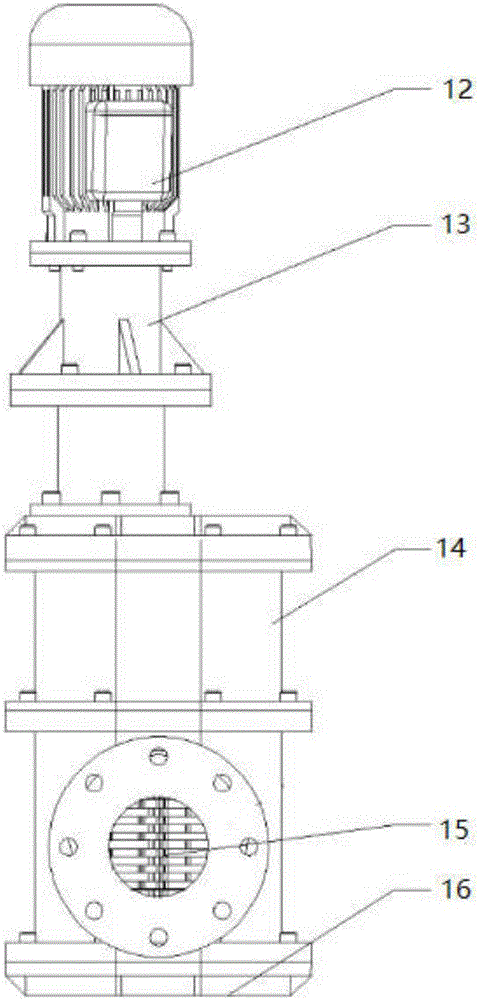

Multifunctional sludge, sewage and dirt treatment machine of septic tank

InactiveCN106430741AImprove self-priming performanceProtectSludge treatment by de-watering/drying/thickeningTreatment involving filtrationSludgeSlag

The invention relates to a multifunctional sludge, sewage and dirt treatment machine of a septic tank. The sludge, sewage and dirt treatment machine comprises a pumping system, a dispensing system group, a solid-liquid separation system, a base I, a plurality of connecting pipelines and a plurality of valves. The multifunctional sludge and sewage treatment machine integrates the dirt collection, crushing, slag removal, filtering, dehydration and packaging, can automatically classify and treat any domestic sewage and dirt, sludge and sewage of the septic tank into slag, clean water and recyclable organic manure raw materials (sludge), and is a movable environment-friendly and ecological treatment factory capable of intensively treating various domestic sewage, excrement dirt, sludge and sewage rather than a simple excrement pumping truck and a dirt suction truck.

Owner:蓝文贵

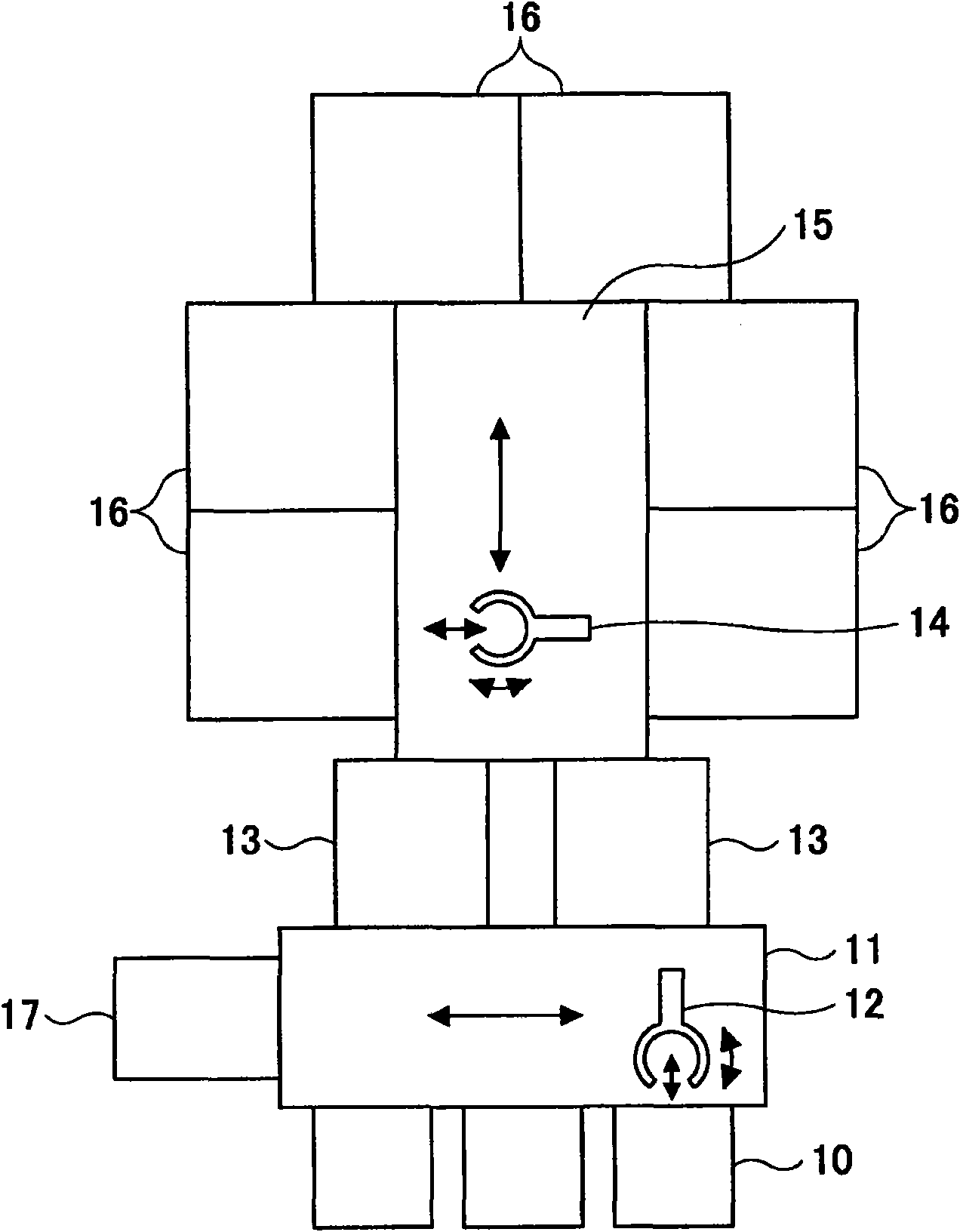

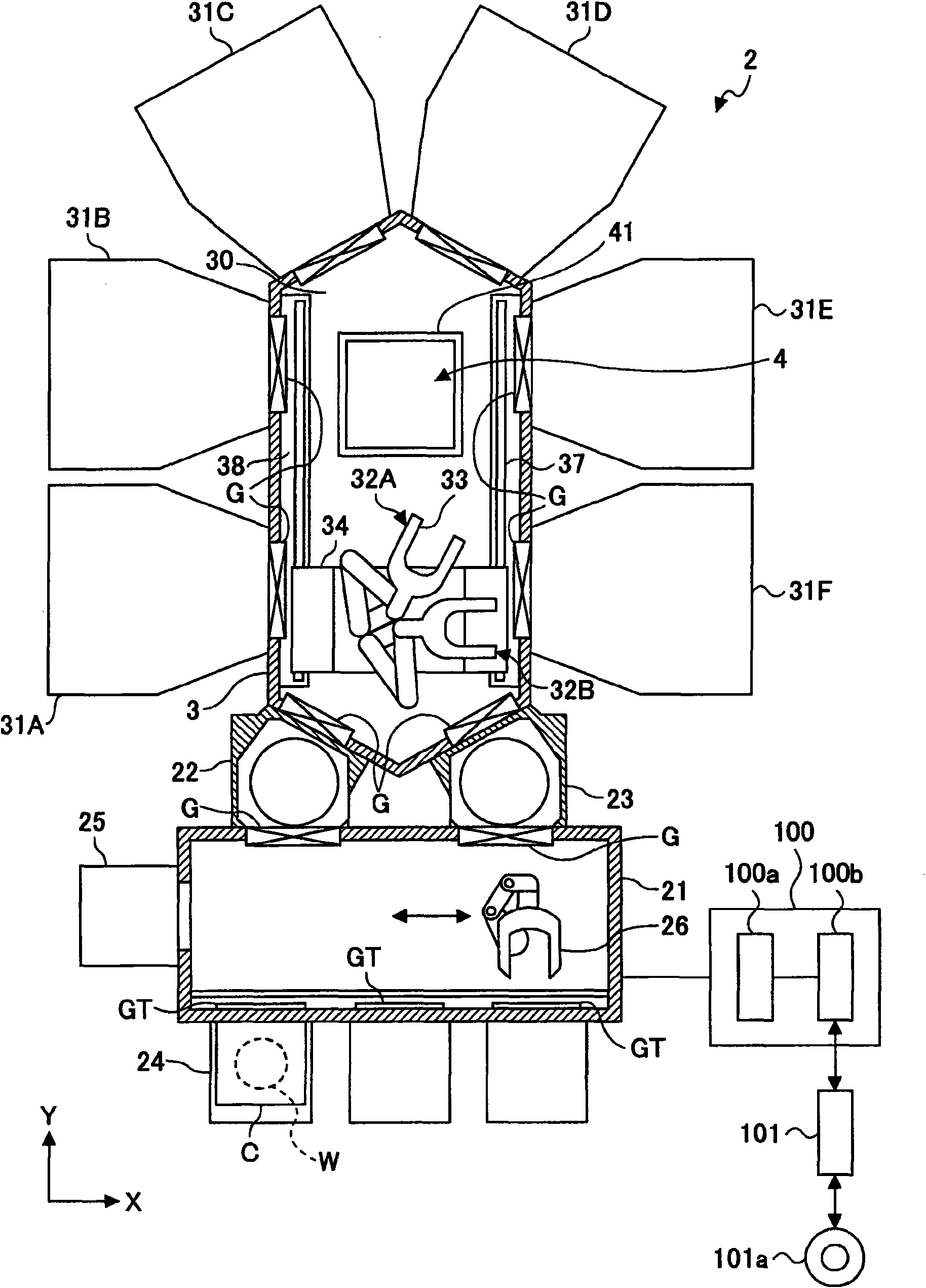

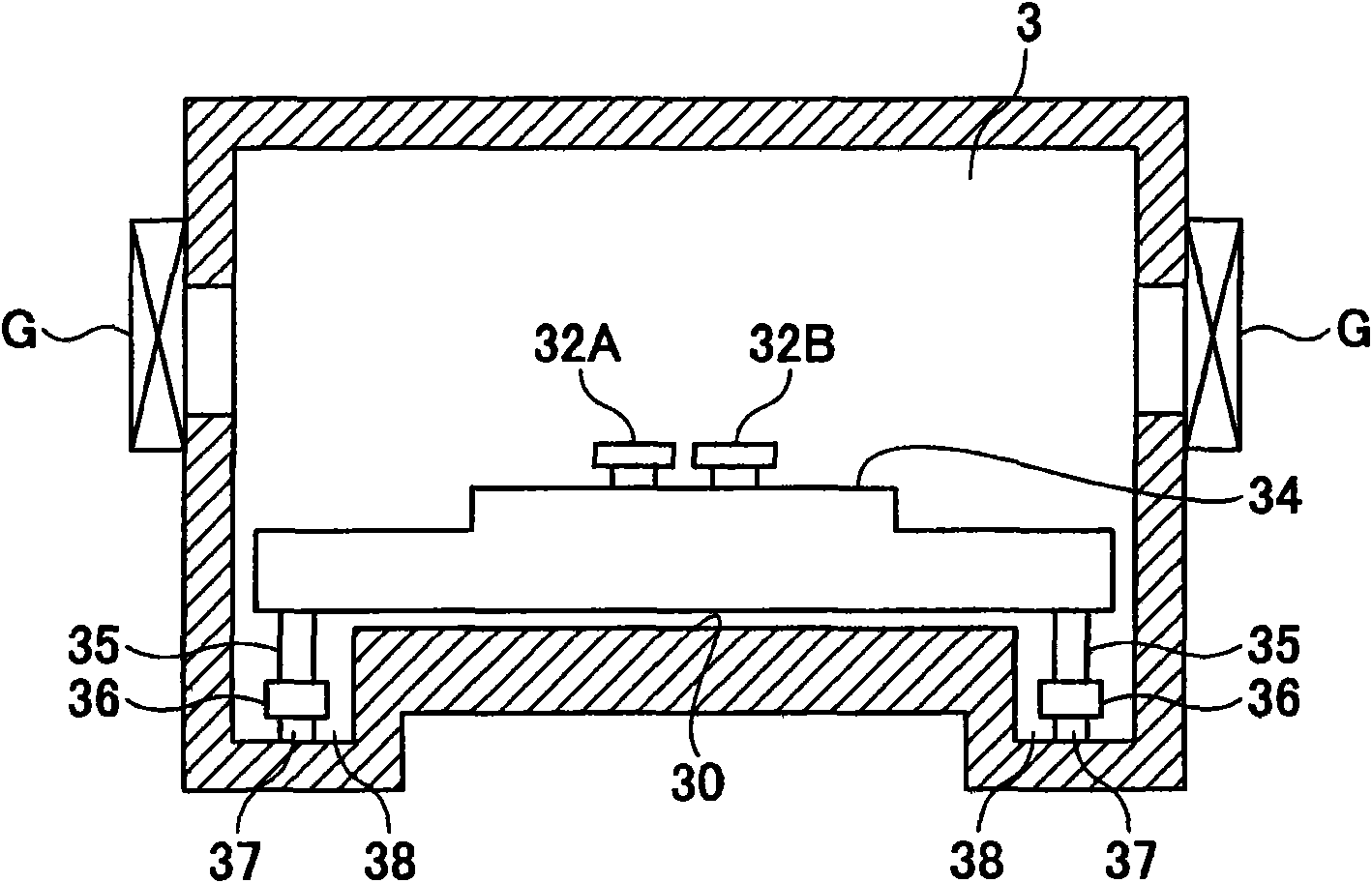

Vacuum processing device, vacuum processing method, and computer-readable storage medium

InactiveCN101911275AReduce the occupied areaWaiting to be addedProgramme-controlled manipulatorVacuum evaporation coatingInternal pressureComputer module

A vacuum processing device comprises a spare vacuum chamber in which the internal pressure is capable of switching between normal pressure and reduced pressure and into / out of which a substrate is carried, plural processing chambers in which various kinds of processing are performed on the substrate, a substrate transfer chamber by which the spare vacuum chamber and the plural processing chambers are connected and which includes a substrate transfer mechanism for transferring the substrate between the spare vacuum chamber and the plural vacuum processing chambers and a recess formed in a bottom portion or a ceiling portion, an auxiliary module in which predetermined processing is performed on the substrate transfer mechanism, and a lifting mechanism for moving the auxiliary module between a first position at which the auxiliary module is housed in the recess so as not to interfere with the transfer of the substrate by the substrate transfer mechanism and a second position at which the substrate is carried into / out of the auxiliary module by the substrate transfer mechanism.

Owner:TOKYO ELECTRON LTD

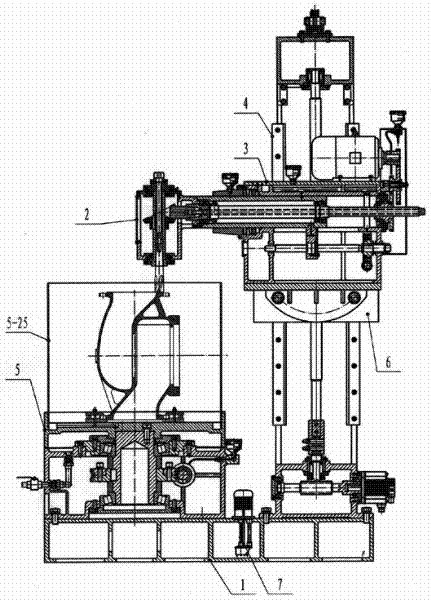

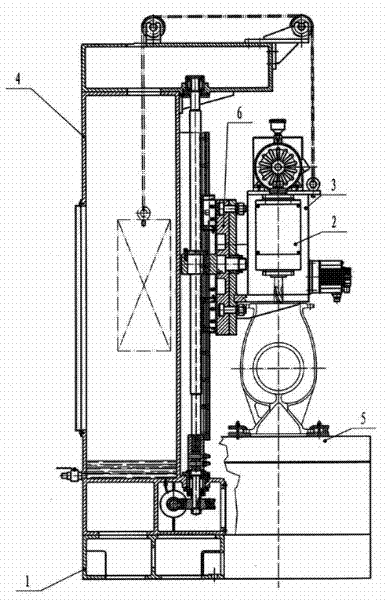

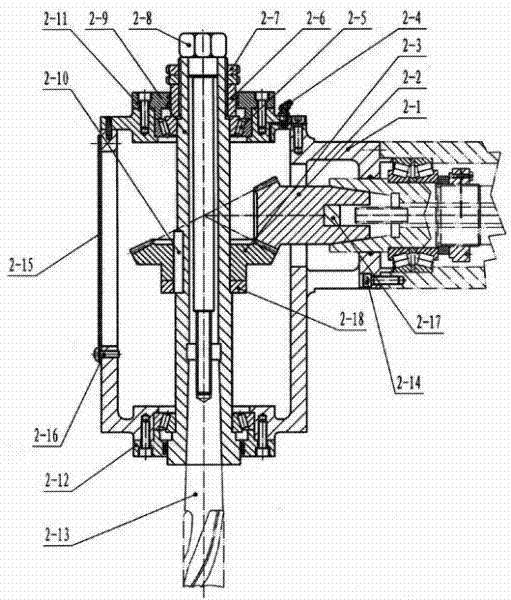

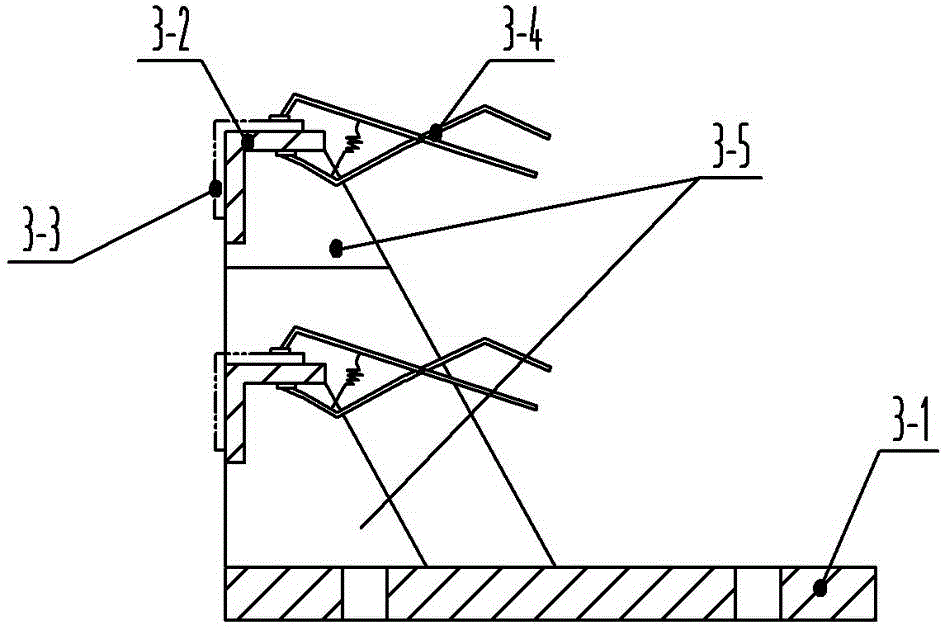

Multifunctional vertical combined machining lathe

InactiveCN102357799AEasy to replaceAdd processing functionOther manufacturing equipments/toolsLarge fixed membersEngineeringKnife holder

The invention provides a multifunctional vertical combined machining lathe. The multifunctional vertical combined machining lathe comprises a lathe body, a knife rest mechanism, a spindle box, an upright column mechanism and a control system, wherein, the upright column mechanism is fixed on the lathe body; the spindle box is assembled on the upright column mechanism; the knife rest mechanism is connected on the spindle box; a rotary worktable is fixed on the lathe body and is mainly composed of a rotating platform, a spindle, a frame and a servo motor; the rotating platform is equipped with a fixture for fixing parts and is fixed on the spindle; the spindle extends into the frame and is arranged on the frame through bearings at journals of upper and lower ends, and a sleeve and a worm wheel are arranged on the spindle between the bearings on the two ends; the frame is fixed on the lathe body and is equipped with a worm shaft meshed with the worm wheel on the spindle; and the servo motor is fixed on the frame and is used for driving the worm shaft. The multifunctional vertical combined machining lathe has the functions of ensuring the machining precision, realizing automatic rotation and transposition of the rotary worktable, facilitating the replacement of the machining cutters, and increasing the machining functions of the lathe, thus achieving higher practicability and obvious economic effect.

Owner:UNICIMA VALVE MFG CHENGDU

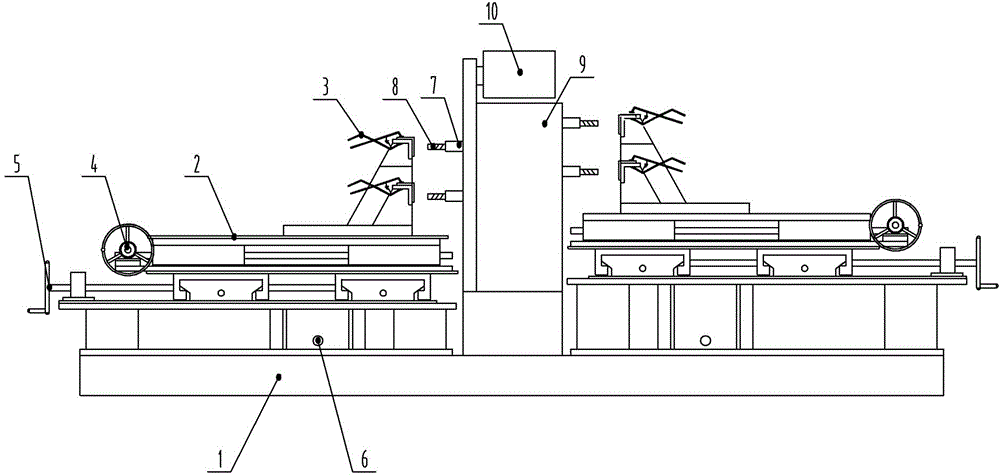

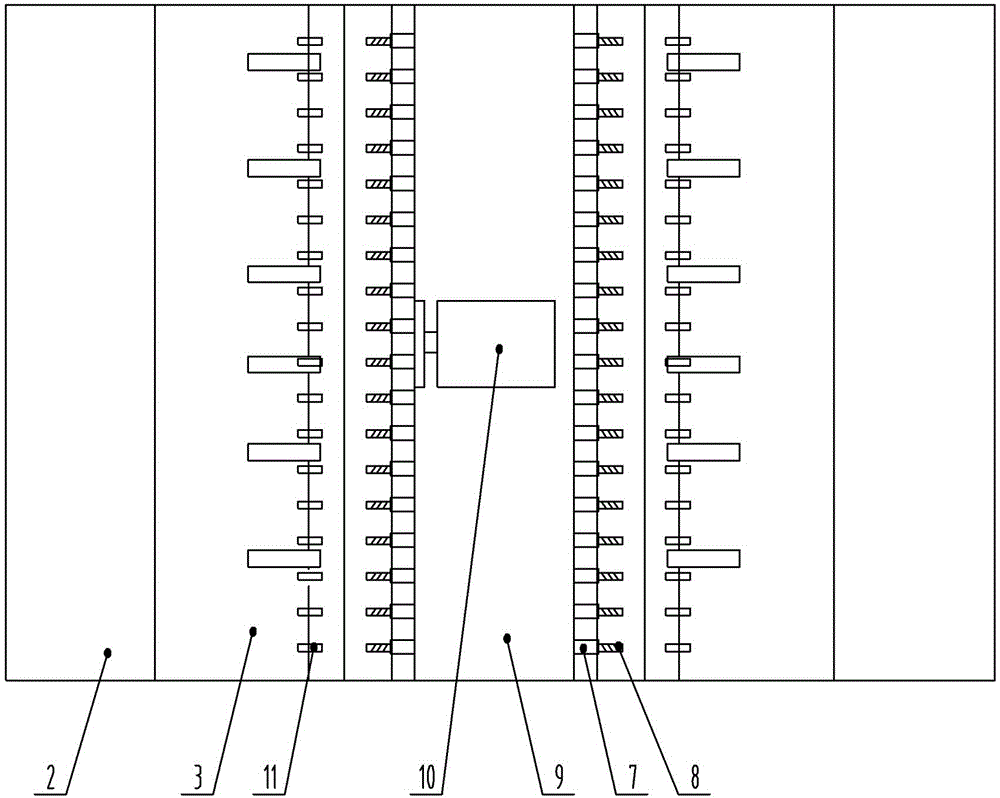

Linear type multiple row horizontal-type-like double-face machining multiple spindles drilling machine

ActiveCN104588725AImprove processing efficiencyImprove artificial efficiencyLarge fixed membersPositioning apparatusGear wheelEngineering

The invention belongs to the technical field of machining equipment, in particular relates a linear type multiple row horizontal-type-like double-face machining multiple spindles drilling machine. The drilling machine comprises a common-base, a machine body, workbenches, a clamp and a drilling hole unit, the drilling hole unit is longitudinally and centrally installed along the top surface of the common-base; two workbenches are respectively installed on the machine body of two longitudinal ends of the common-base, and a workbench longitudinal reciprocating movement mechanism, a workbench lateral reciprocating movement mechanism and a workbench lifting movement mechanism are arranged inside the machine body from top to bottom; the clamp comprises a support and a clamping element; multi-layer transverse shelves are arranged on the support from top to bottom, a plurality of clamping elements are arranged on each transverse shelf; the drilling hole unit comprises spindles, drills, a gear box and a driving mechanism, the spindles are evenly distributed and installed in the gear box from top to bottom in a multi-row manner, two adjacent rows of spindles are arranged from top to bottom in a staggering manner, and the extending directions of the drills are opposite, the driving mechanism comprises a plurality of gears which are engaged with one another to carry out transimission, a main drive mechanism and a power mechanism. The linear type multiple row horizontal-type-like double-face machining multiple spindle drilling machine can processes rows of holes which are fixed in intervals and hole diameter on multiple workpieces to be processed, the time and labor are saved, the processing efficiency is high and the machining is precise.

Owner:王瑞方

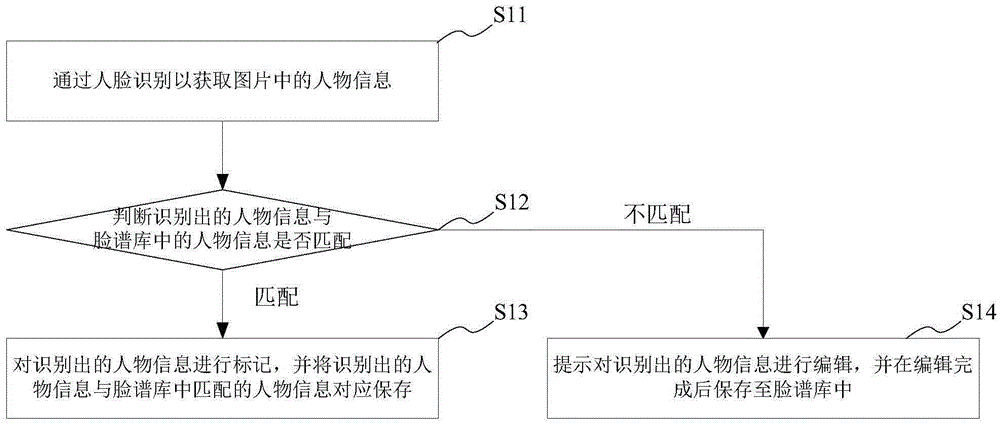

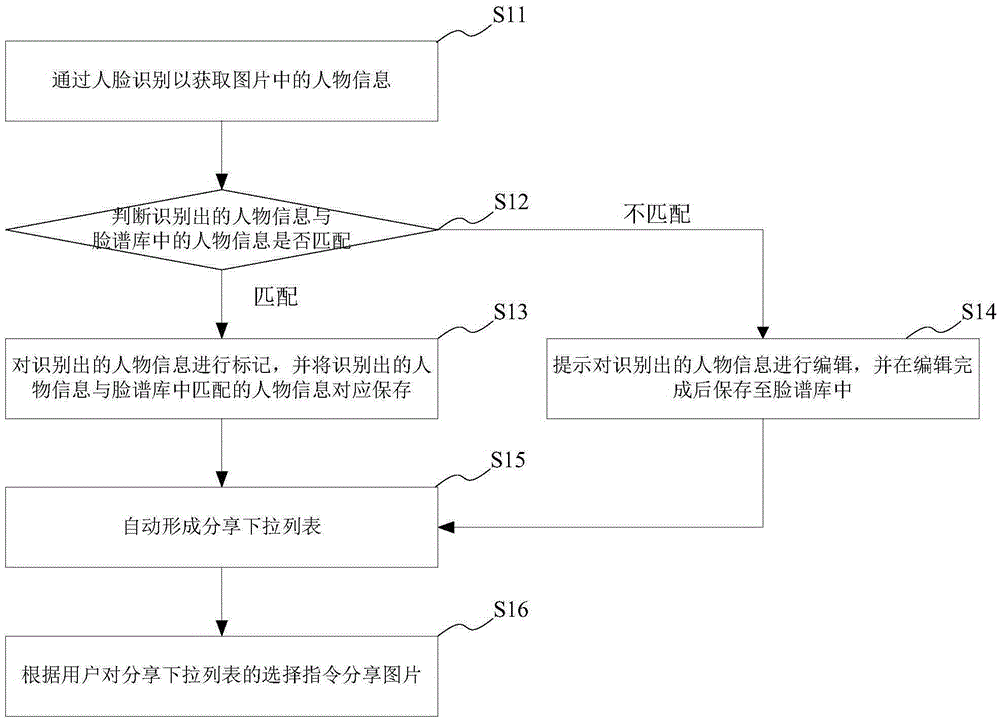

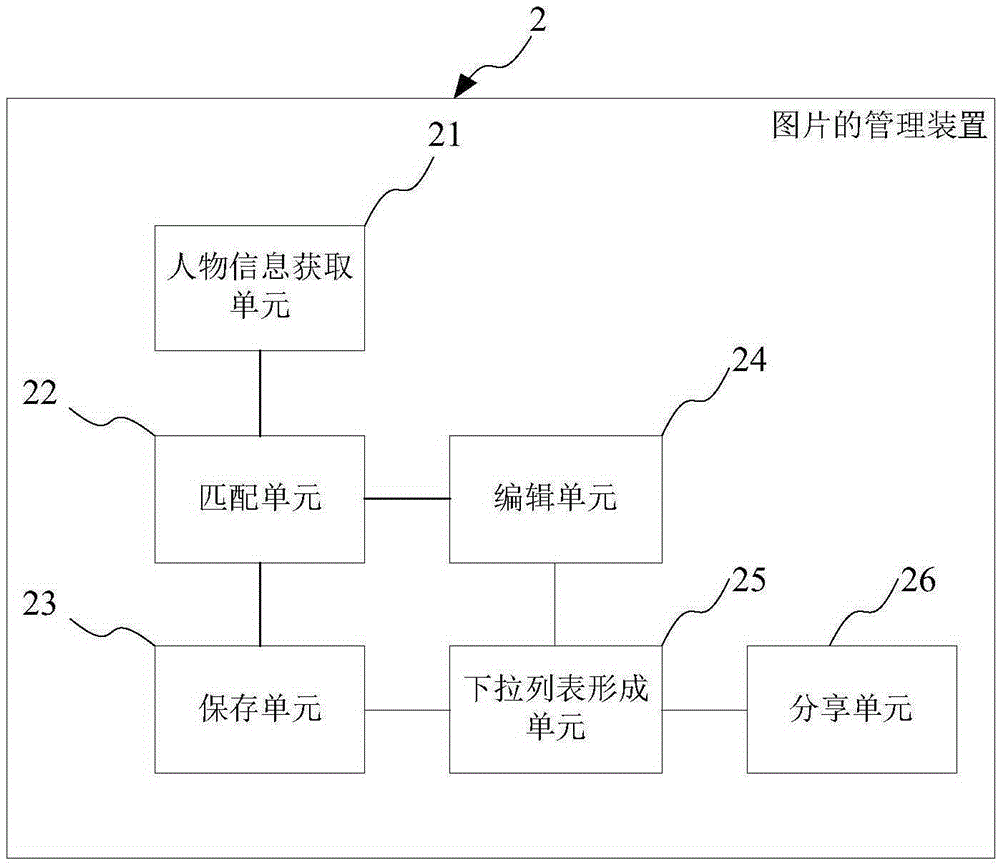

Picture managing method and device

InactiveCN105260487AIncrease processing functionShorten the timeStill image data indexingSpecial data processing applicationsKnowledge managementMultimedia

The invention provides a picture managing method and device. The method comprises the steps of acquiring people information in a picture through face identification, judging whether the identified people information is matched with people information in a face base, marking the identified people information and saving the identified people information and the matched people information in the face base correspondingly if yes, and instructing that the identified people information be edited and saving the edited people information in the face base if not. By the adoption of the picture managing method and device, automatic identification of people information is achieved, a pull-down list can be automatically formed and shared, so that picture sharing is greatly facilitated for users and sharing efficiency is improved, and then user experience is improved.

Owner:PHICOMM (SHANGHAI) CO LTD

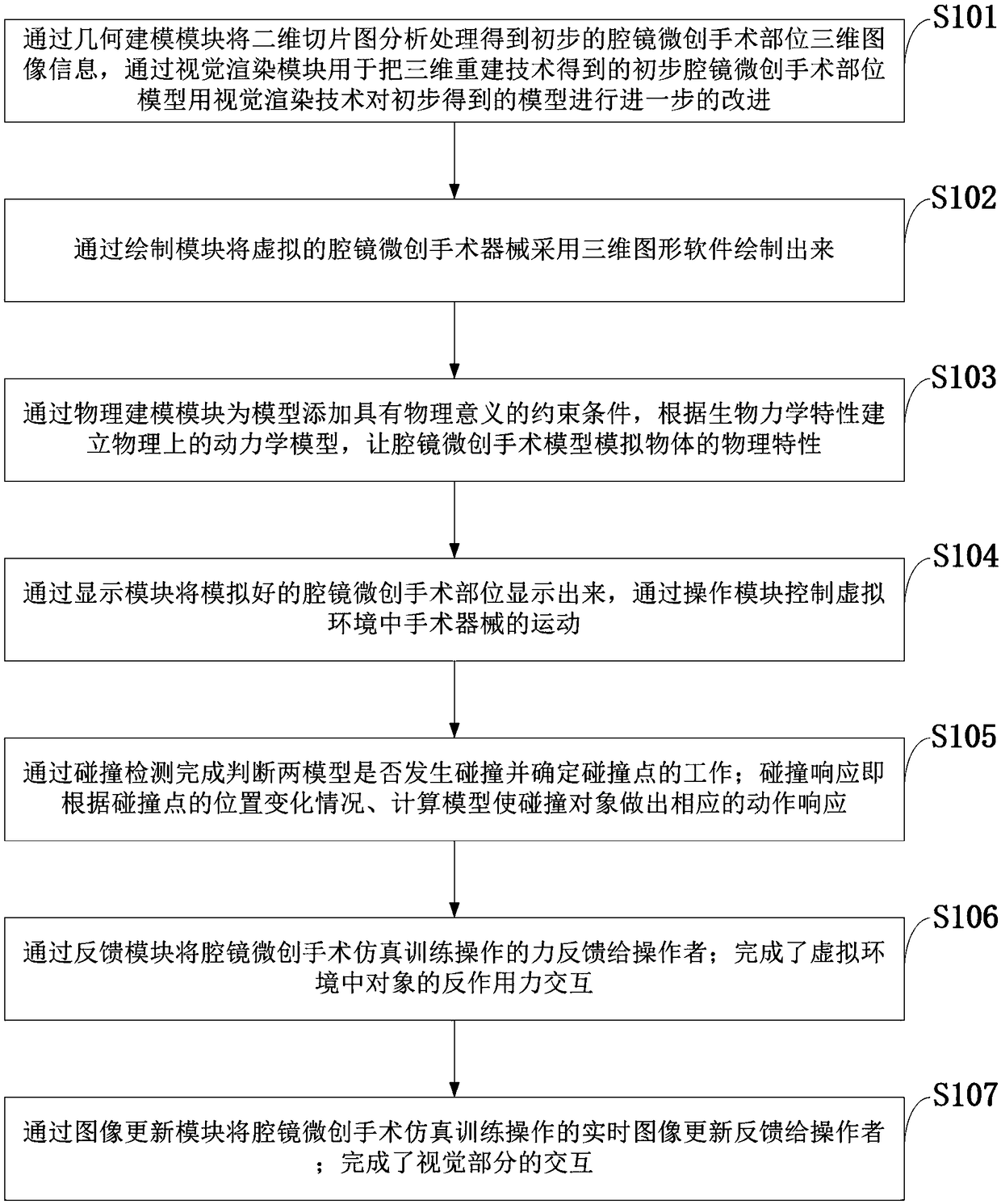

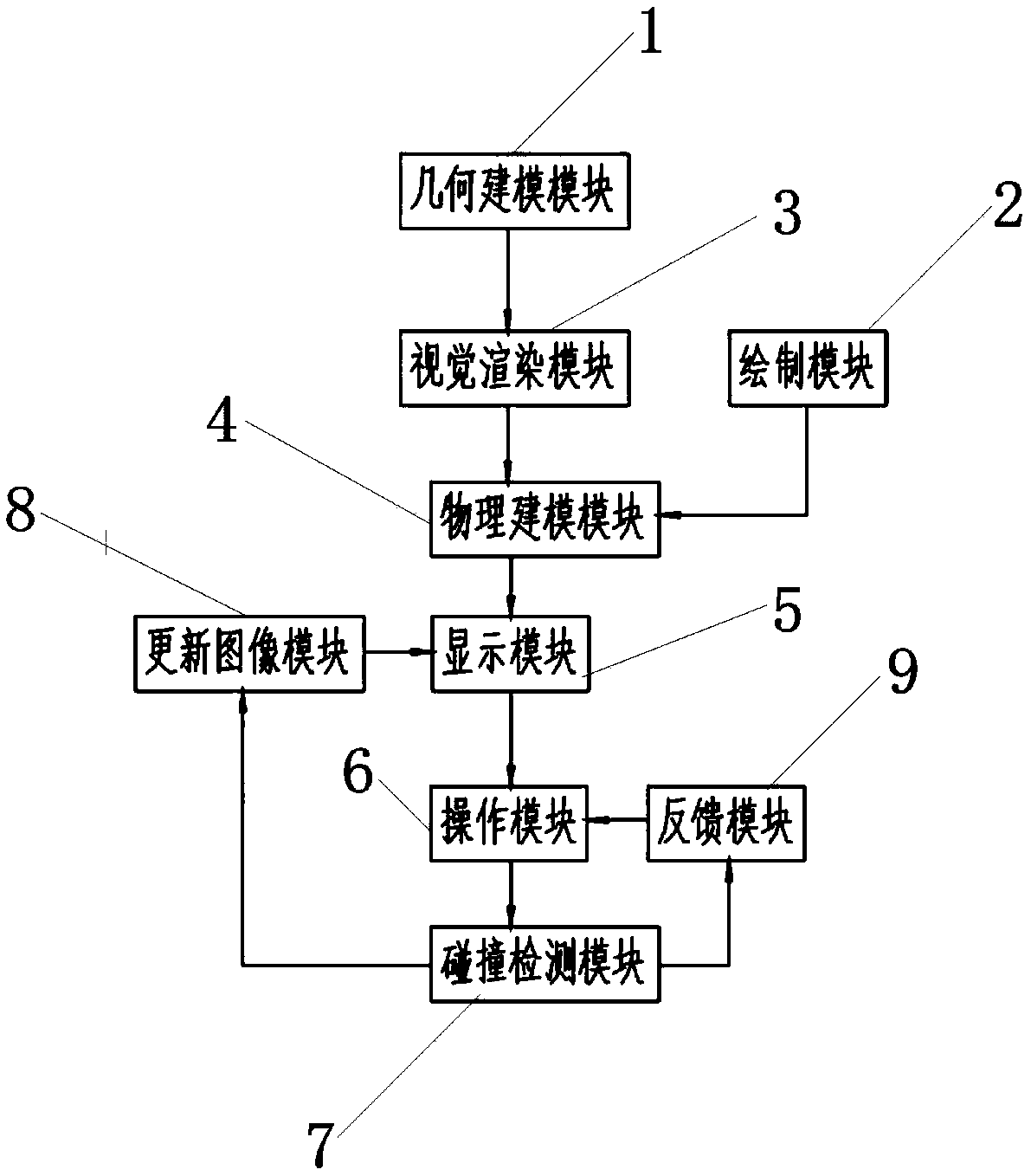

Virtual-reality-based real endoscopic minimally invasive surgery simulation training system and method

InactiveCN109192030AProtection securityHigh cure rateEducational modelsMedical equipmentCollision detection

The invention belongs to the technical field of medical equipment, and discloses a virtual-reality-based real endoscopic minimally invasive surgery simulation training method, which comprises a geometric modeling module, a drawing module, a visual rendering module, a physical modeling module, a display module, an operation module, a collision detection module, an update image module and a feedbackmodule. The three-dimensional image information is obtained by the geometric modeling module, and the model is improved by the visual rendering module. The virtual surgical instrument is rendered bythe rendering module. Physically significant constraints are added to the model through the physical modeling module; the simulated endoscopic minimally invasive surgical site is displayed by the display module, and the movement of surgical instruments in the virtual environment is controlled by the operation module. Collision detection is used to judge whether the two models collide and determinethe collision point. The feedback module is used to realize the interaction of the reaction force of the object in the virtual environment; and the interaction of the visual part is completed throughthe image update module.

Owner:THE FIRST AFFILIATED HOSPITAL OF ZHENGZHOU UNIV

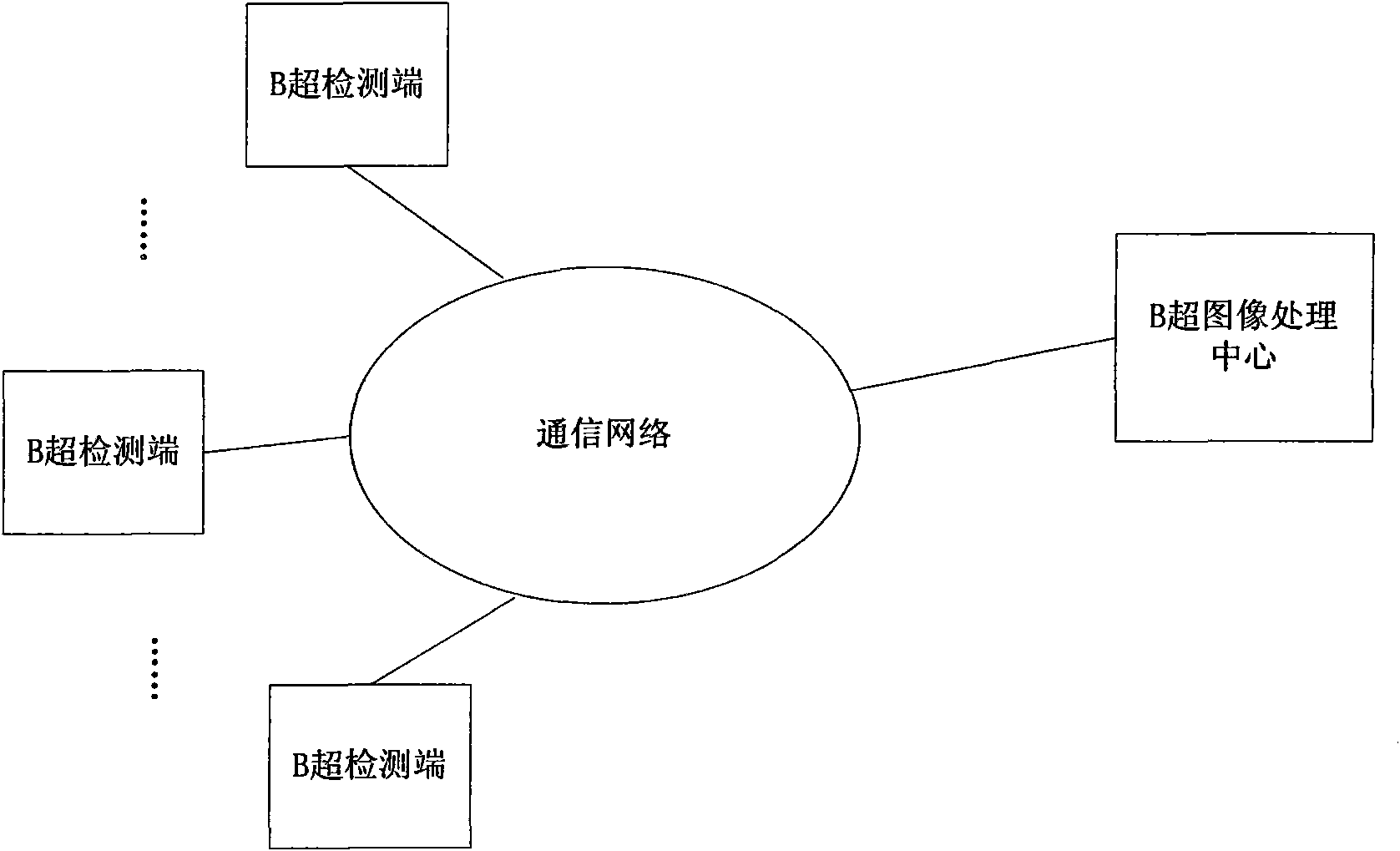

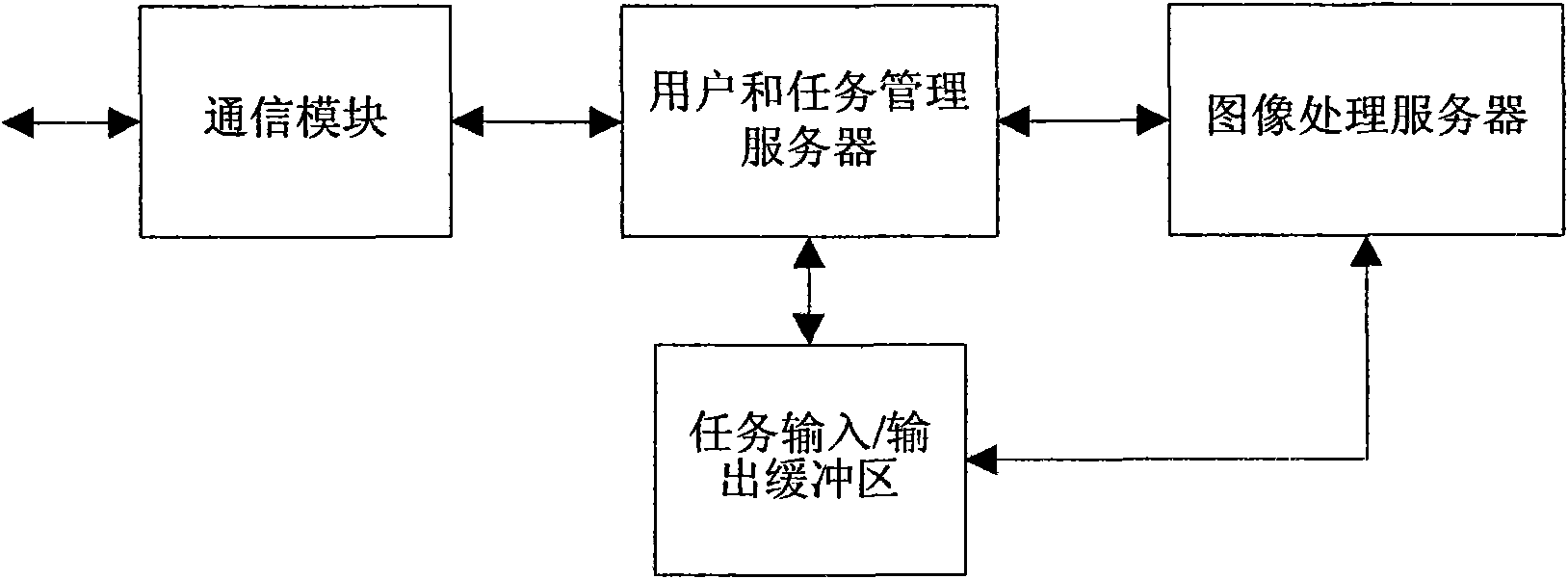

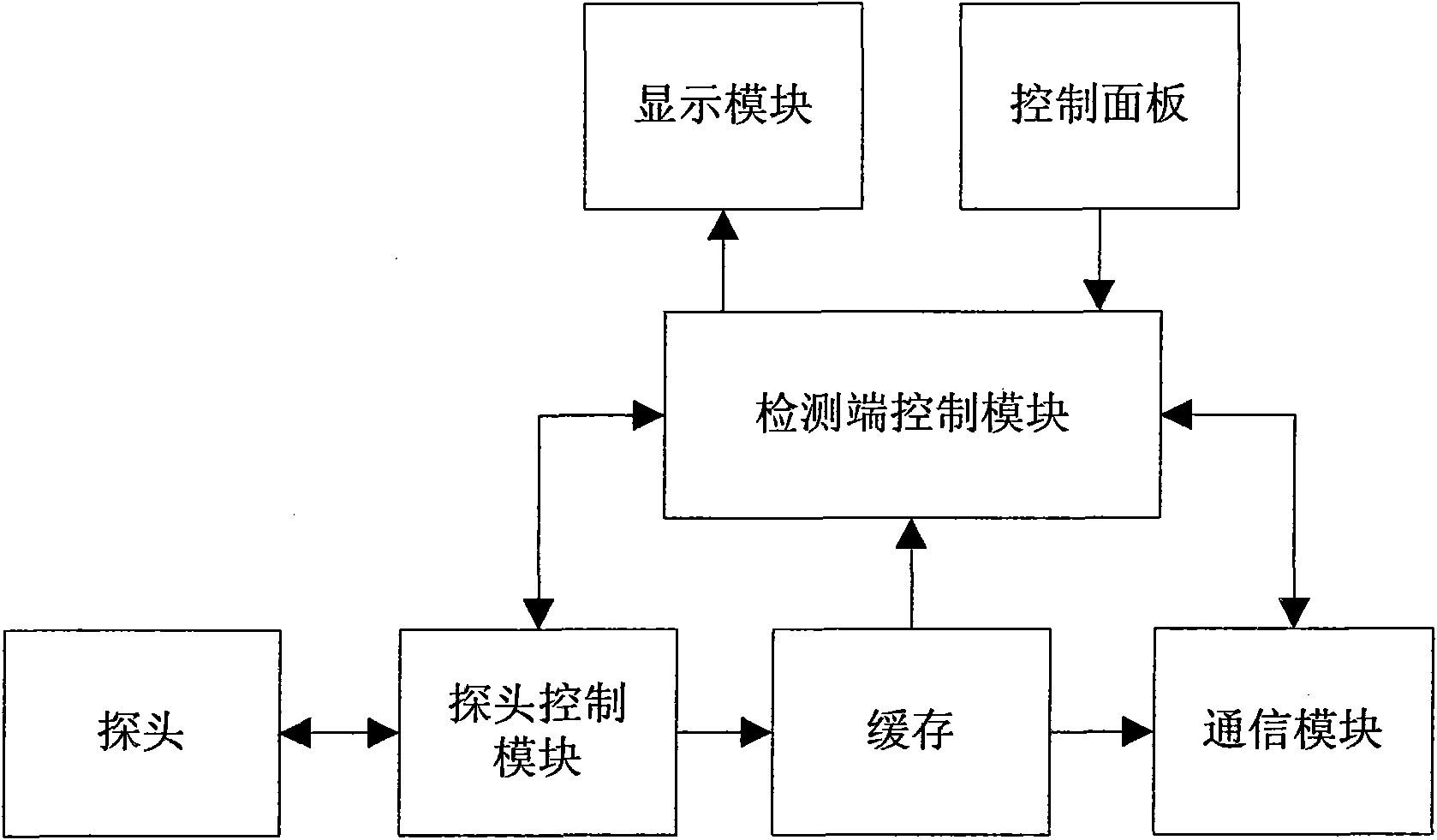

Distributed type-B ultrasonic inspection system and processing method for ultrasonic detection signals thereof

InactiveCN101569542AIncrease profitReduce idle rateUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsImaging processingResource utilization

The invention relates to a distributed type-B ultrasonic inspection system and a processing method for ultrasonic detection signals thereof, wherein the system comprises a type-B ultrasonic image processing center for communication through a communication network, and a plurality of type-B ultrasonic detecting terminals; the type-B ultrasonic image processing center comprises a communication module, a user and task management server, a task input / output buffer area and an image processing server; the communication module is connected with the user and task management server, and the user and task management server, the task input / output buffer area and the image processing server are mutually connected; the type-B ultrasonic detecting terminals comprise probes, probe control modules, a cache, communication modules, detection terminal control modules, display modules and control panels; the probes, the probe control modules, the cache and the communication modules are connected in turn, and the detection terminal control modules are connected with the probe control modules, the cache and the communication modules, the display modules and the control panels respectively; and the system and the method have the advantages of a host with shared computing power, high resource utilization rate, flexible use, low cost, strong expanding capability, and the like.

Owner:SOUTH CHINA UNIV OF TECH

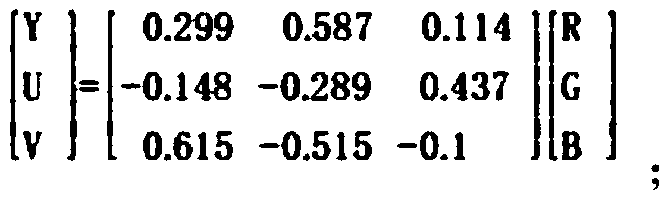

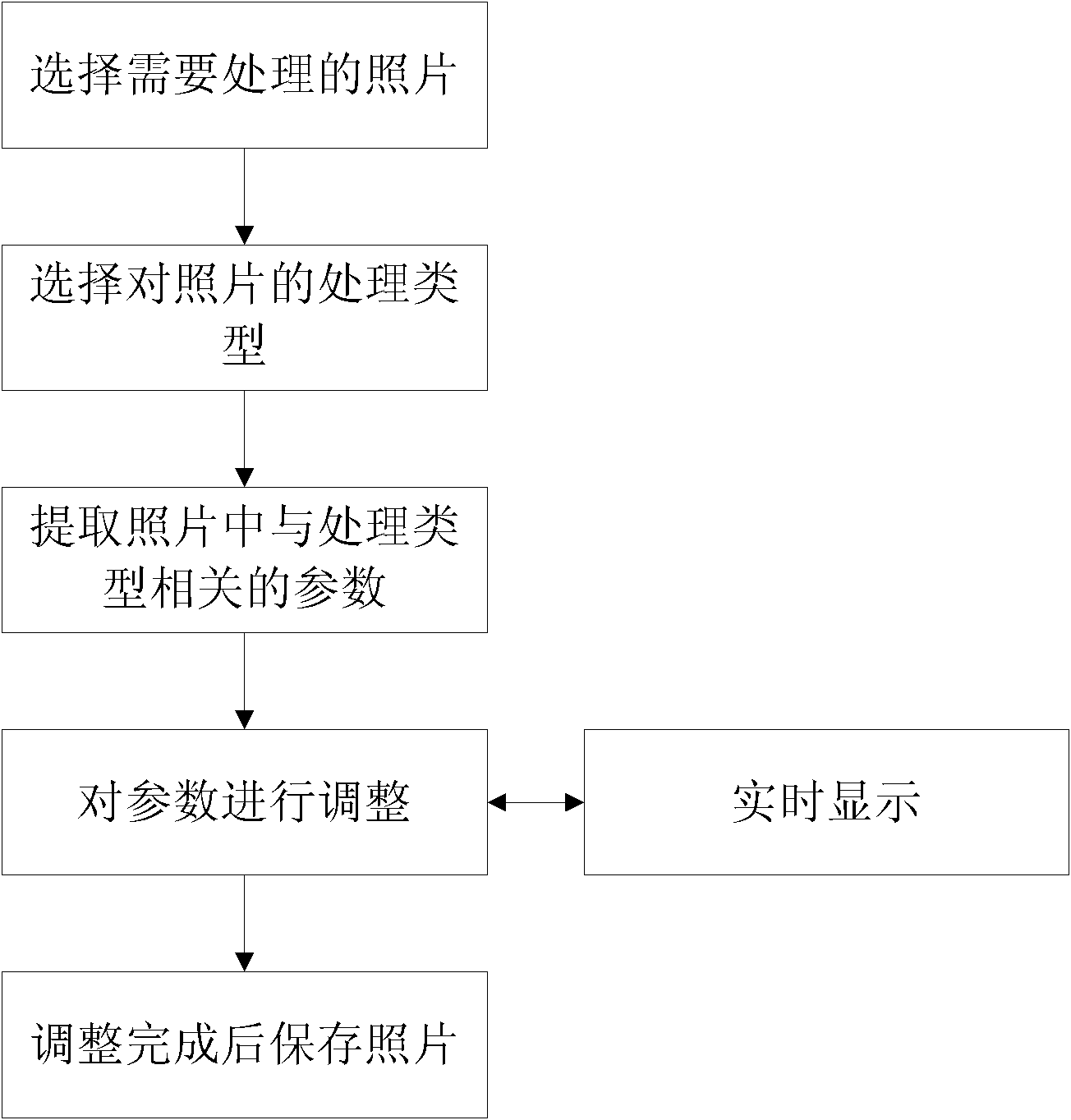

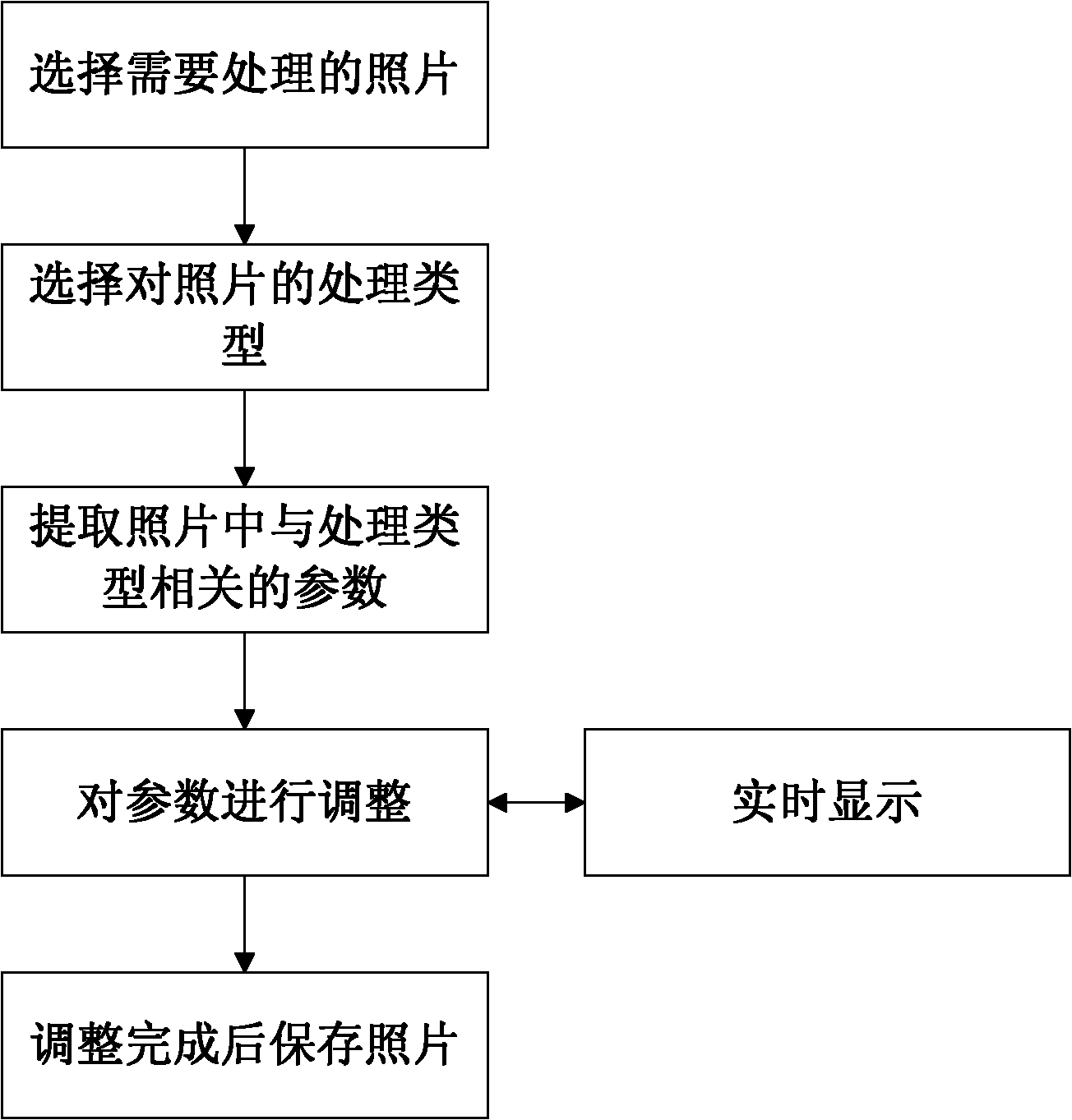

Method for processing photo by using digital camera and digital camera

InactiveCN101945202AIncrease processing functionQuality is not affectedTelevision system detailsColor television detailsProcessing typeComputer graphics (images)

The invention discloses a method for processing a photo by using a digital camera and a digital camera. The method comprises the following steps: (A) selecting the photo stored in the digital camera by using the control key of the digital camera; (B) designating the processing type for the photo; (C) extracting the parameters related to the processing type from the photo; (D) adjusting the extracted parameters, and displaying the adjustment result in real time by using the display screen of the digital camera; and (E) after the adjustment, storing the photo according to the adjusted parameters. The invention is characterized in that the photo processing function is added to the digital camera, so that the user can take photos according to demands in many particular cases; and thus, the invention enables the user to get rid of the restriction of the photo environment, does not affect the quality of the photo, eliminates worries about the photo defects for the users, and enhances the photo effect.

Owner:TIANJIN SAMSUNG OPTO ELECTRONICS

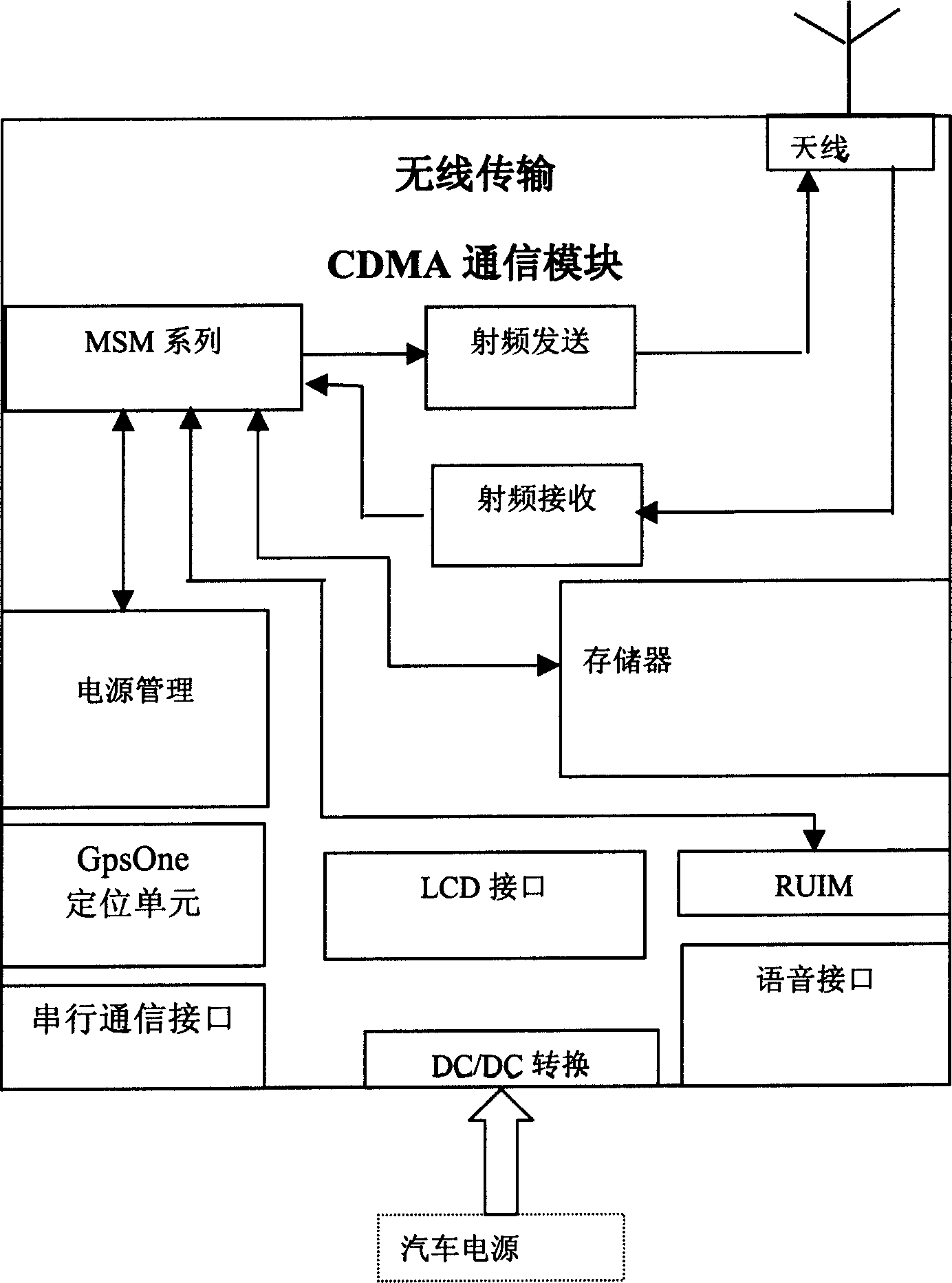

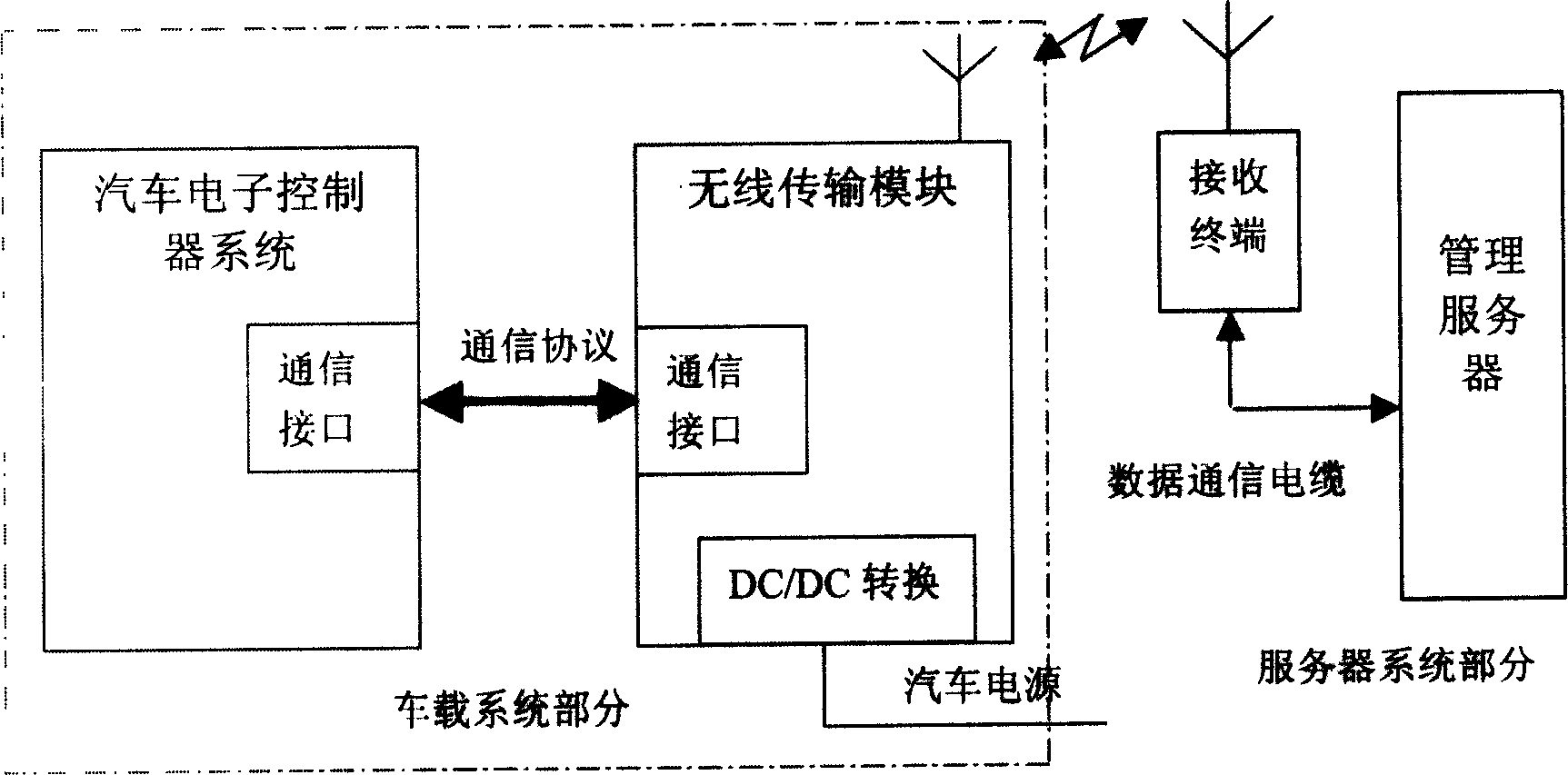

Automobile electronic control information wireless management system

InactiveCN1528620AIncrease processing functionEfficient integrationElectric/fluid circuitTotal factory controlElectronic controllerData information

The invention is a car electronic control information wireless management system, including car electronic controller which is added with serial communication interface and connected with the wireless transmission module through the communication protocol, the wireless transmission module transmits the data information to the receiving terminal through the wireless mobile net, and the receiving terminal is linked with the information management server through the communication cable. The wireless transmission module has voice calling function and the car user can selectively use vehicle-carried mobile telephone. It transmits various car control information to the information management server through the wireless mobile net, the database software inserted in the server provides failure diagnosis function and service prompt information for the user by means of collected analysis, management report, etc, and each car maintenance department terminal obtains the failure diagnosis information through INTERNET.

Owner:HISENSE +1

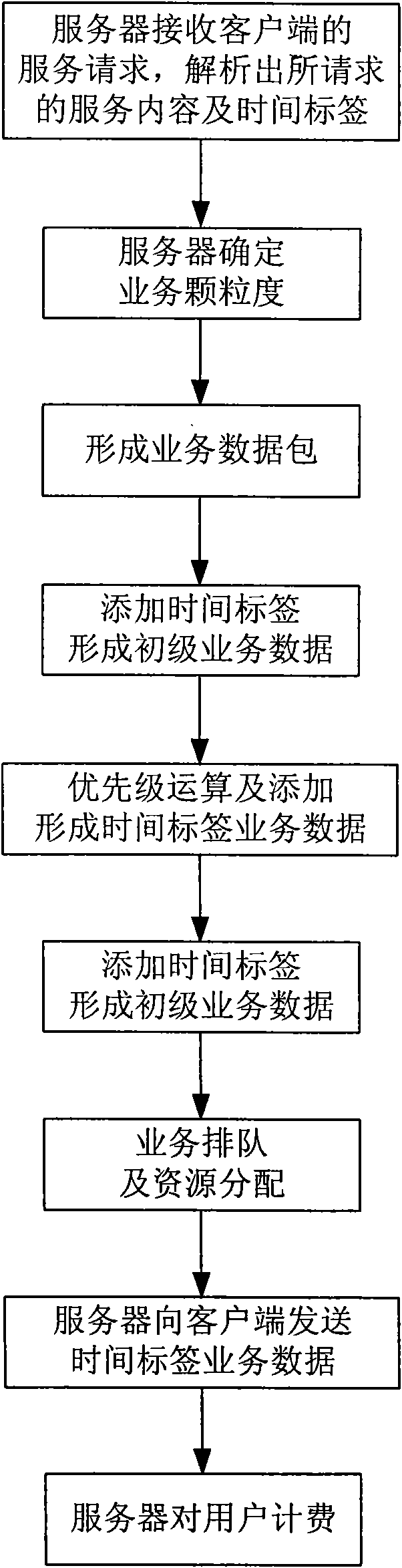

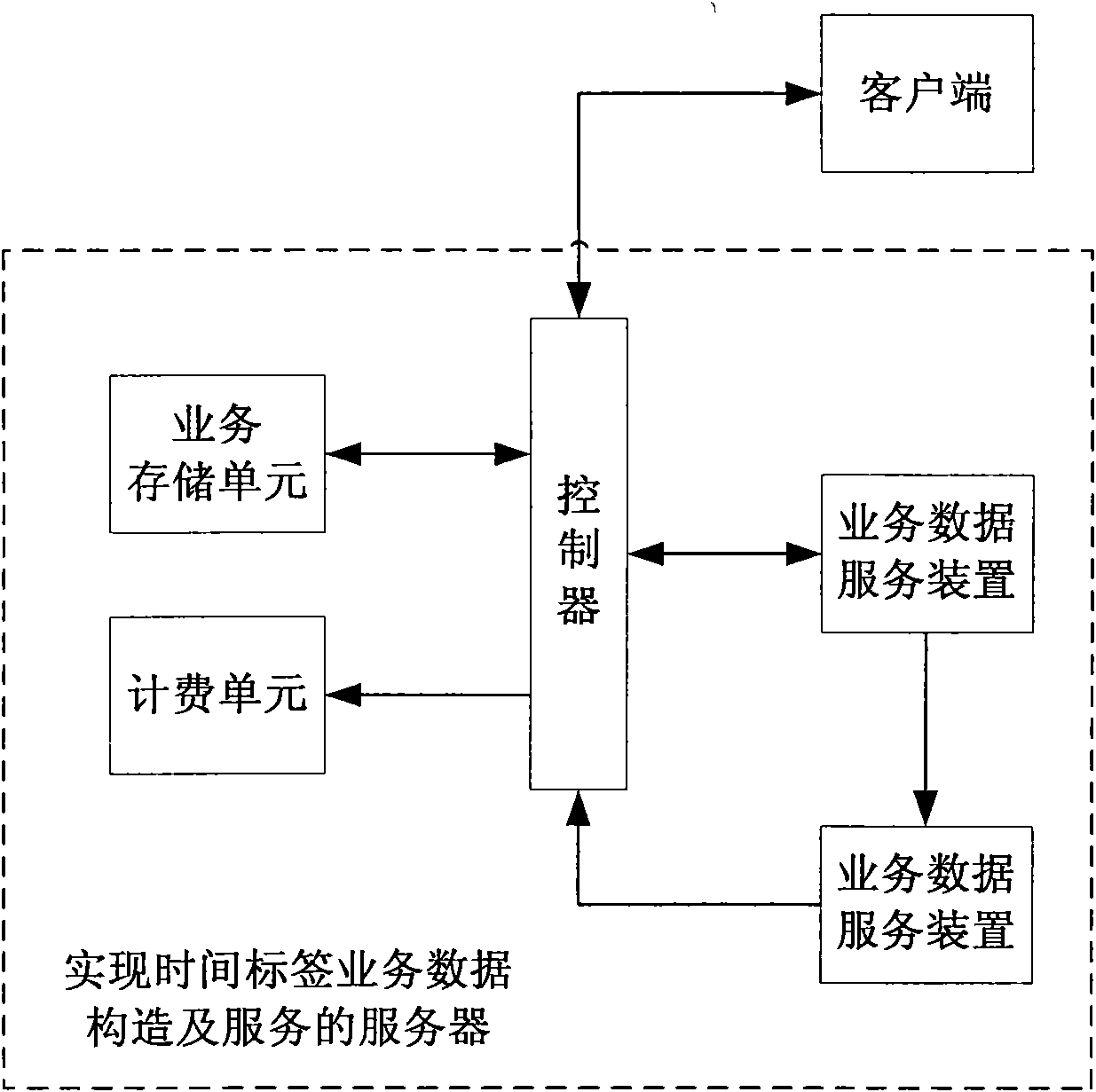

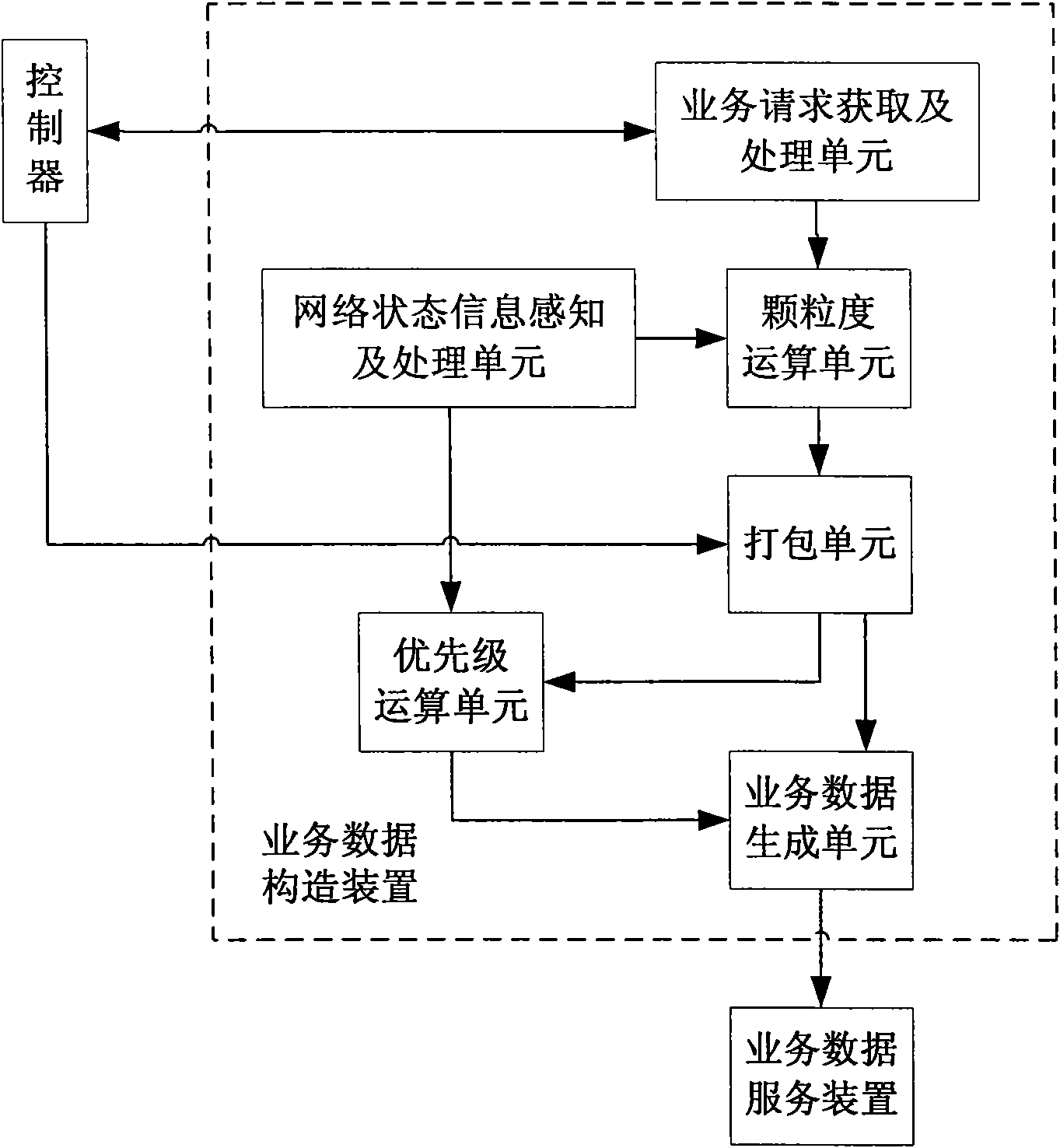

Method for construction and service of time tag business data for communication

ActiveCN101808117AImprove carrying capacityFlexible adjustment of granularityData switching networksTraffic capacityNetwork packet

The invention relates to a method for construction and service of time tag business data for communication, which belongs to the technical field of communication. The method comprises the following steps: receiving a service request of a client through a server at first, analyzing business contents in the request and time tag information corresponding to the contents, and packaging the original data to form a business data packet according to the granularity of the time tag information; adding the time tag information into the business data packet to form a primary business data packet; obtaining a priority level of the primary business data packet according to the time tag information, and constructing time tag business data; determining a transmission sequence through the server according to the network communication capacity, the priority level and the time tag information; configuring the number of resources for storage, computation and communication of each time label business data; and transmitting the business contents of the request to the client and charging according to the transmission sequence. The invention makes the business flow in the network smooth, and eases the tension of resource allocation and the pressure for upgrading the network equipment.

Owner:TSINGHUA UNIV

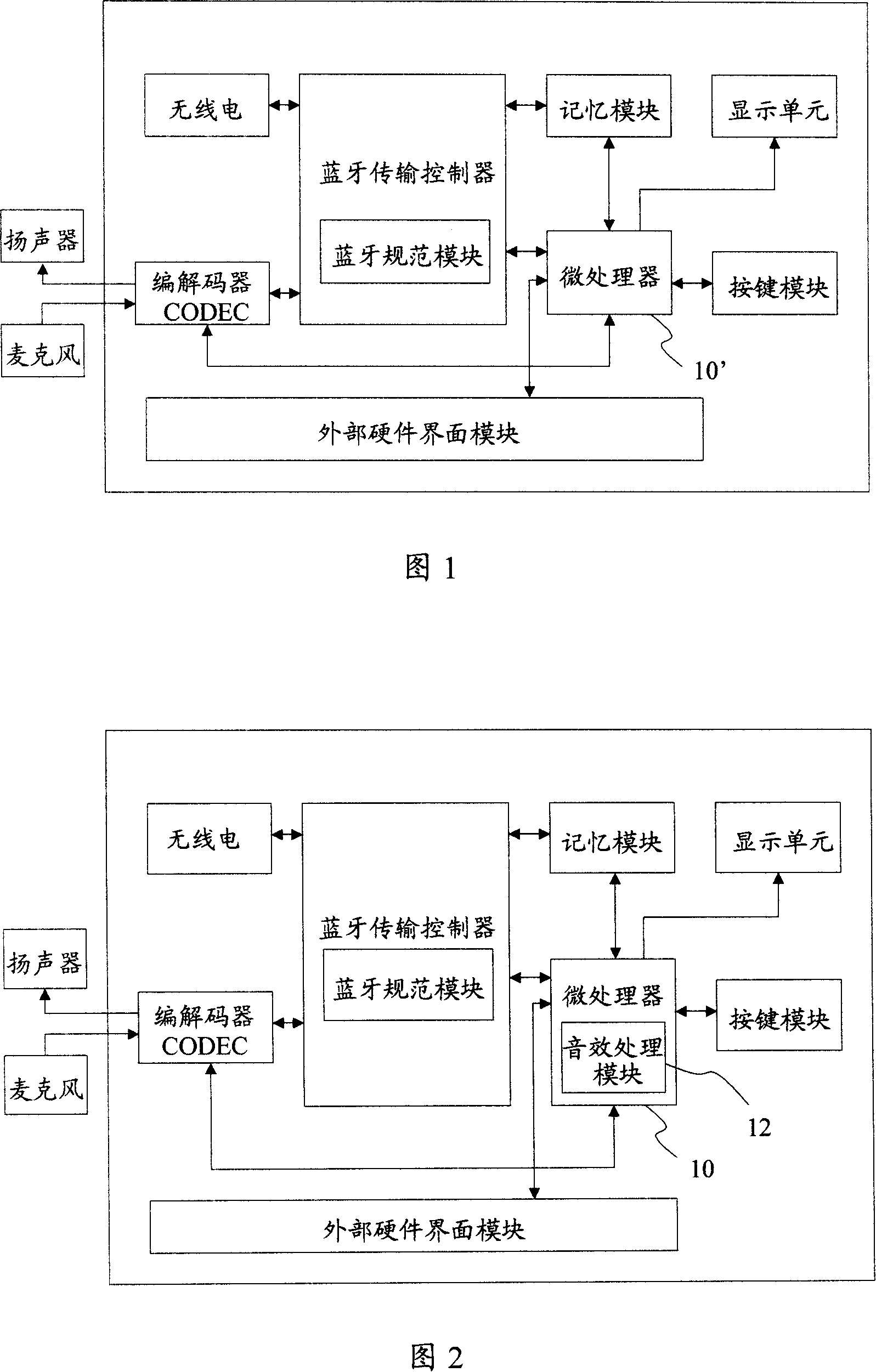

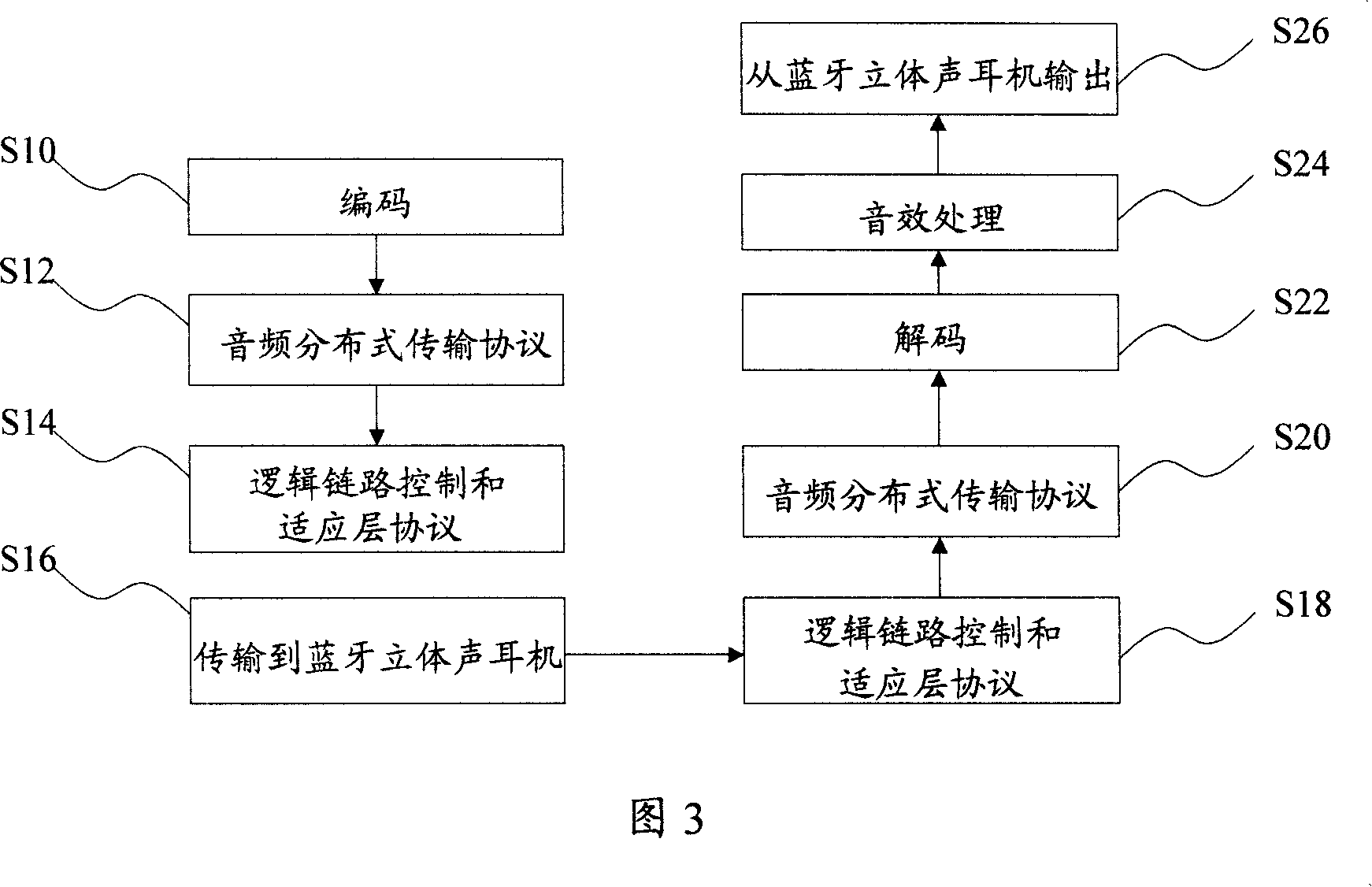

Method for intensifying sound effect processing function of Bluetooth stereo device

InactiveCN101155439AIncrease processing functionAdd sound processing functionStereophonic circuit arrangementsPseudo-stereo systemsDigital signal processingProcess function

A method for adding sound effect process function of a Bluetooth stereo device is provided in the present invention, adding a digital signal process technology to the Bluetooth stereo device and adding a sound effect process module for processing stereo sound source series flow, adding special sound effect series flow into the form of the sound source series flow after subband coding (Subband coding, SBC) decoding received by the Bluetooth stereo device, sound effect process function containing super bass process function, sound effect simulating various sound fields and process function of the dynamic equalizer, wherein the super bass process bases on using human ear lost basic frequency effect, and the simulating various sound fields bases on the rebound of sound in space, sound positioning process technology and sound effect simulating technology etc., leading the stereo sound effect to be perfect while process sound effect process.

Owner:NFORE TECH CO LTD

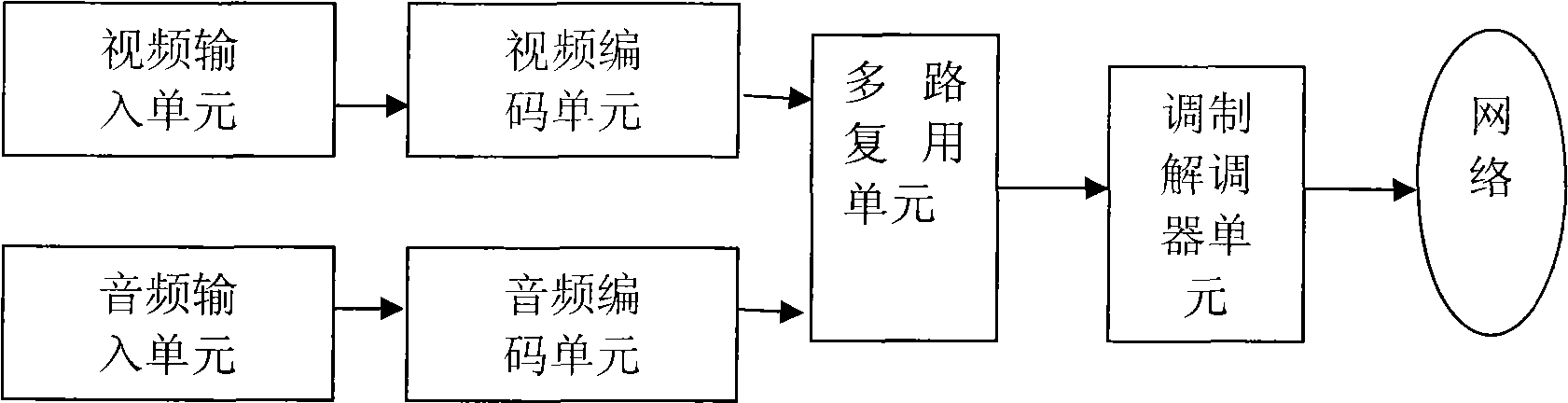

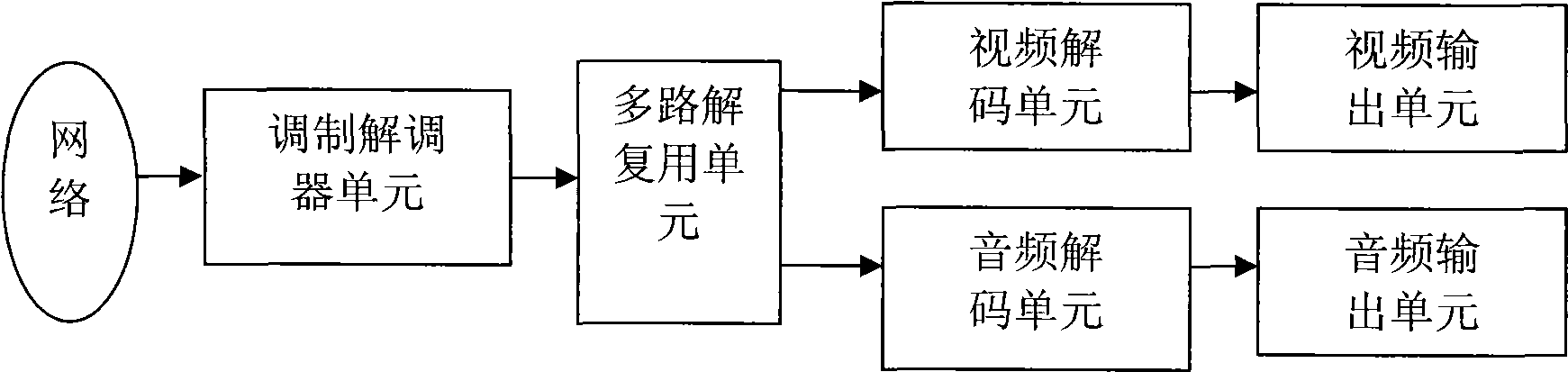

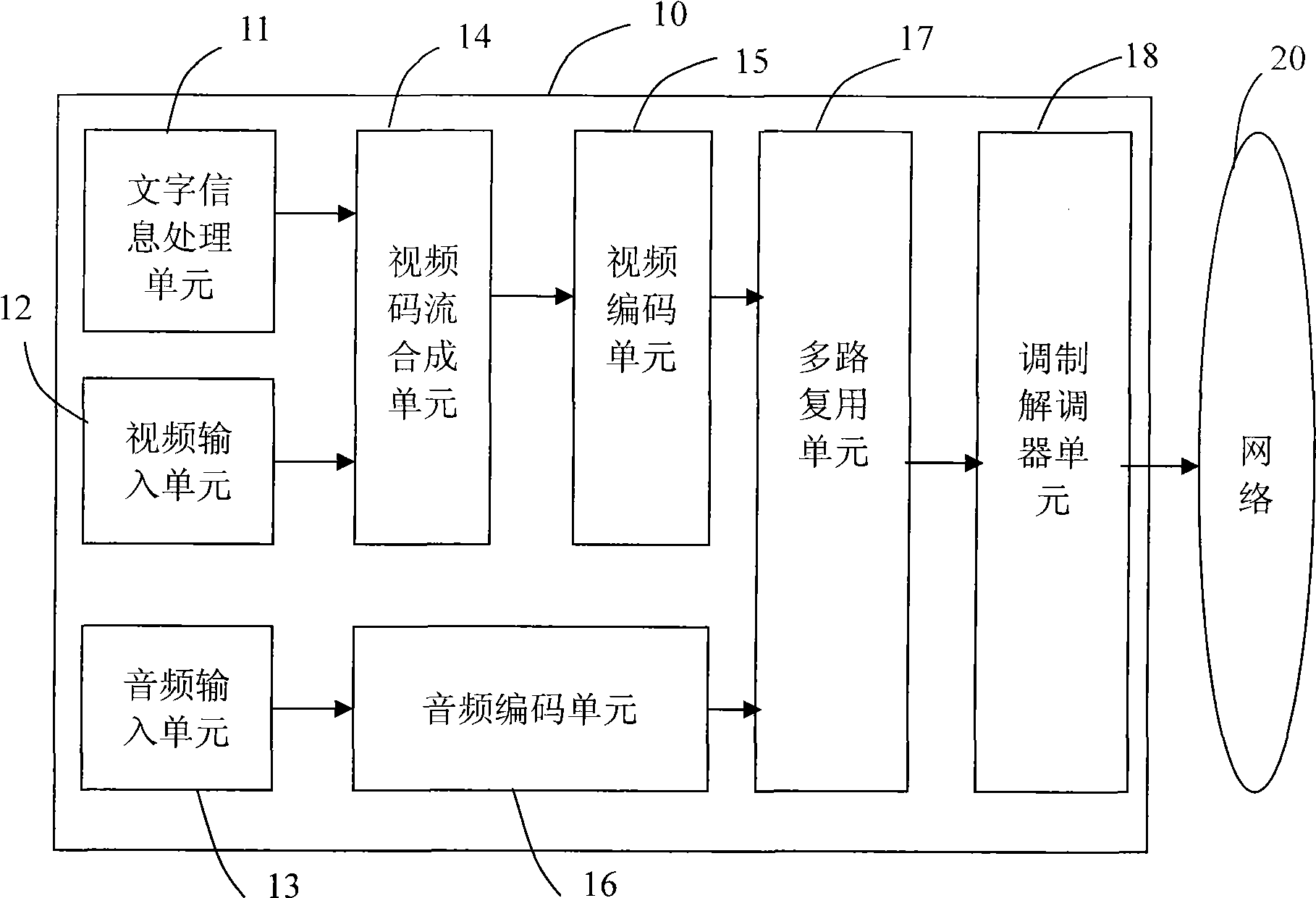

Video telephone, system and method for realizing word message sending function during video communication.

InactiveCN101521789AIncrease processing functionRealize the sending functionPulse modulation television signal transmissionTwo-way working systemsComputer hardwareVideo encoding

The invention discloses a video telephone, a system and a method for realizing a word message sending function during video communication. The video telephone comprises a word message processing unit, a video input unit, a video code stream synthesis unit, a video coding unit and a modem unit, wherein the video input unit is used for collecting video data of a sending terminal user, the word message processing unit is used for inputting word messages to be sent and transforming the word messages to video data of a video format adopted by the video input unit, the video code stream synthesis unit is used for processing video data output by the video input unit and video data output by the word message processing unit in a superposed way so as to form new mixed video data with word messages, and the video coding unit is used for coding the new mixed video data with word messages and transmitting the new mixed video data with word messages to a receiving terminal by the modem unit. The invention can meet the requirement of realizing word input during the video communication.

Owner:ZTE CORP