Video processing on-chip system of double AHB (Advanced High Performance Bus) buses

A technology for video processing and system-on-chip, which is applied to components of TV systems, electrical digital data processing, and TV. It can solve problems affecting system performance and low system efficiency, and achieve the effect of improving processing efficiency and high flexibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further elaborated below in conjunction with the accompanying drawings.

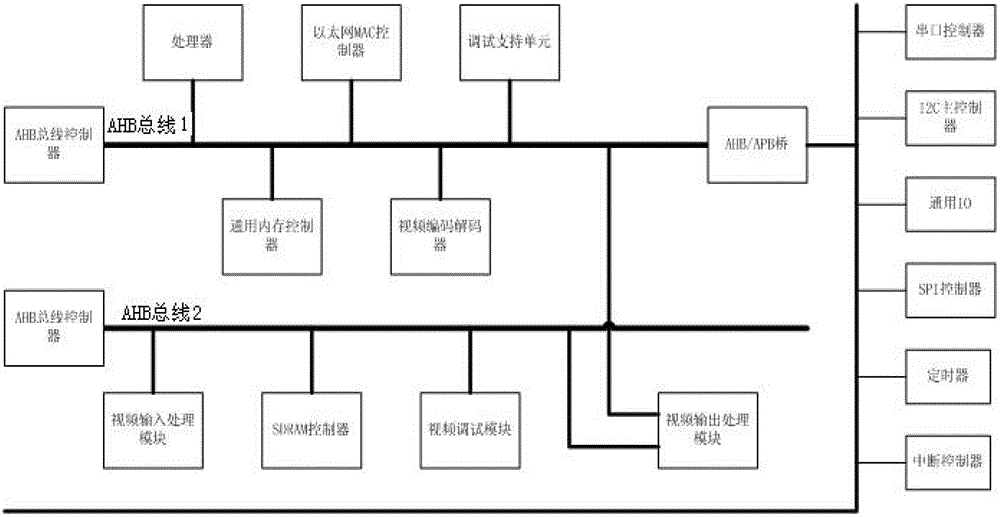

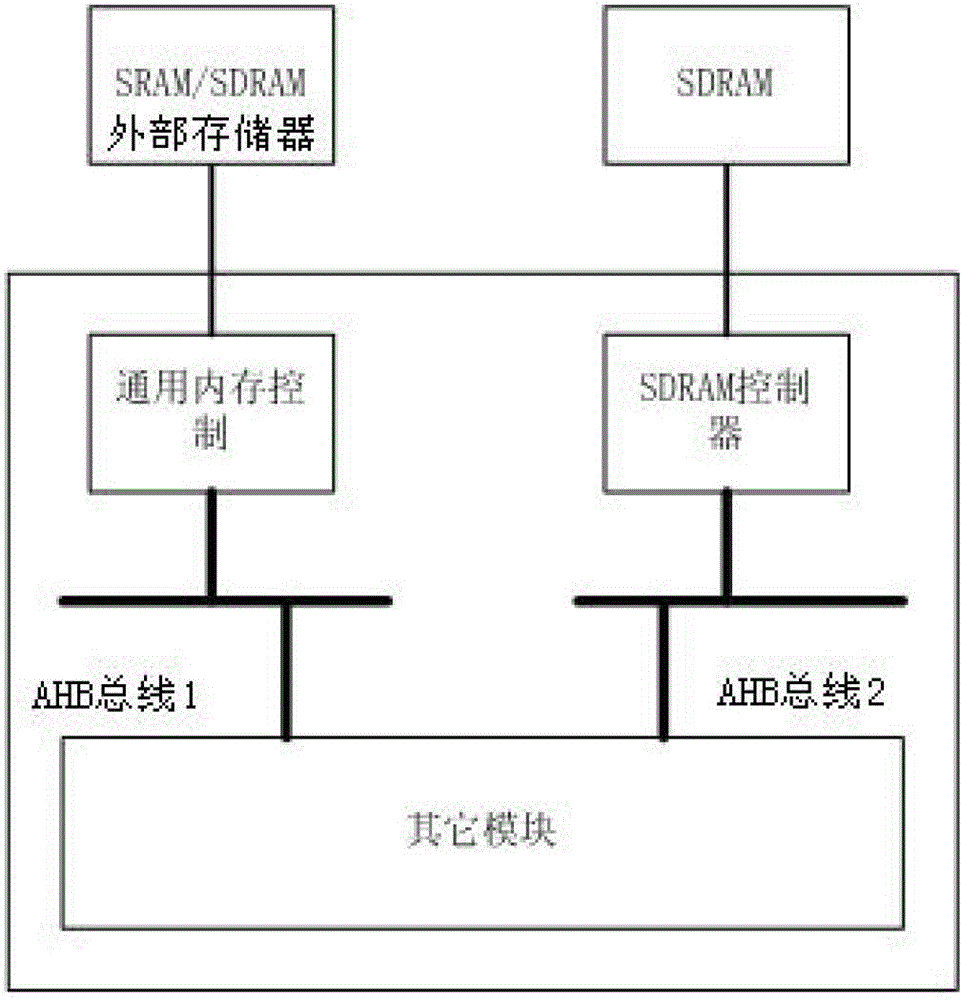

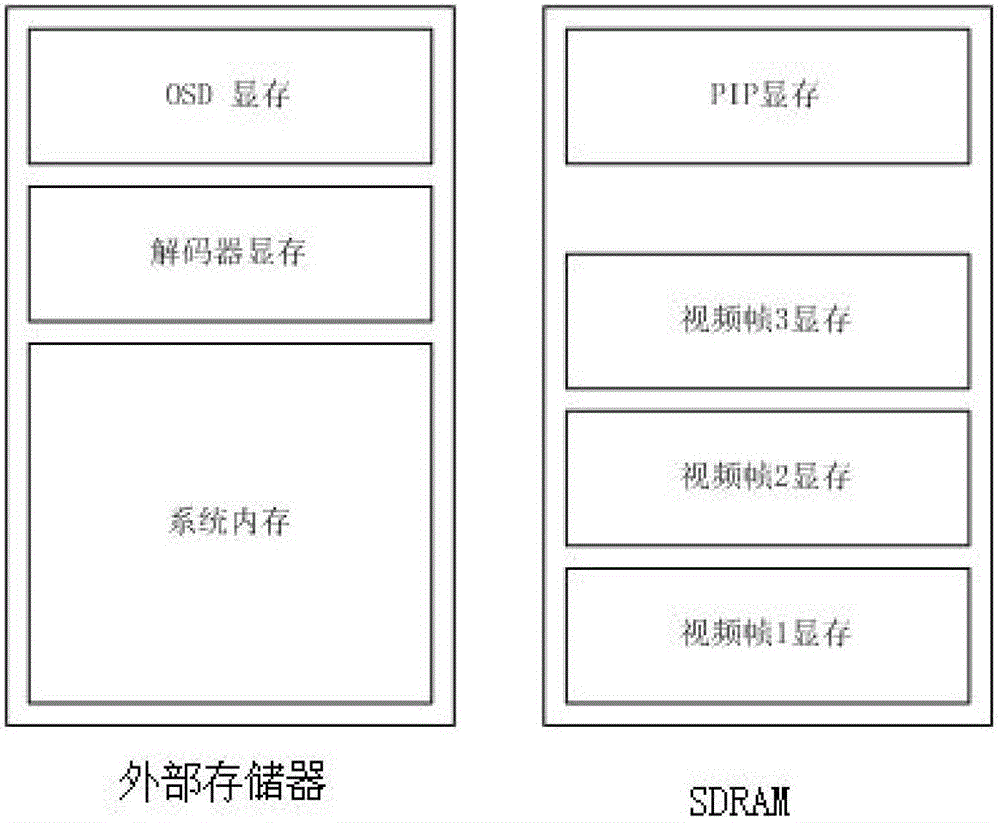

[0022] Such as figure 1 As shown, the video processing system-on-chip (SoC) of the double AHB bus of the present invention has two sets of AHB buses and a set of APB buses as internal high-speed data channels, and two sets of AHB buses are respectively connected to respective AHB bus controllers, AHB bus 1 Common high-performance processing units such as processors, Ethernet MAC controllers, debugging support units, general-purpose memory controllers, and video codecs are connected to it, as well as AHB / APB bridges. This set of buses focuses on general-purpose control functions; AHB bus 2 is connected to high-performance video units such as video input processing unit, SDRAM controller and video debugging unit. This bus focuses on high-speed video processing. In addition, the two sets of AHB buses are connected to the video output processing unit, which is the video ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com