Metal-oxide-semiconductor field-effect transistor layout structure

A technology of metal oxide half-field and layout structure, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., and can solve problems such as asymmetry of online circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Although the present invention may be embodied in different forms, what is shown in the drawings and described below is a preferred embodiment of the invention, and it is to be understood that what is disclosed herein is considered an example of the invention , and are not intended to limit the invention to the particular embodiments shown and / or described.

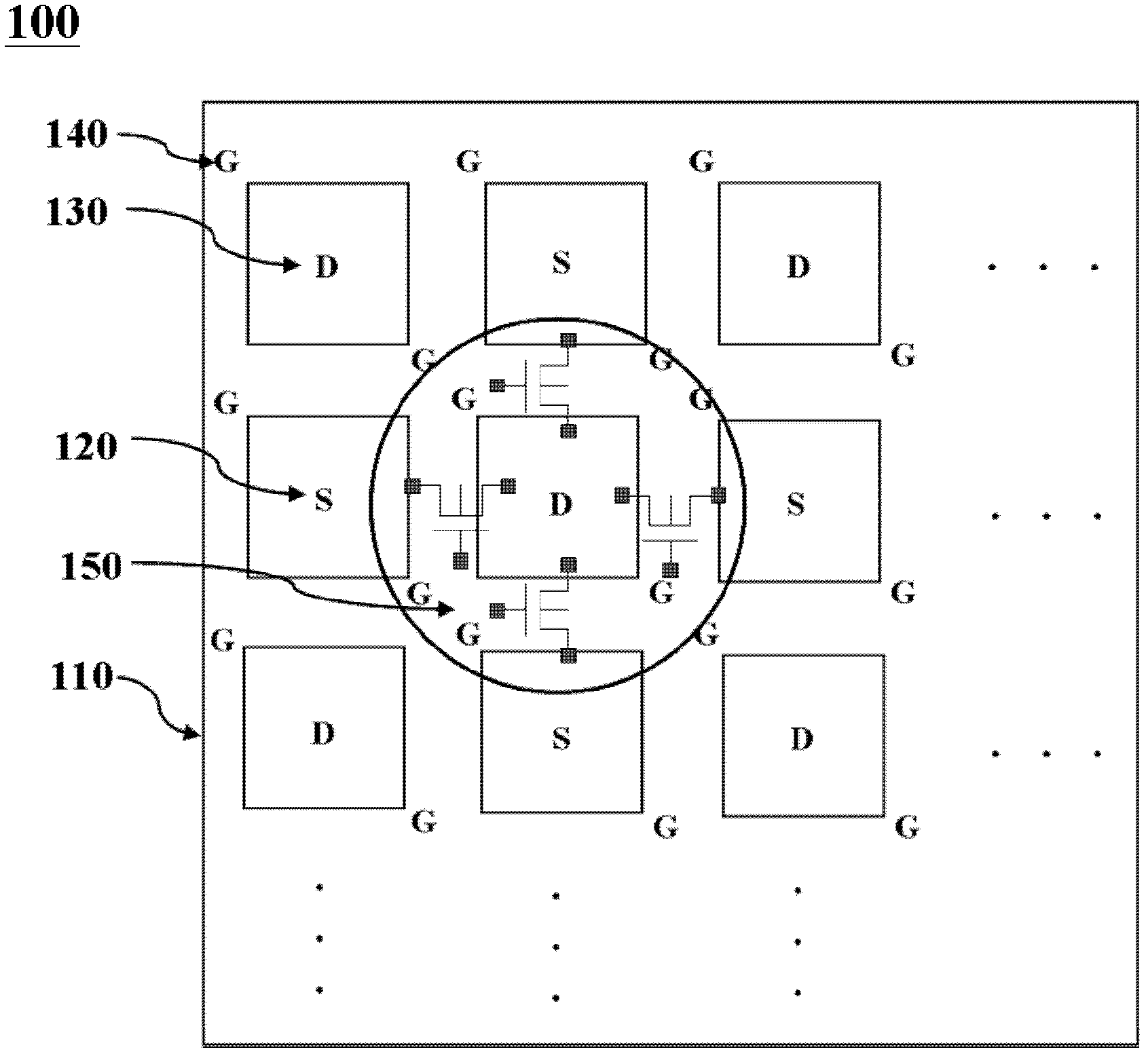

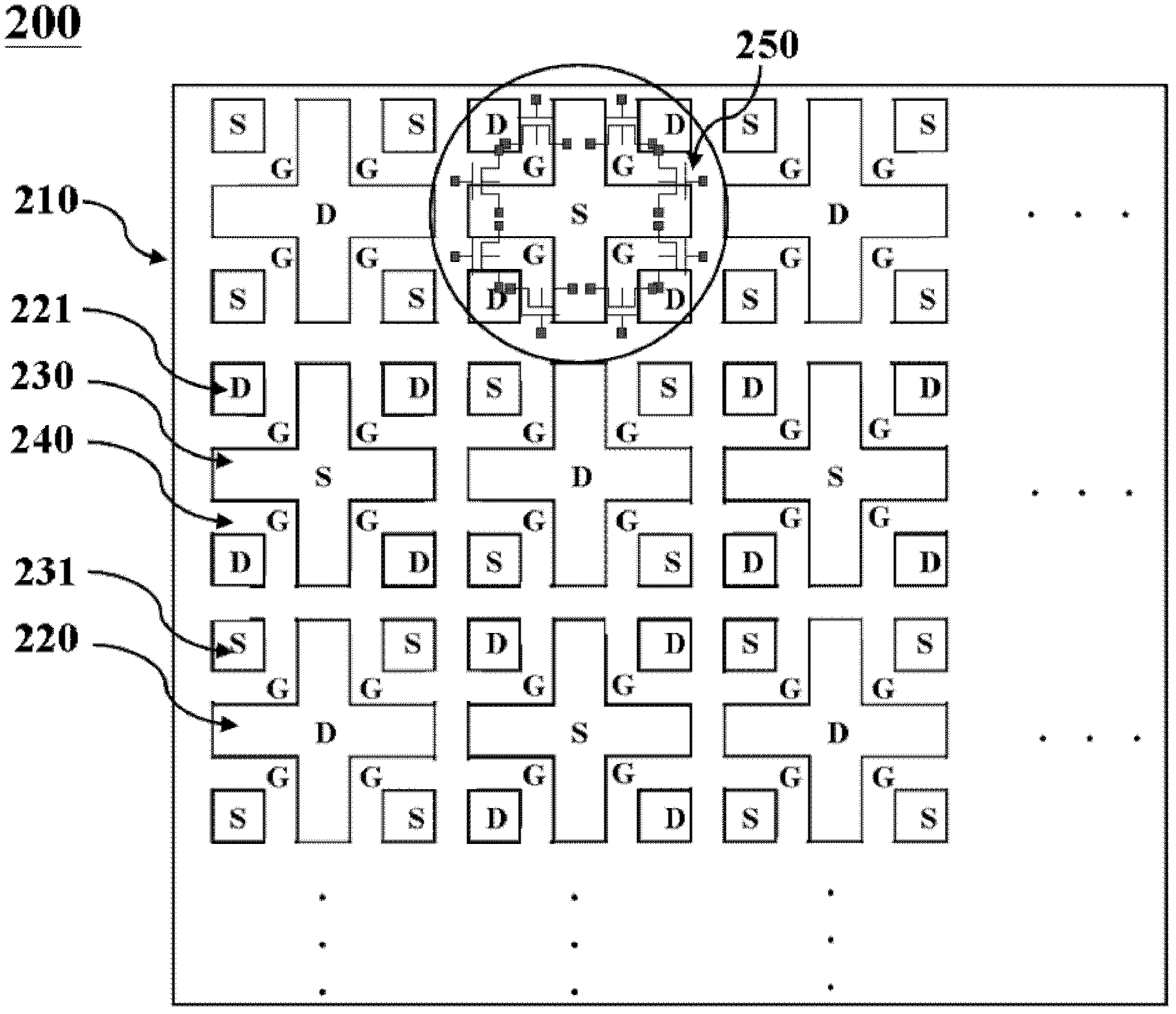

[0037] Please refer now Figure 2A , which shows a schematic diagram of the layout structure of a metal-oxide-semiconductor field-effect transistor with a higher effective channel width and a higher component density in the present invention. It includes: a substrate; a common drain region 220 with a cross pattern; at least two common source regions 231 with a grid pattern; a common source region 230 with a cross pattern; at least two common source regions 231 with a grid pattern a common drain region 221 ; and at least two common gate regions 240 . A common drain region 220 with a cross pattern is formed on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More