Synchronous phasor calculation method based on discrete Fourier transform (DFT) recursion of field programmable gate array (FPGA) hardware

A technology of synchronized phasors and calculation methods, applied in calculation, special data processing applications, instruments, etc., can solve the problems of unfavorable master station data processing, large calculation result error, high CPU load, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

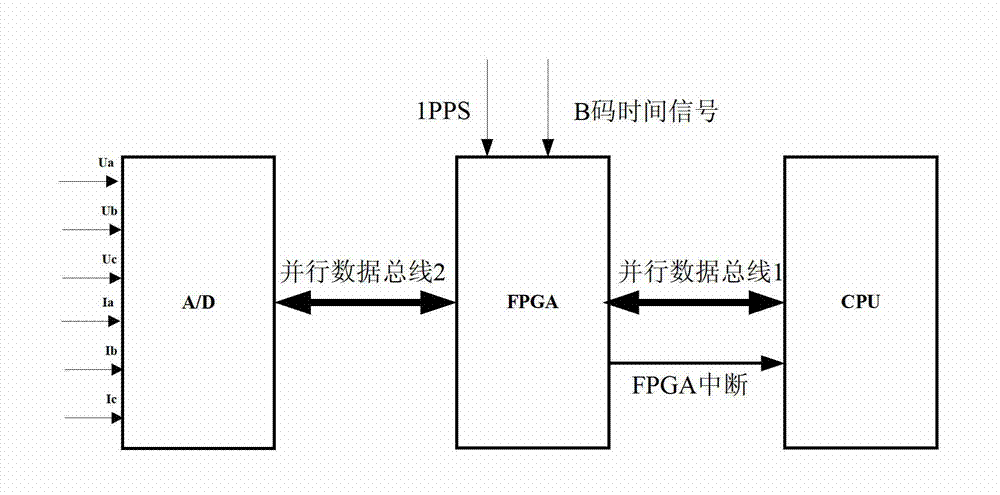

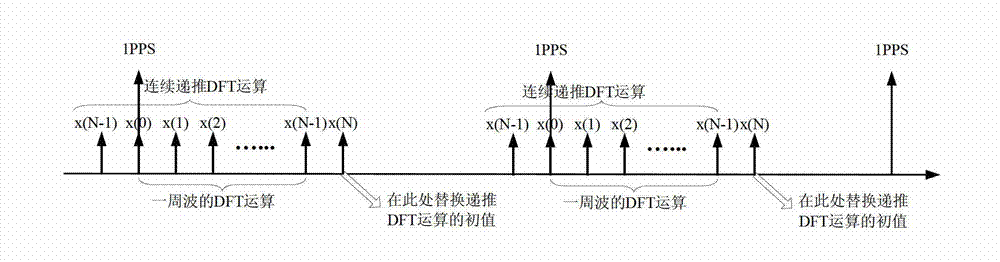

[0066] In order to make the technical means, creative features, objectives and effects of the present invention easy to understand, the following is attached figure 1 And figure 2 , Further explain the present invention.

[0067] See figure 1 with figure 2 , The present invention is a method for calculating synchronous phasor based on FPGA hardware DFT recursion, which is characterized in that the method includes the following steps:

[0068] (1) FPGA and CPU are connected by 32-bit or 64-bit parallel bus 1 in hardware. FPGA has an interrupt signal connected to the external interrupt pin of CPU. FPGA accesses standard clock 1PPS signal and B code time signal, FPGA passes Parallel bus 2 controls the AD chip;

[0069] (2) Define sampling configuration register (CONFIG_REG), sampling buffer register (DATA_REG), DFT coefficient original register (DFT_COEF), DFT result buffer register (DFT_REG) on the FPGA side;

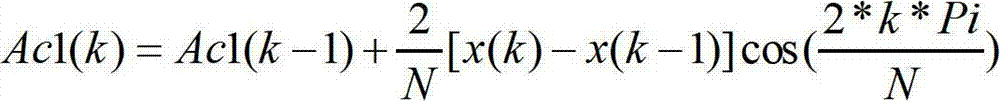

[0070] (3) The CPU writes the predefined DFT coefficients into the prede...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More