A Three-Order Symptom Test Method Combined with Parity Check

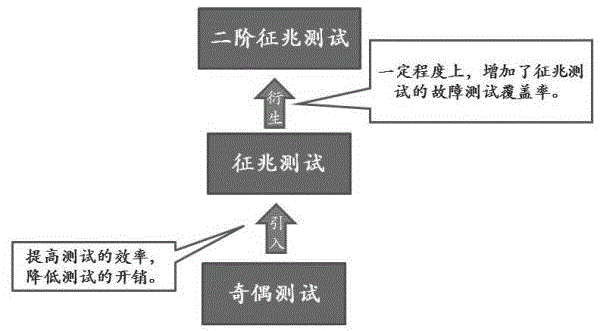

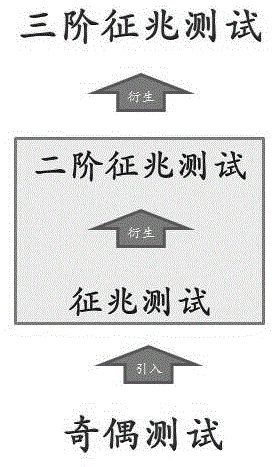

A parity check and symptom technology, applied in the field of computer hardware fault testing, can solve the problems of complex circuit fault testing, complex circuit design, and difficulty in circuit fault detection, so as to reduce resources and time overhead and reduce testing. overhead, the effect of improving fault coverage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0066] In this embodiment, the method of the third-order symptom test combined with parity check is based on Microsoftvisualstudio2008, and is implemented with C++ object-oriented language as the programming language.

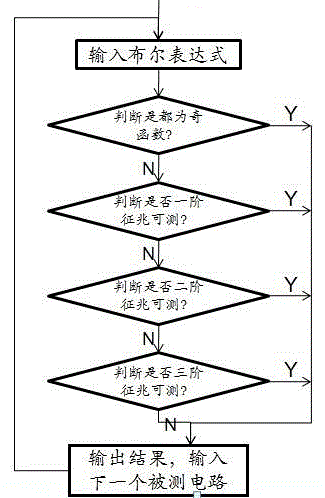

[0067] image 3 As shown, the method for the third-order symptom test in combination with the parity check comprises the following steps, and is characterized in that,

[0068] Step 1, read the corresponding Boolean expression of the circuit from the text;

[0069] Step 2, analyze Boolean expressions, generate corresponding intermediate data, and perform parity check;

[0070] Included in said step 2, the Boolean expression for the circuit, replacing the general exhaustive (input 2 n Combination) method, disjunctive, and then get disjunctive normal form (DNF). The parity of the circuit is judged according to the obtained disjunction paradigm.

[0071] Step 3 is based on the parity check, and according to the intermediate data generated accordingly, the firs...

Embodiment 2

[0085] This embodiment is basically the same as Embodiment 1, and the special features are as follows:

[0086] The boolean expression: . First perform a parity check on it to get:

[0087]

[0088] is an odd function, therefore, the circuit can be obtainedN For symptom-testable circuits, use first-order symptom testing for fault detection. In this way, pre-checking the circuit using the parity check can effectively reduce the calculation amount of the test and the test time.

Embodiment 3

[0090] This embodiment is basically the same as Embodiment 1, and the special features are as follows:

[0091] The boolean expression:

[0092] a) According to the definition of parity test, it can be obtained:

[0093]

[0094] It can be obtained that the circuit is an even function, so it is necessary to continue to make a testable judgment on the circuit.

[0095] b) According to the definition of the first-order symptom test, variables can be extracted:

[0096]

[0097] At the same time, you can get:

[0098] Unpredictable for first-order symptoms;

[0099] c) Carry out second-order symptom judgment on the circuit and extract variables:

[0100]

[0101] At the same time, you can get: ,

[0102] The circuit is still untestable.

[0103] d) After the third-order symptom judgment of the circuit, it can be obtained

[0104]

[0105] At the same time, after calculation, we get:

[0106]

[0107] At this time, after using the third-order symptom j...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More