Patents

Literature

32results about How to "Reduce testing overhead" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

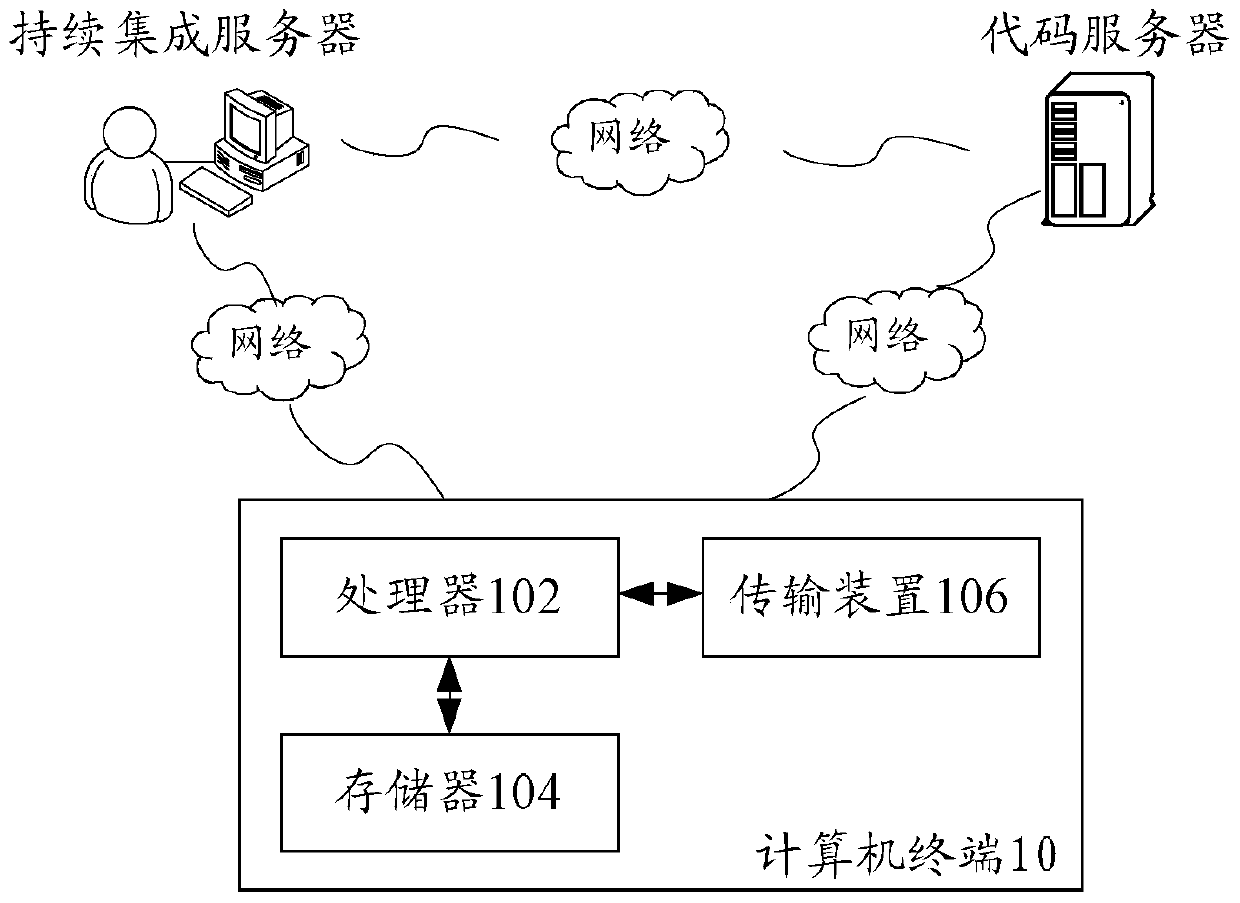

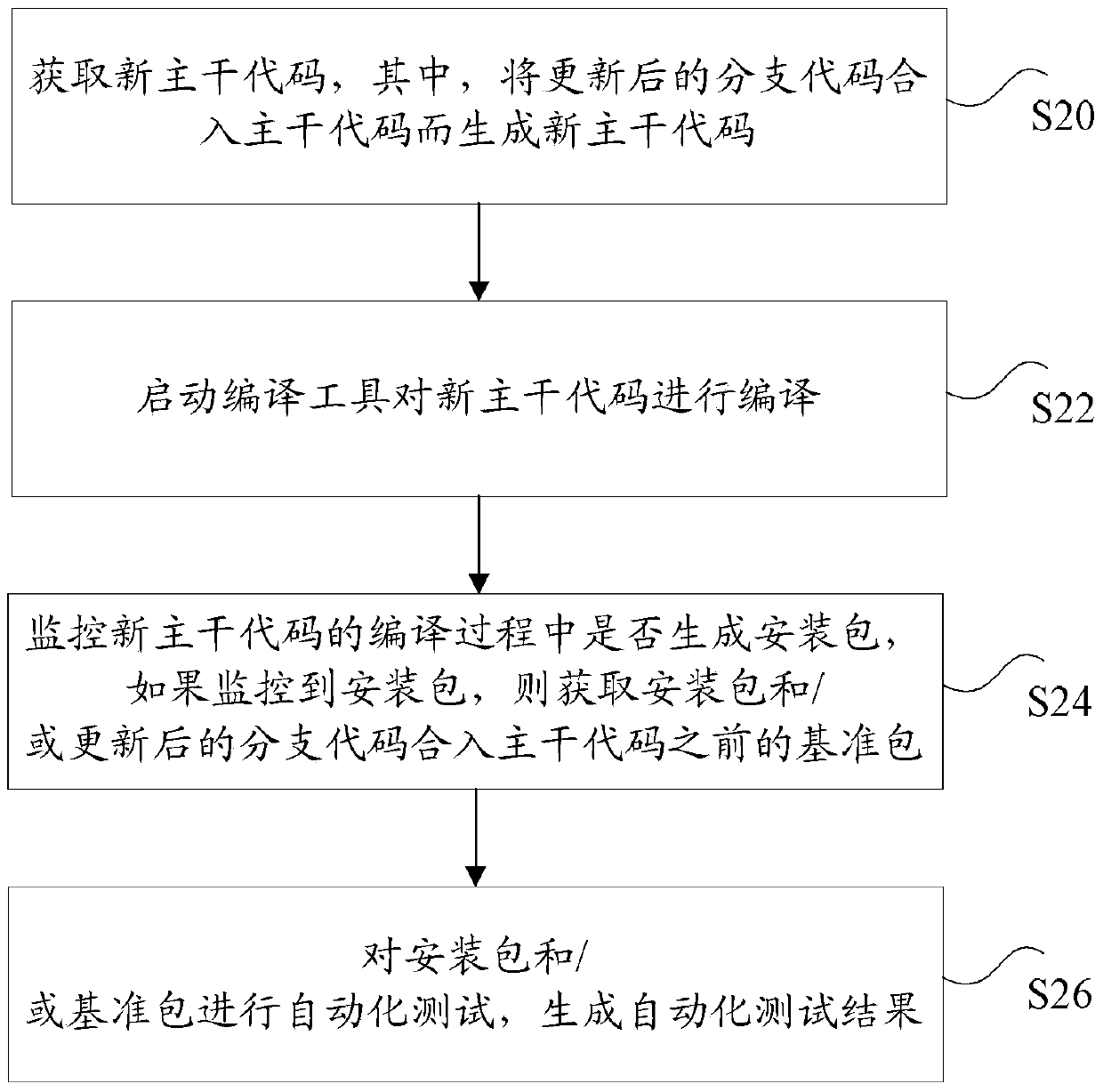

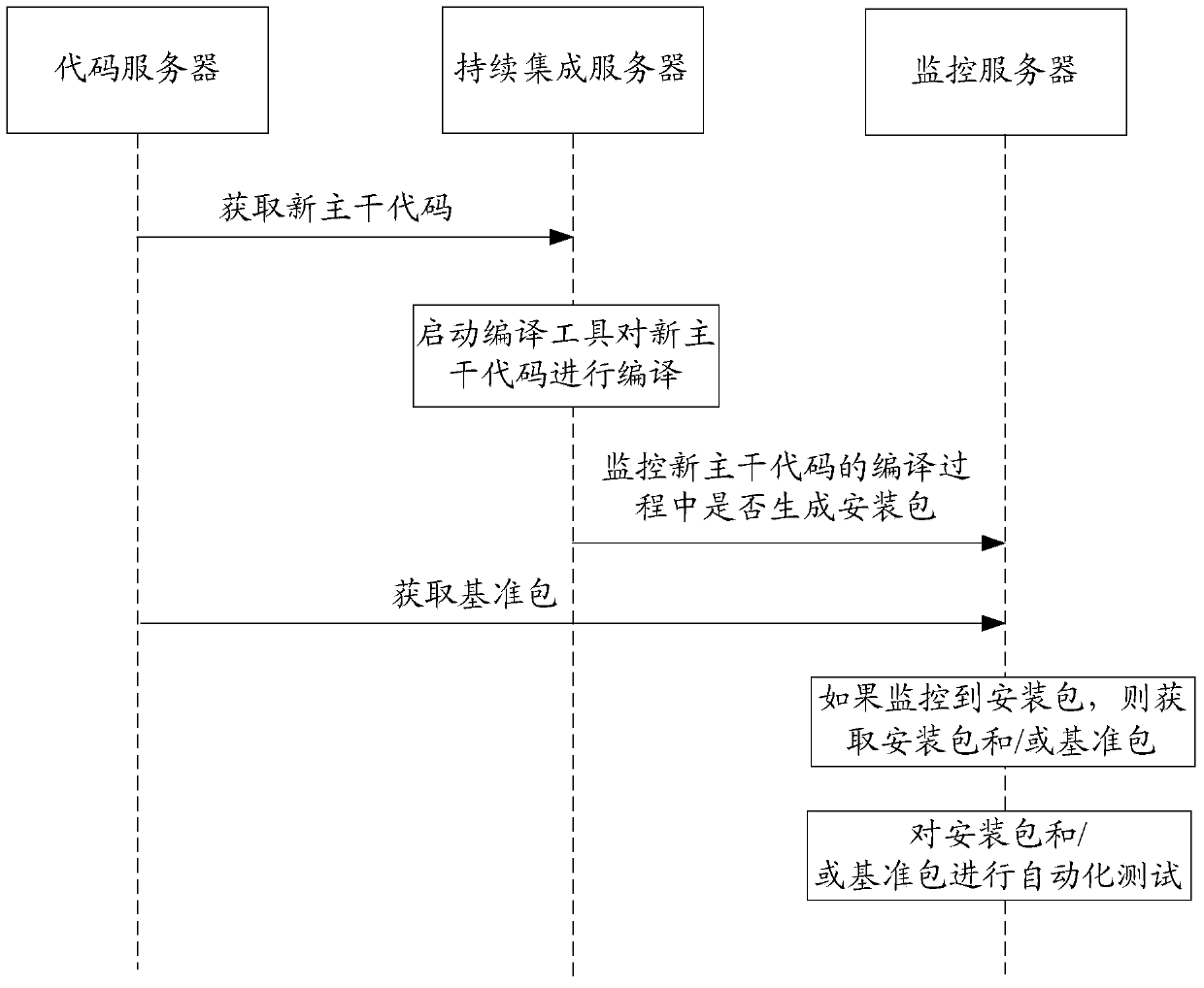

Method and apparatus for test in joint development mode

ActiveCN105302716ATest accurateReduce testing overheadSoftware testing/debuggingTest efficiencySoftware engineering

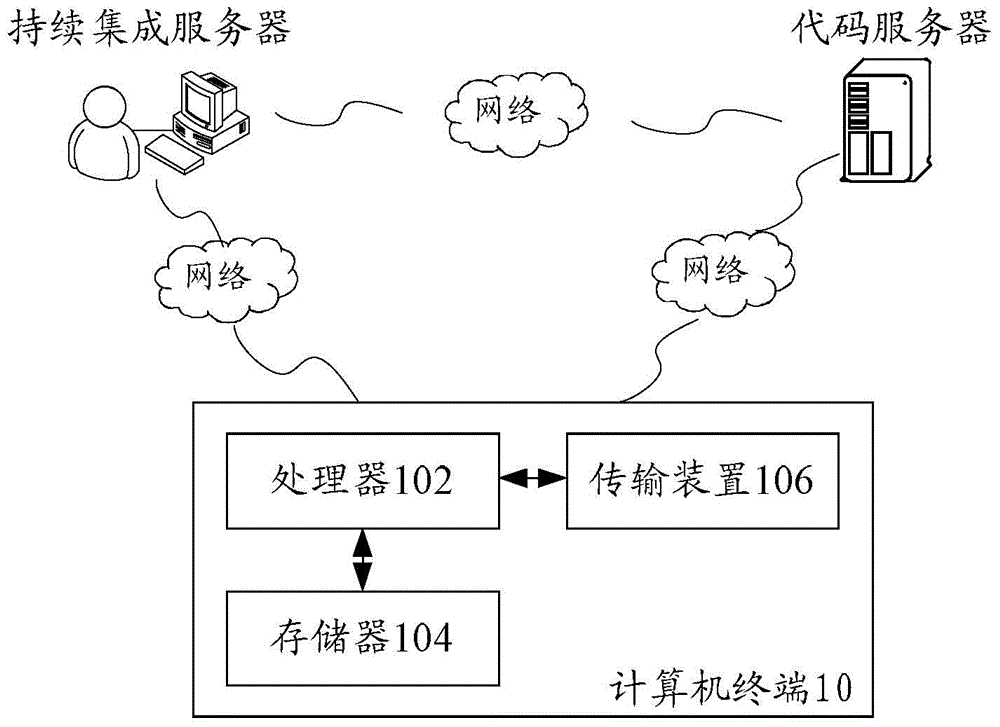

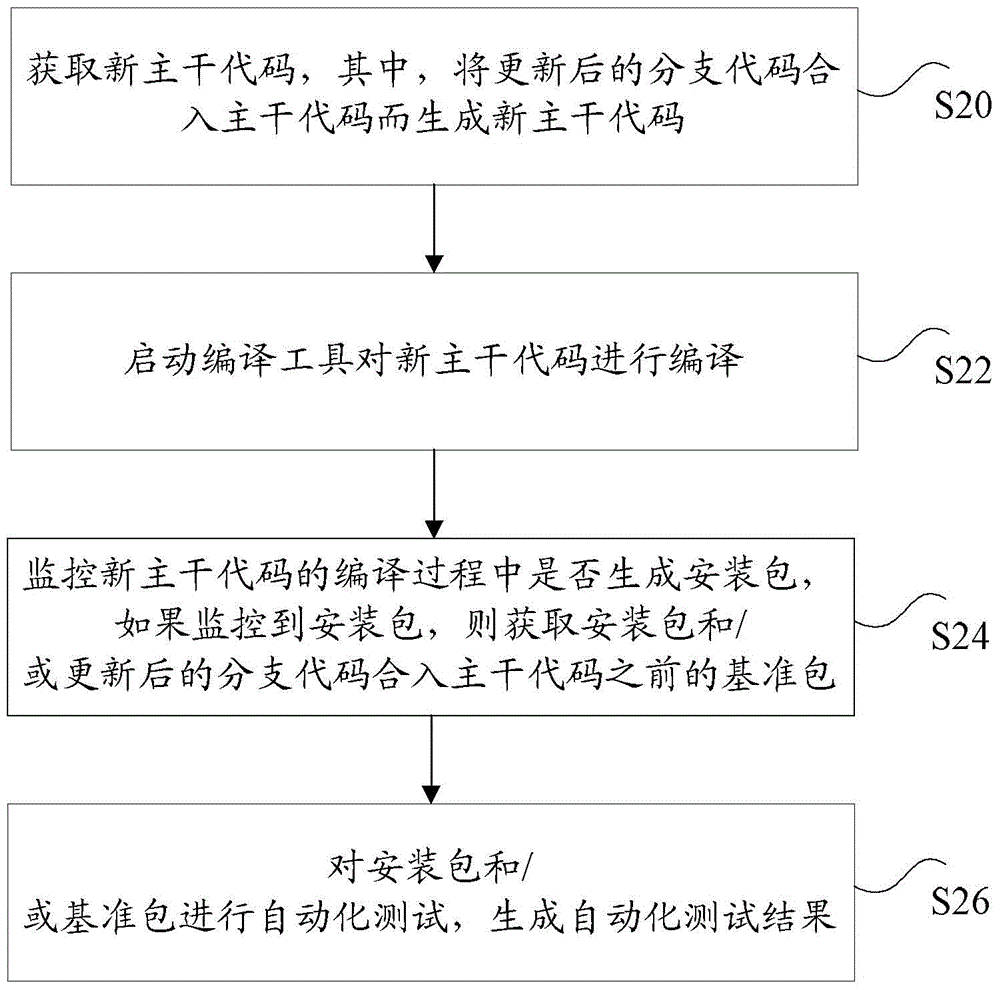

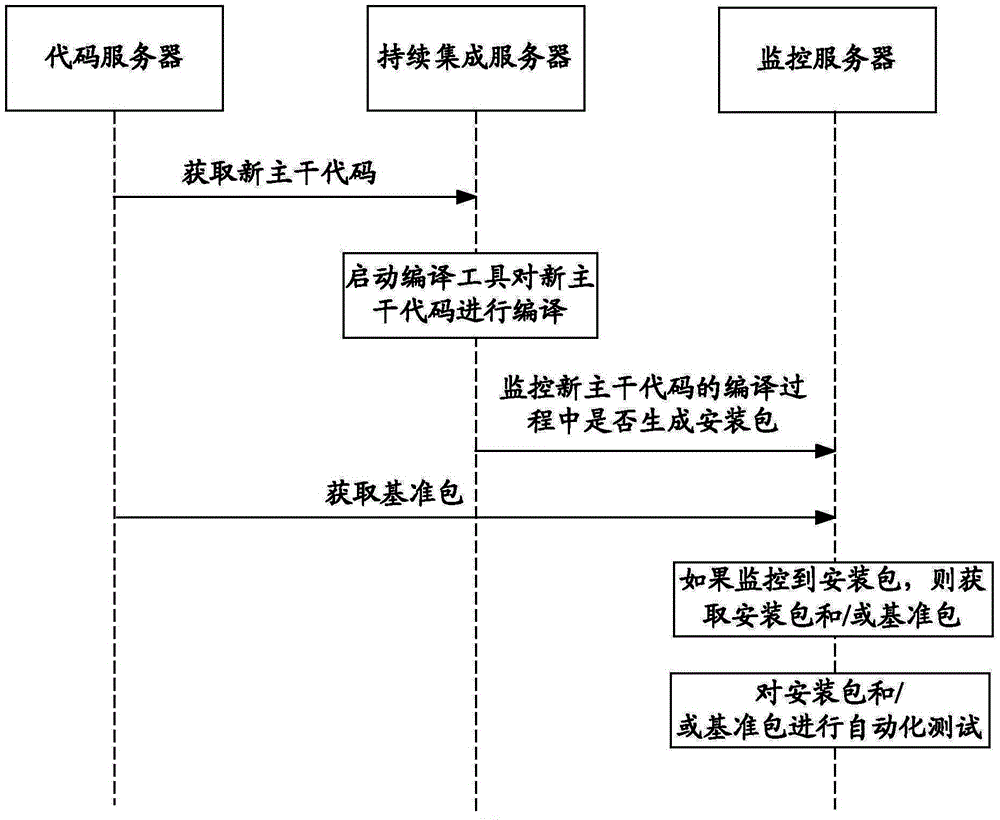

The invention discloses a method and an apparatus for a test in a joint development mode. The method comprises: obtaining a new main code, wherein updated branch codes are combined into a main code to generate the new main code; starting a compiling tool to compile the new main code; monitoring whether an installation package is generated in a compiling process of the new main code or not, and if the installation package is monitored, obtaining the installation package and / or a reference package before the updated branch codes are combined into the main code; and performing an automated test on the installation package and / or the reference package to generate an automated test result. According to the method and the apparatus, the technical problems of inaccurate test result and low test efficiency caused by adoption of a timed test method in a software development mode of combining branch codes with a main code in the prior art are solved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

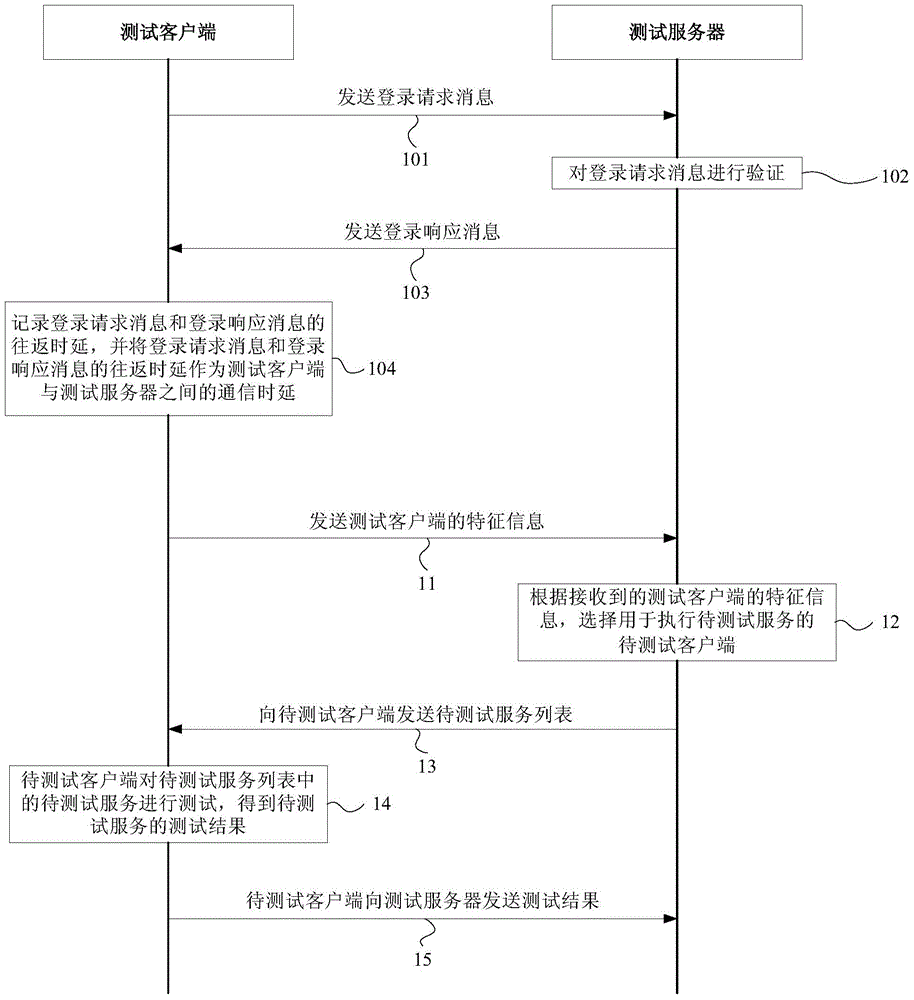

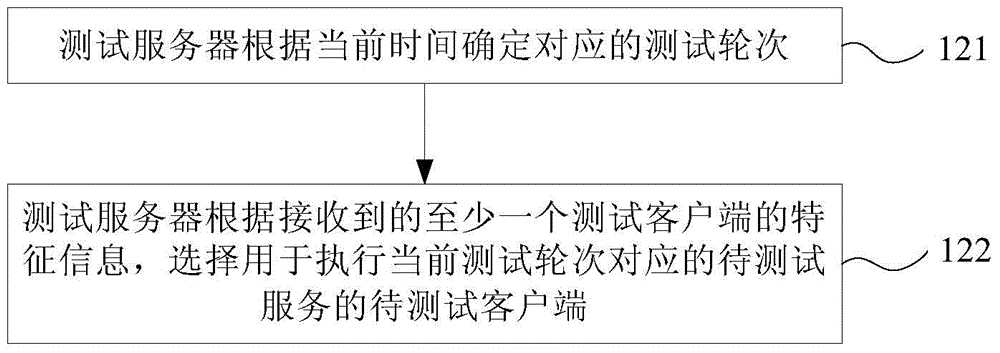

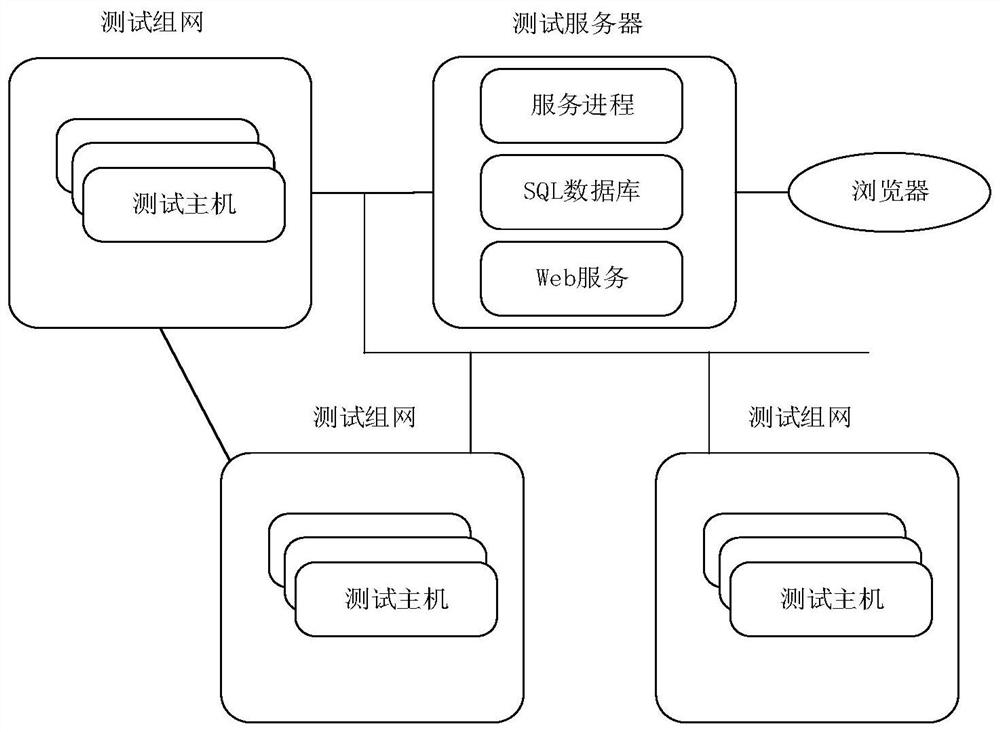

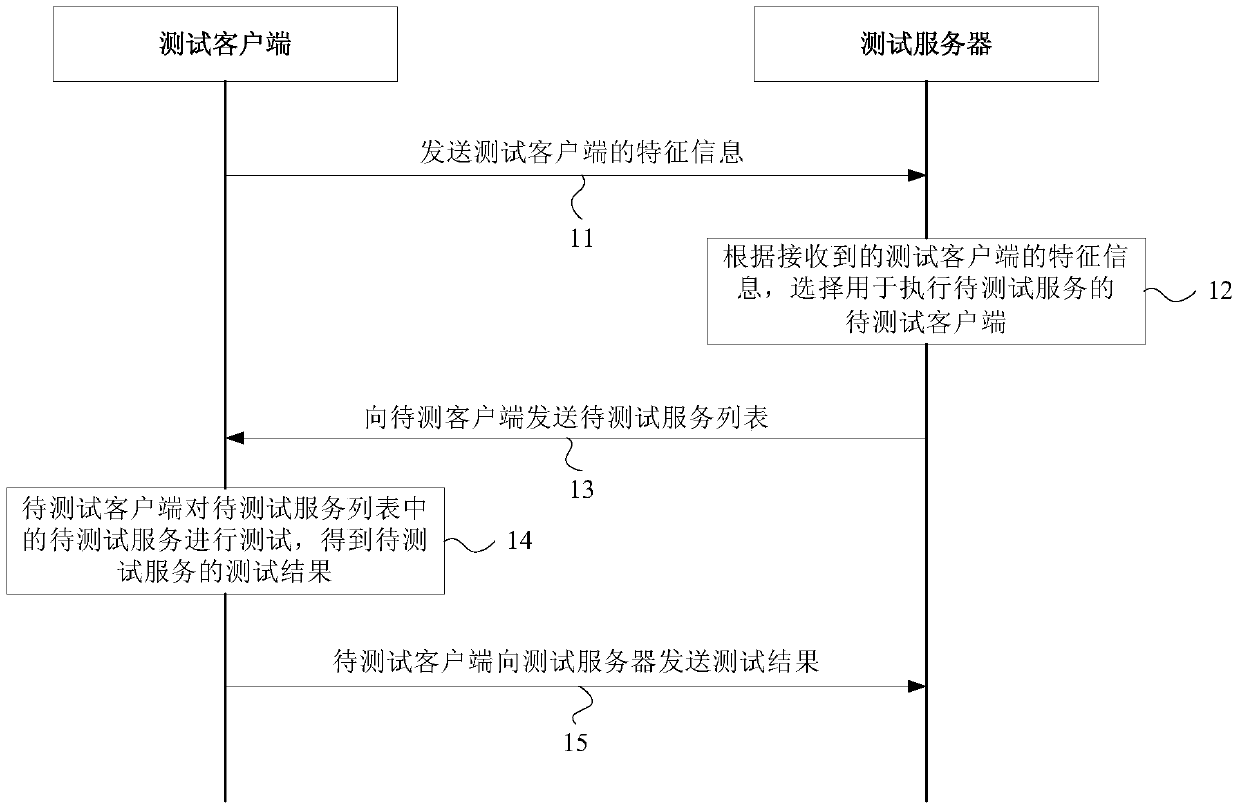

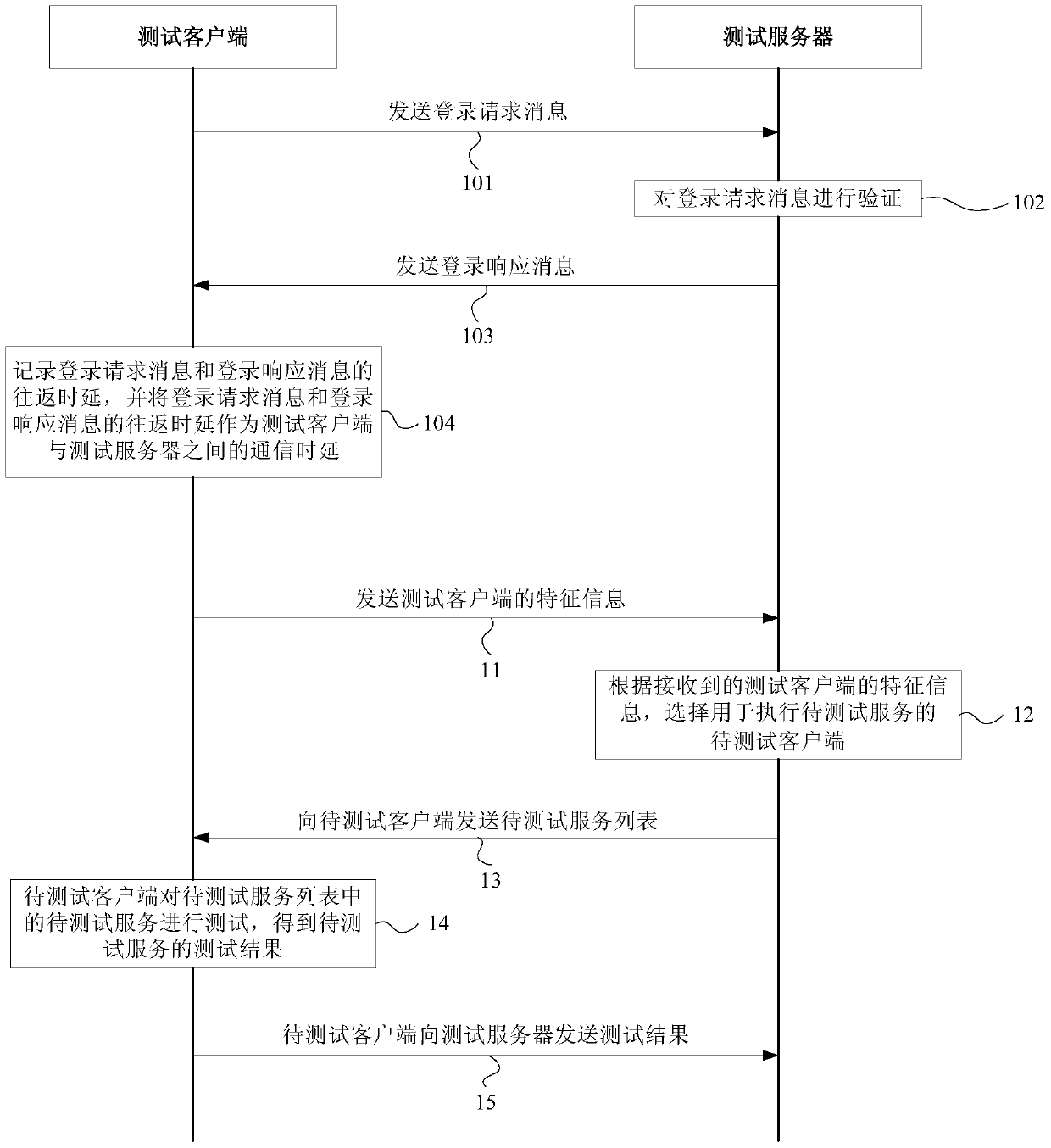

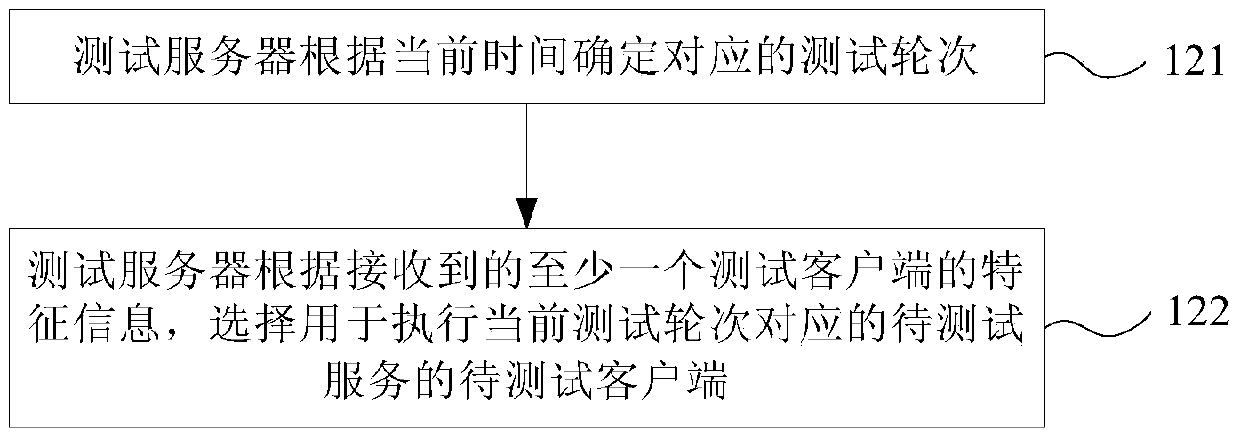

Crowdsourcing test method

ActiveCN104579854AThe test effect is goodReduce testing overheadData switching networksCrowdsourced testingSoftware engineering

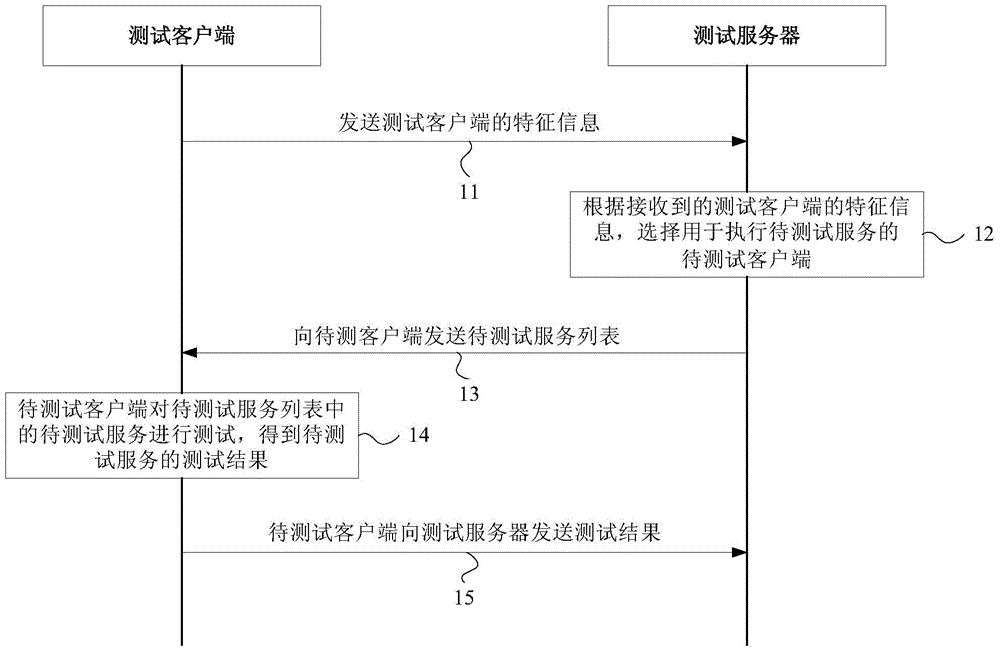

The invention provides a crowdsourcing test method. The crowdsourcing test method comprises the following steps: a test client side is used for sending characteristic information of the test client side to a test server; the test server is used for selecting a to-be-tested client side used for executing to-be-tested service according to the received characteristic information of at least one test client side; the test server is used for sending a to-be-tested service list to the to-be-tested client side; the to-be-tested client side is used for testing the to-be-tested service in the to-be-tested service list to obtain a test result of the to-be-tested service; and finally, the to-be-rested client side is used for sending the test result to the test server. The crowdsourcing test method used for testing network application service is used for remarkably improving the test result and effectively reducing the test cost.

Owner:BEIHANG UNIV

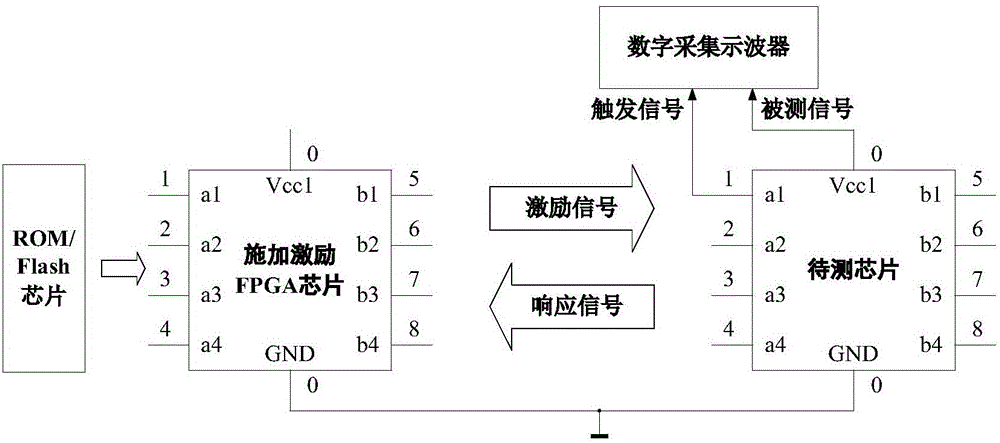

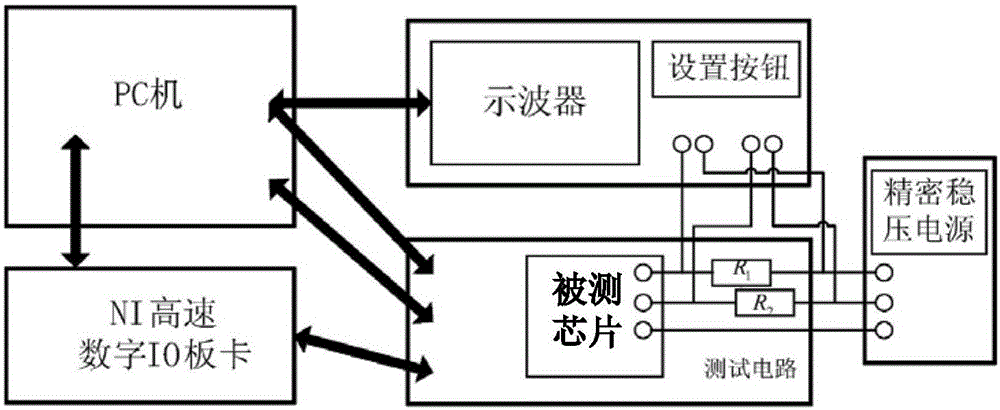

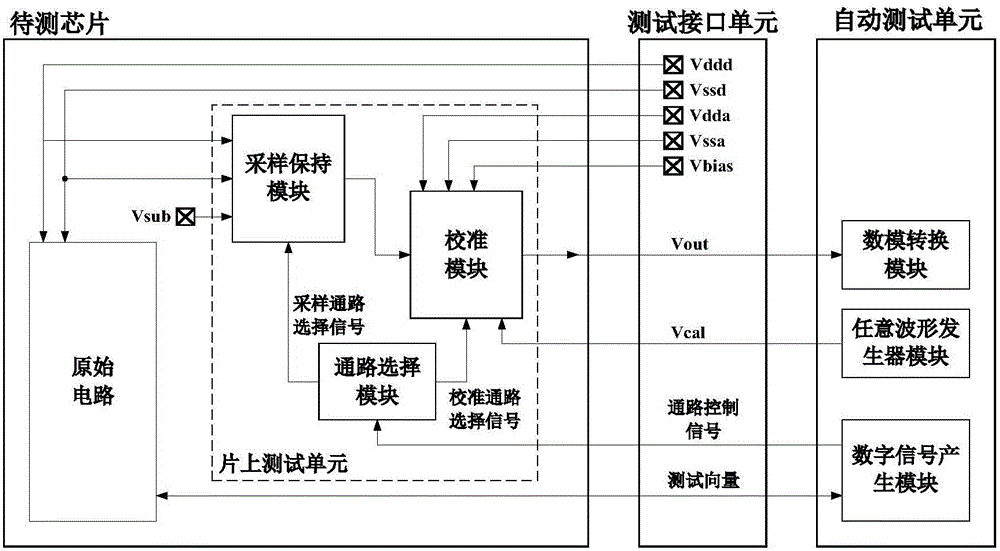

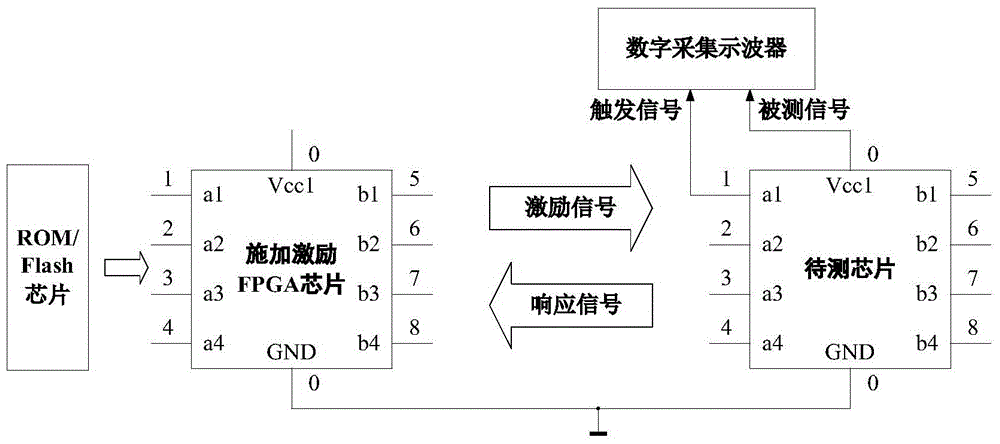

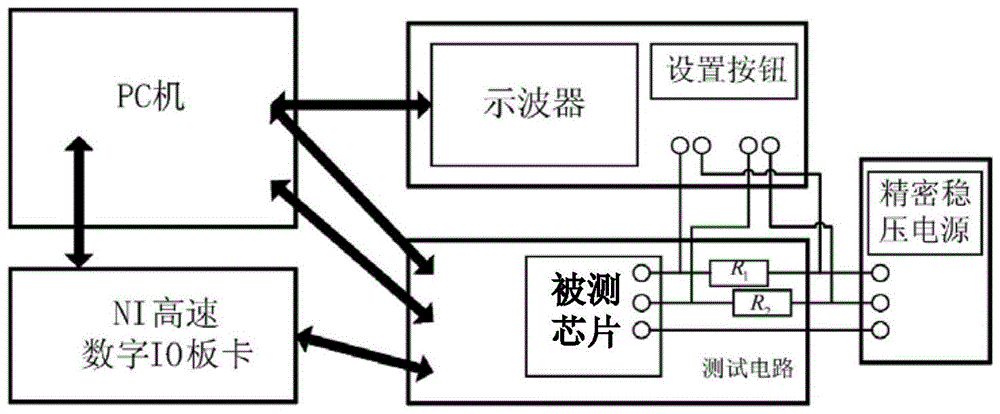

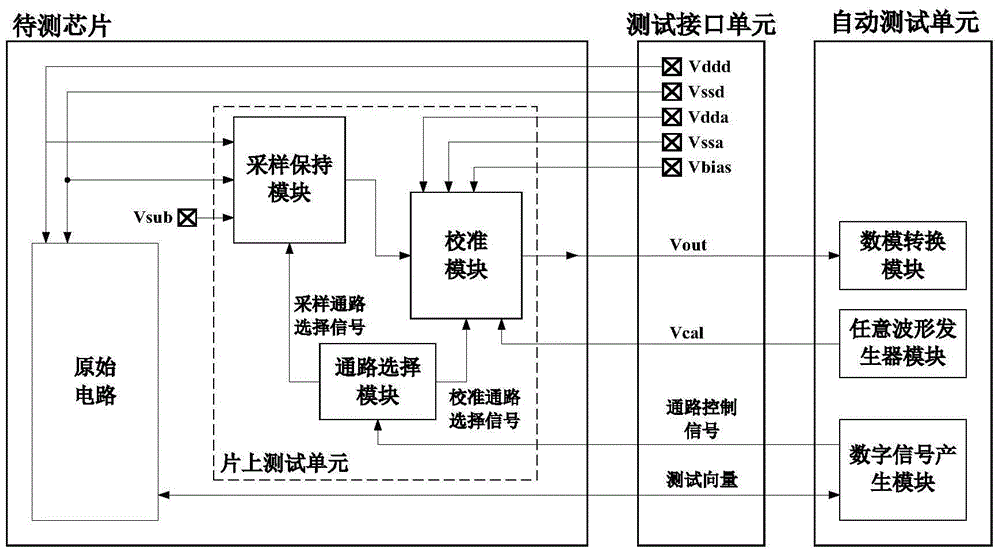

Integrated circuit test system and method

ActiveCN105116317AOvercome the problems of slow test speed, low efficiency and high test overheadReduce testing overheadElectrical testingTest efficiencyTest flow

The present invention relates to an integrated circuit test system. The integrated circuit test system comprises an automatic test unit, a test interface unit and an on-chip test unit embedded in a to-be-tested chip, the on-chip test unit comprises an access selection module, a sampling holding module and a calibration module, and the to-be-tested chip is connected with the automatic test unit via the test interface unit. The automatic test unit generates a test vector and an access control signal and transmits to the test interface unit, the access selection module receives the access control signal adapted by the test interface unit and outputs an access selection signal to the sampling holding module or the calibration module based on the access control signal. According to the present invention, the test of the high speed (GHz) to-be-tested chip is realized, in addition, by just needing the test interface unit to finish the electrical connection of the automatic test unit and the to-be-tested chip, the integration of the to-be-tested chip and a conventional integrated circuit test flow is realized, thereby improving the test efficiency and reducing the test cost.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

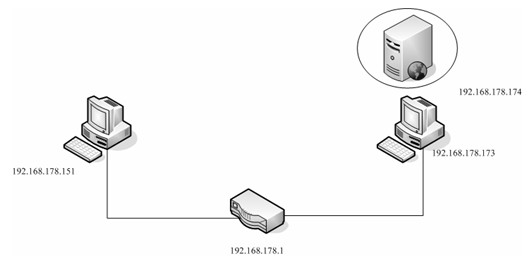

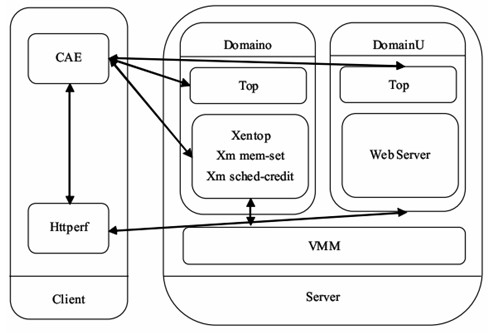

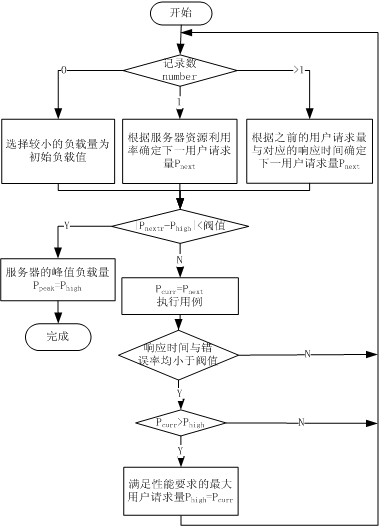

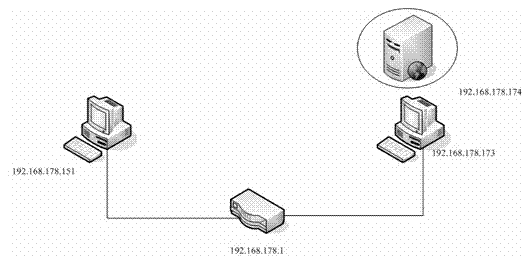

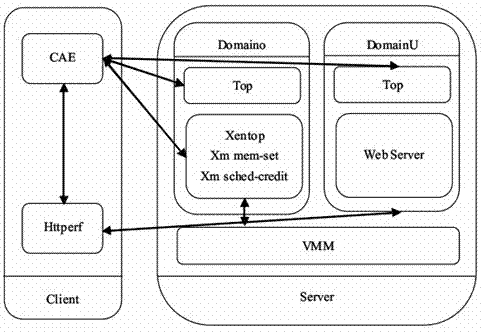

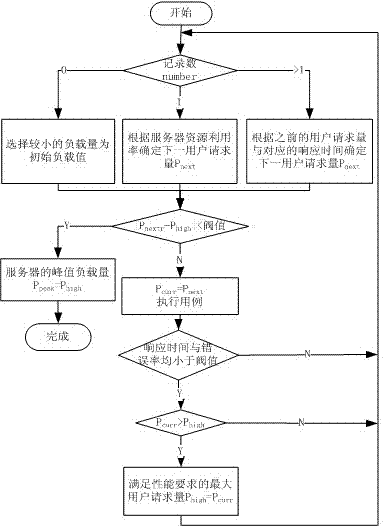

Method for determining performance of Web server

The invention relates to a method for determining the performance of a Web server. Performance evaluation cannot be performed on a real server by the conventional method. In the method provided by the invention, a peak load of the web server is determined by monitoring the usage rate of internal memories and central processing units (CPU) of the Web server and a host and the response time and an error rate of a user request and by analyzing a relationship between the usage rates and a user request capacity, a relationship between the response time and the user request capacity, and a relationship between the error rate and the user request capacity, so that the performance of the Web server is evaluated rapidly and correctly, and a correct and reliable basis for using hardware resources reasonably and effectively and meeting a user requirement is provided. By the method, the maximum real utilization ratio of a proper reference resource is selected as a reference point to calculate thenext user request capacity, and the request capacity obtained through calculation is smaller than the peak load capacity of the server no matter whether the resource is a performance bottleneck of the Web server.

Owner:HANGZHOU DIANZI UNIV

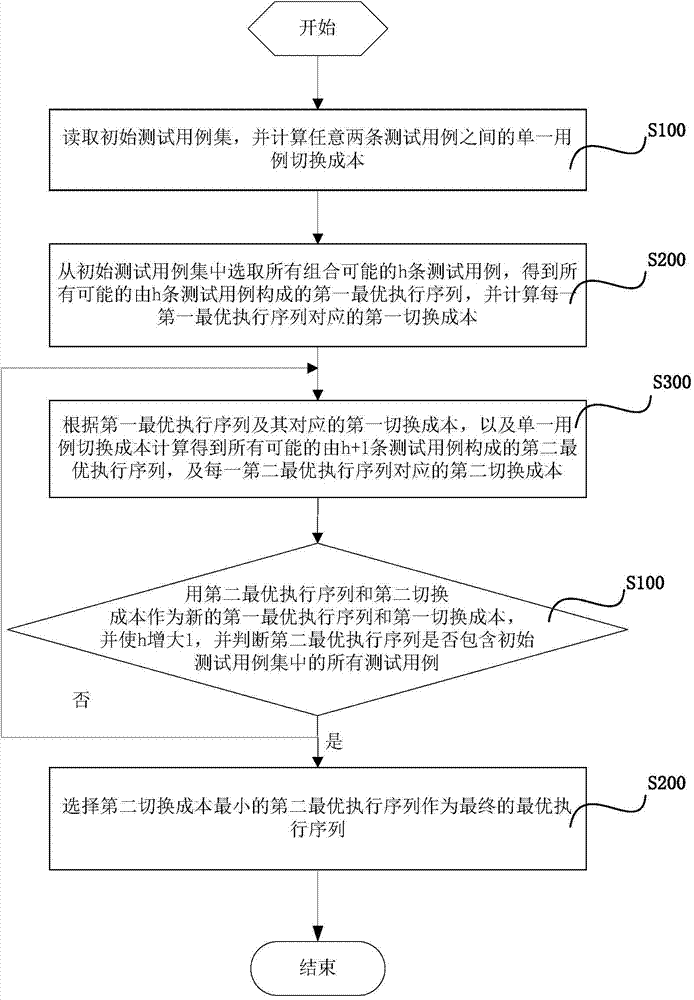

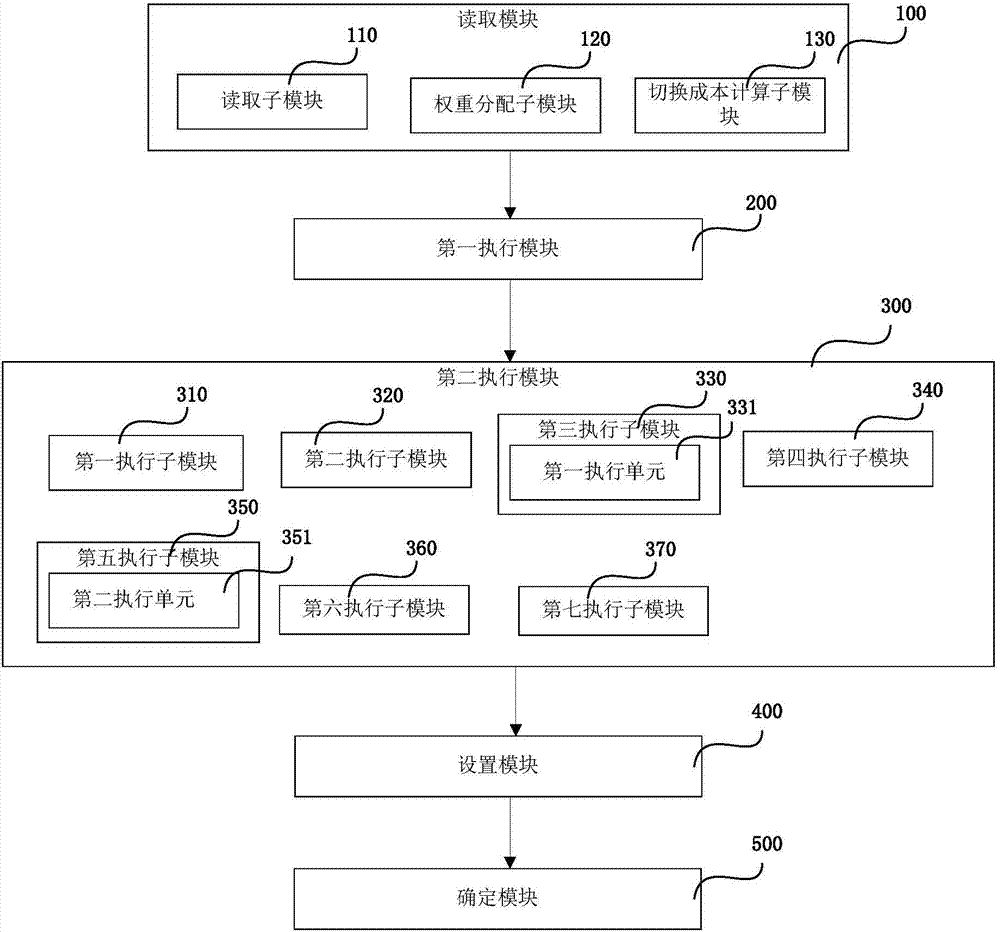

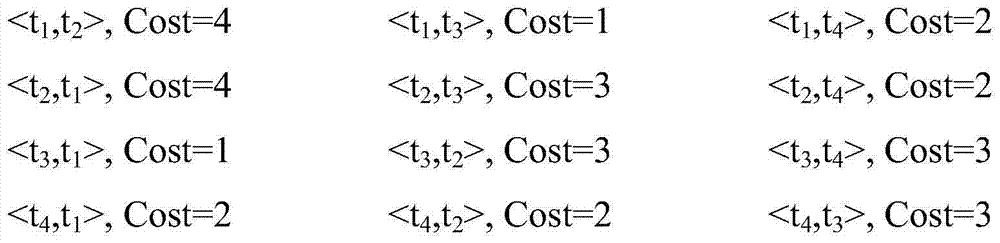

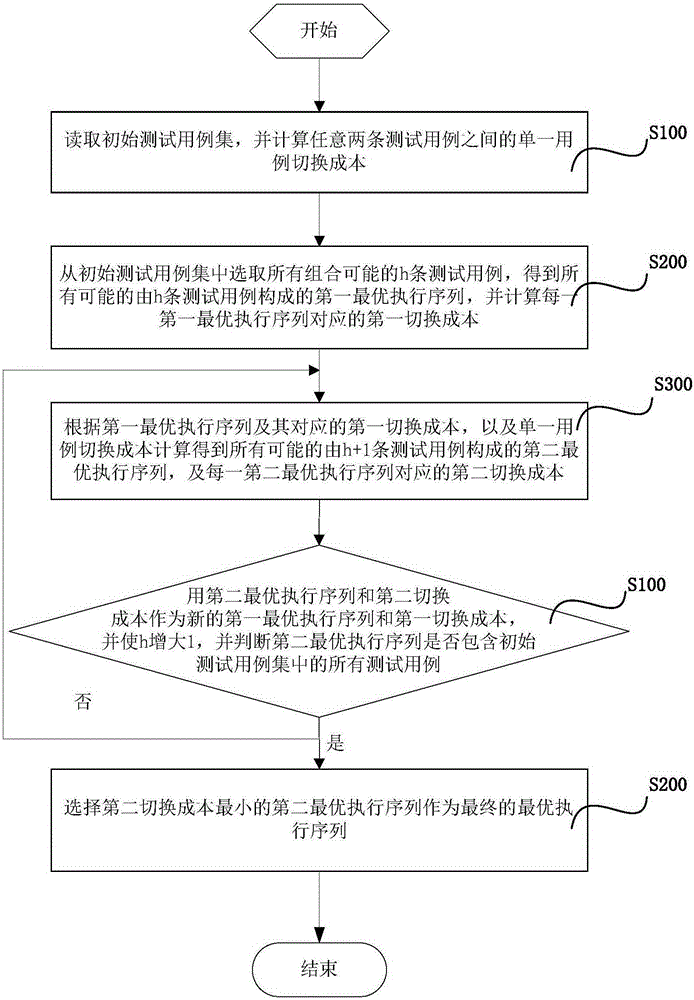

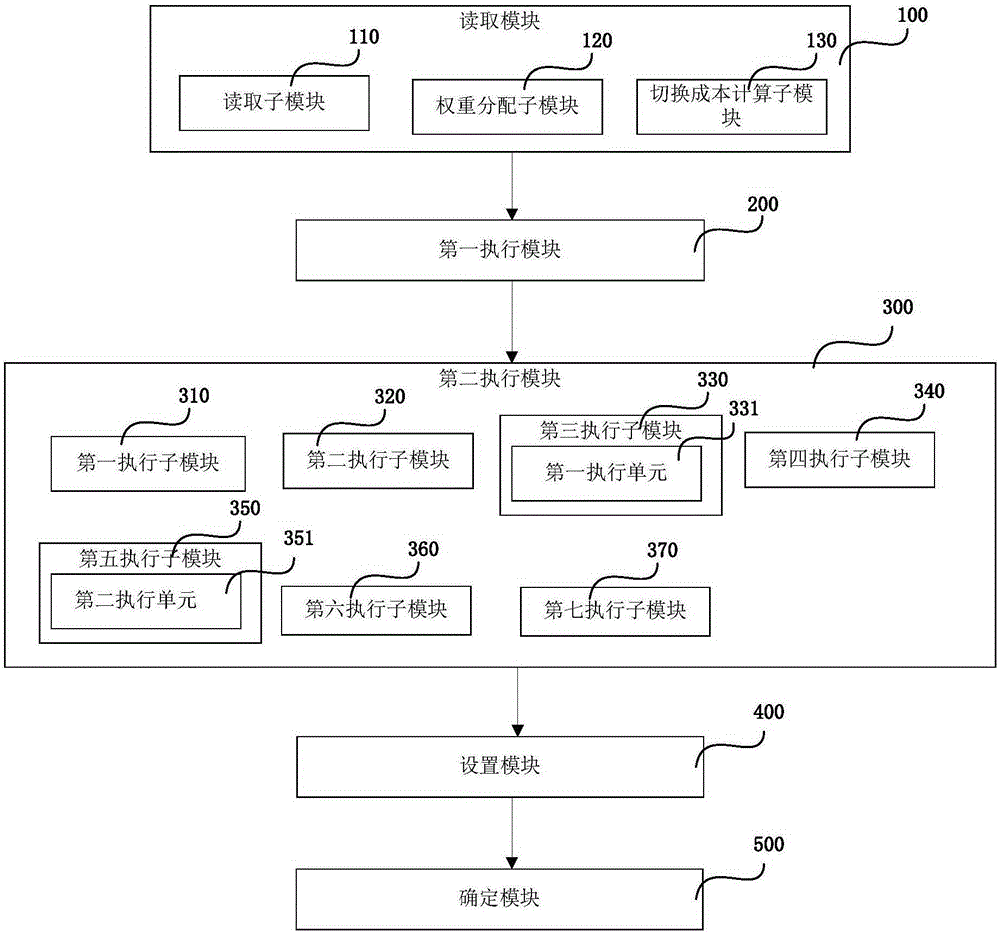

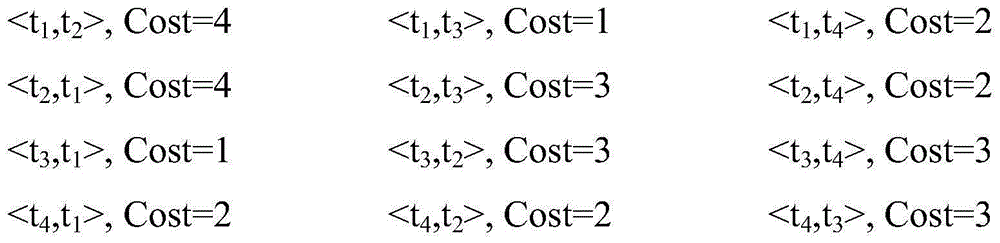

Method and system for determining execution sequence of test case suite

InactiveCN103577325AMinimal reconfiguration timesSmall test switching costsSoftware testing/debuggingComputer architectureTest suite

The invention discloses a method and a system for determining an execution sequence of a test case suite. The method comprises the steps as follows: the single case switching cost between any two test cases in an initial test case suite is calculated; h test cases with all combination possibilities are selected from the initial test case suite, and all the possible first optimum execution sequences and first switching costs which are formed by the h test cases are obtained; according to the first switching costs and the single case switching cost, all possible second optimum execution sequences and second switching costs which are formed by h+1 test cases are calculated and obtained; the second optimum execution sequences and the second switching costs are taken as the first optimum execution sequences and the first switching costs respectively, h is increased by 1, a previous step is returned until the second optimum execution sequences comprise all test cases; and a second optimum execution sequence with the smallest second switching cost is taken as the optimum execution sequence, so that minimum reconfiguration times of parameters in a test can be realized, and the expenditure is reduced.

Owner:NANJING UNIV

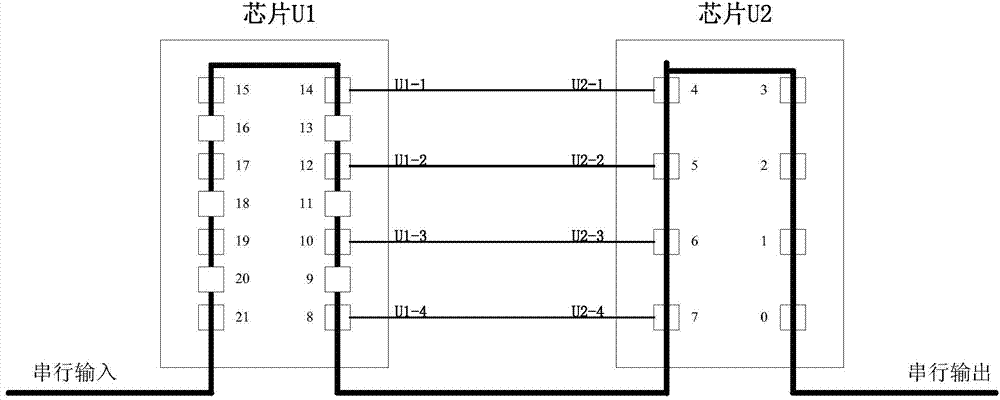

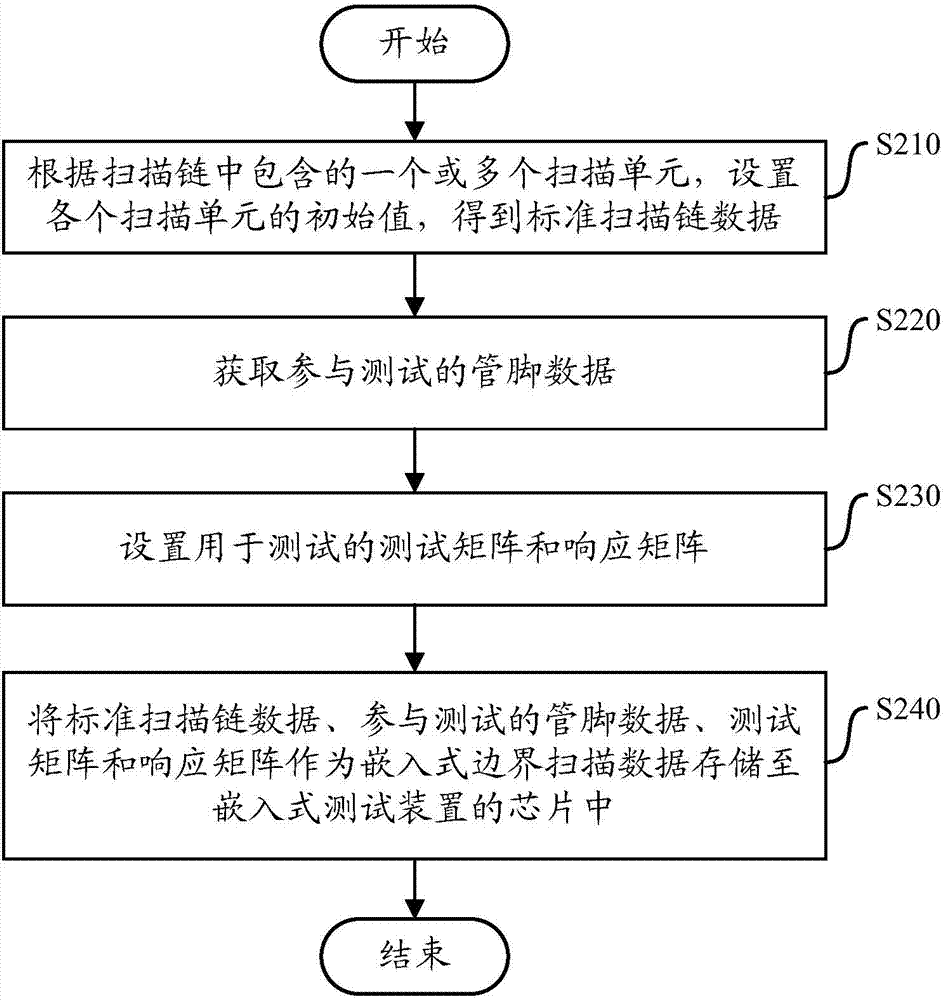

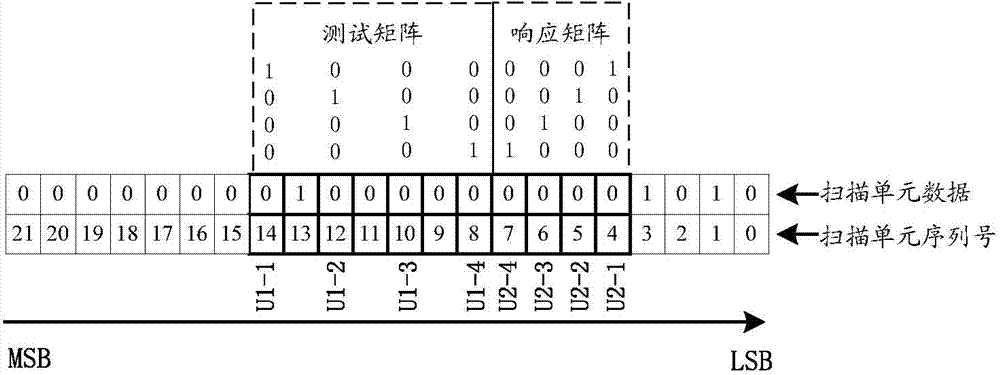

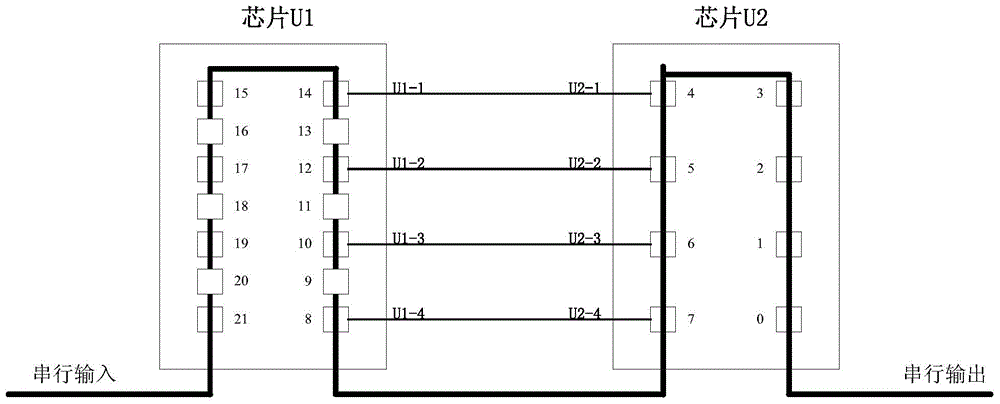

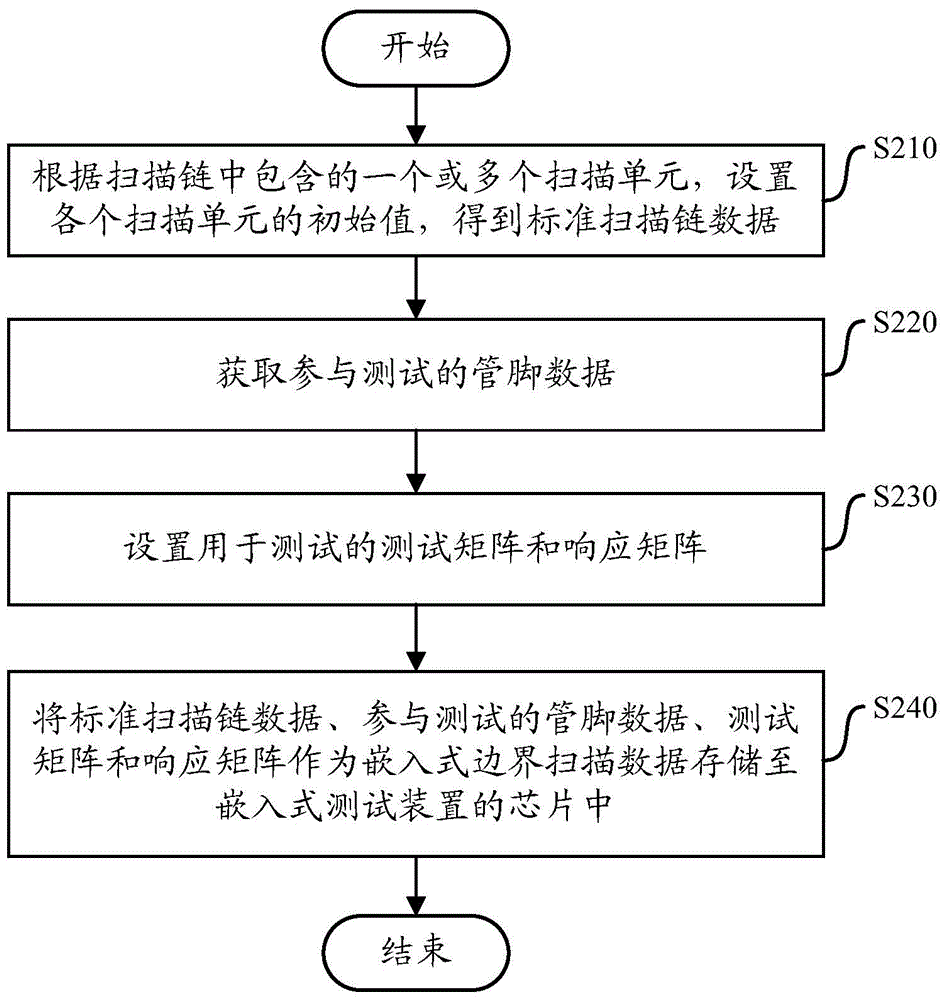

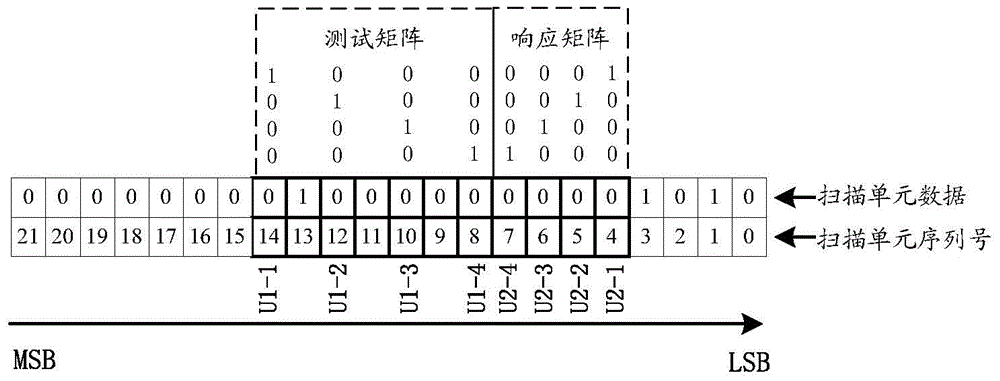

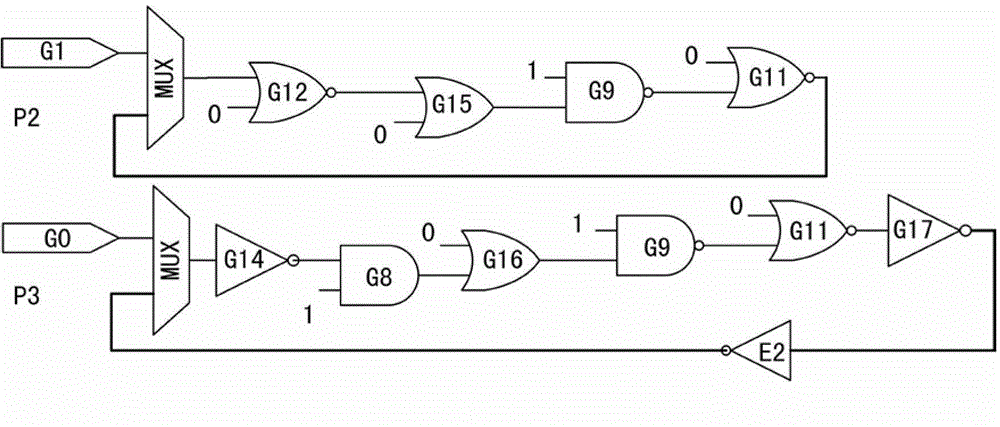

Embedded boundary-scan data compression and synthesis method and device

ActiveCN103675650AReduce data volumeSave storage spaceElectronic circuit testingData compressionComputer hardware

The invention discloses an embedded boundary scan data compression and synthesis method and device. The method comprises the steps of: obtaining a standard scan chain data; obtaining a pin data used in the test, a test matrix and a response matrix; storing the standard scan chain data, the pin data used in the test, the test matrix and the response matrix into the chip of the embedded test device; obtaining the standard scan chain data, the pin data used in the test, the test matrix and the response matrix stored in the chip; calculating the position of the scan unit on the standard scan chain data of each pin used in the test to use the vector synthesis standard scan chain data in the test matrix and the vector synthesis standard scan chain data in the response matrix. The method and device effectively solves the problems of small storage space and being unable to conduct the boundary scan test of a large quantity of data of the test device. The data quantity of the boundary scan datum is effectively compressed, storage space is saved, test time and cost are reduced, and production efficiency is increased.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

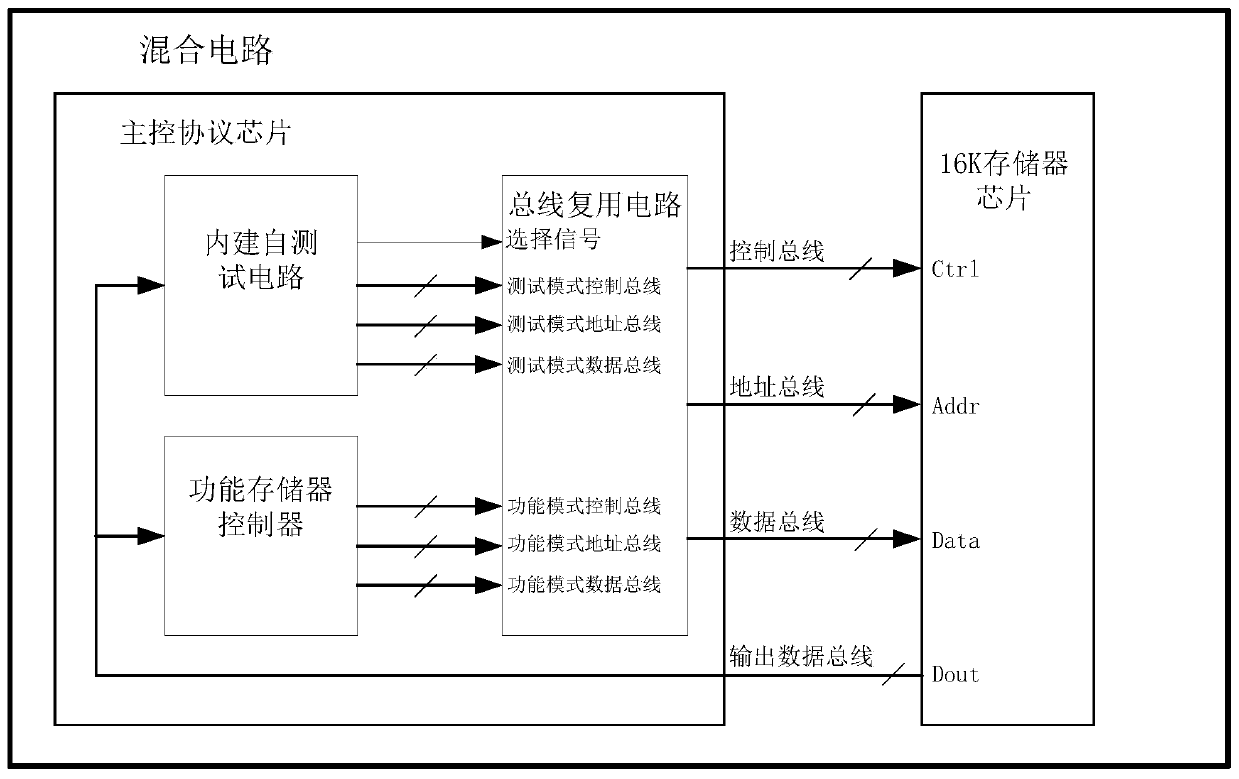

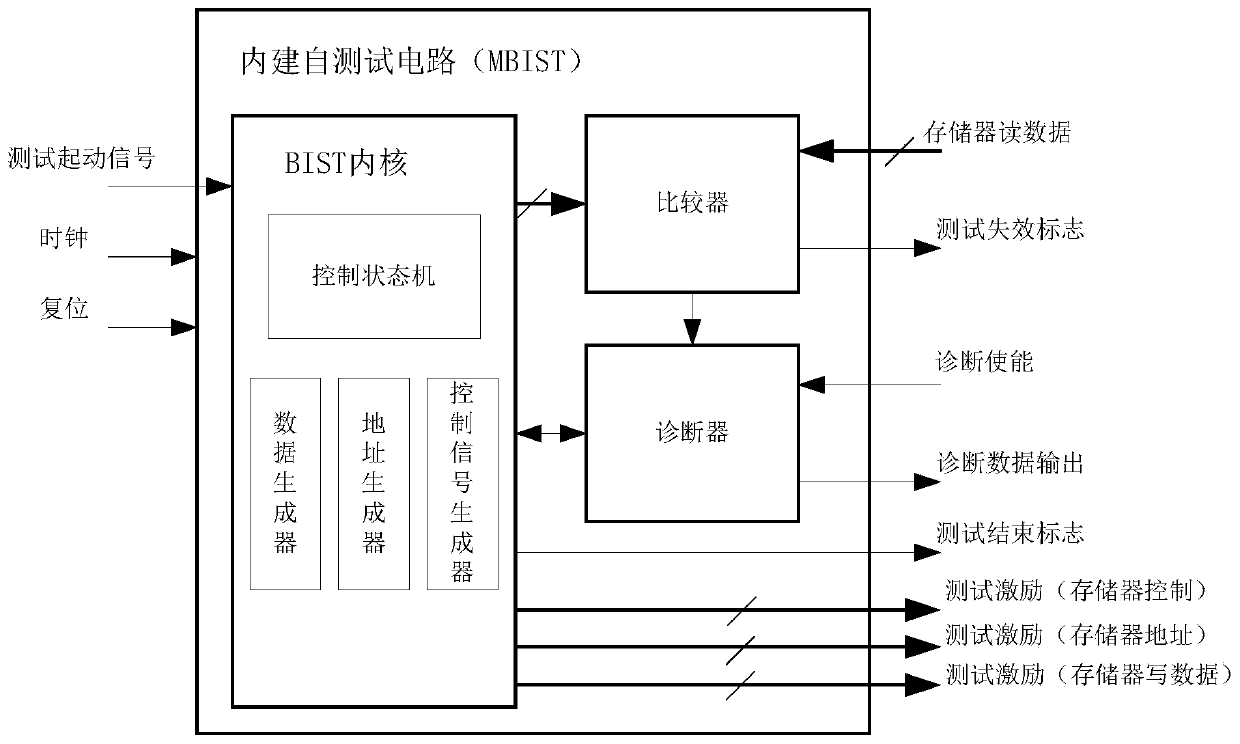

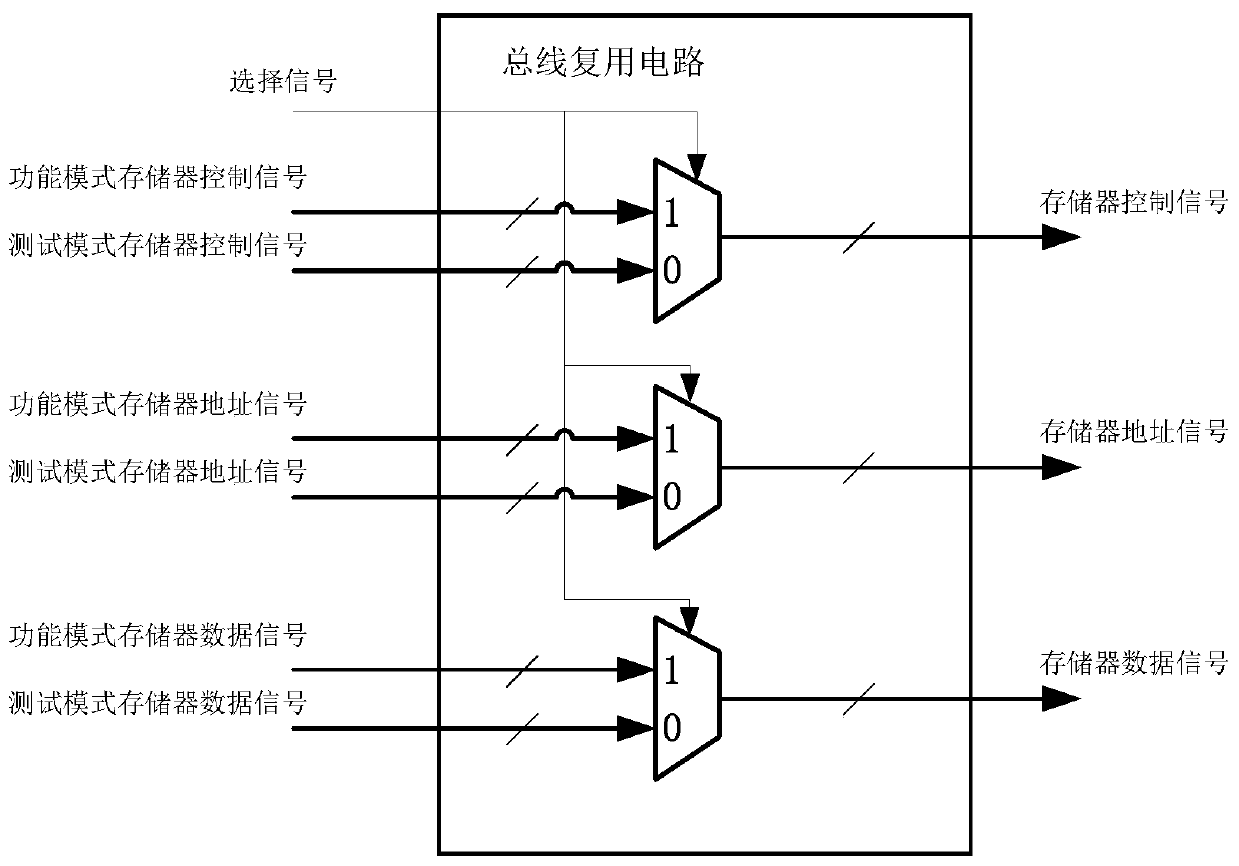

Testing device for a memory chip in a hybrid circuit

The invention provides a testing device for a memory chip in a hybrid circuit. capable of achieving fault positioning and diagnosis at the same time; The device comprises a built-in self-test circuitand a bus multiplexing circuit. The built-in self-test circuit and the bus multiplexing circuit are arranged on the main control protocol chip; The built-in self-test circuit is connected with a selection signal port of the bus multiplexing circuit. The built-in self-test circuit is connected with the bus multiplexing circuit through the test mode control bus, the test mode address bus and the test mode data bus. The main control protocol chip also comprises a functional memory controller; Wherein a control bus of the main control protocol chip is connected with a control port of the memory chip, a data bus of the main control protocol chip is connected with a data port of the memory chip, and an address bus of the main control protocol chip is connected with an address port of the memorychip; An output data bus of the main control protocol chip is connected with an output data port of the memory chip; And the built-in self-test circuit and the functional memory controller read data on the memory chip through the output data bus.

Owner:XIAN MICROELECTRONICS TECH INST

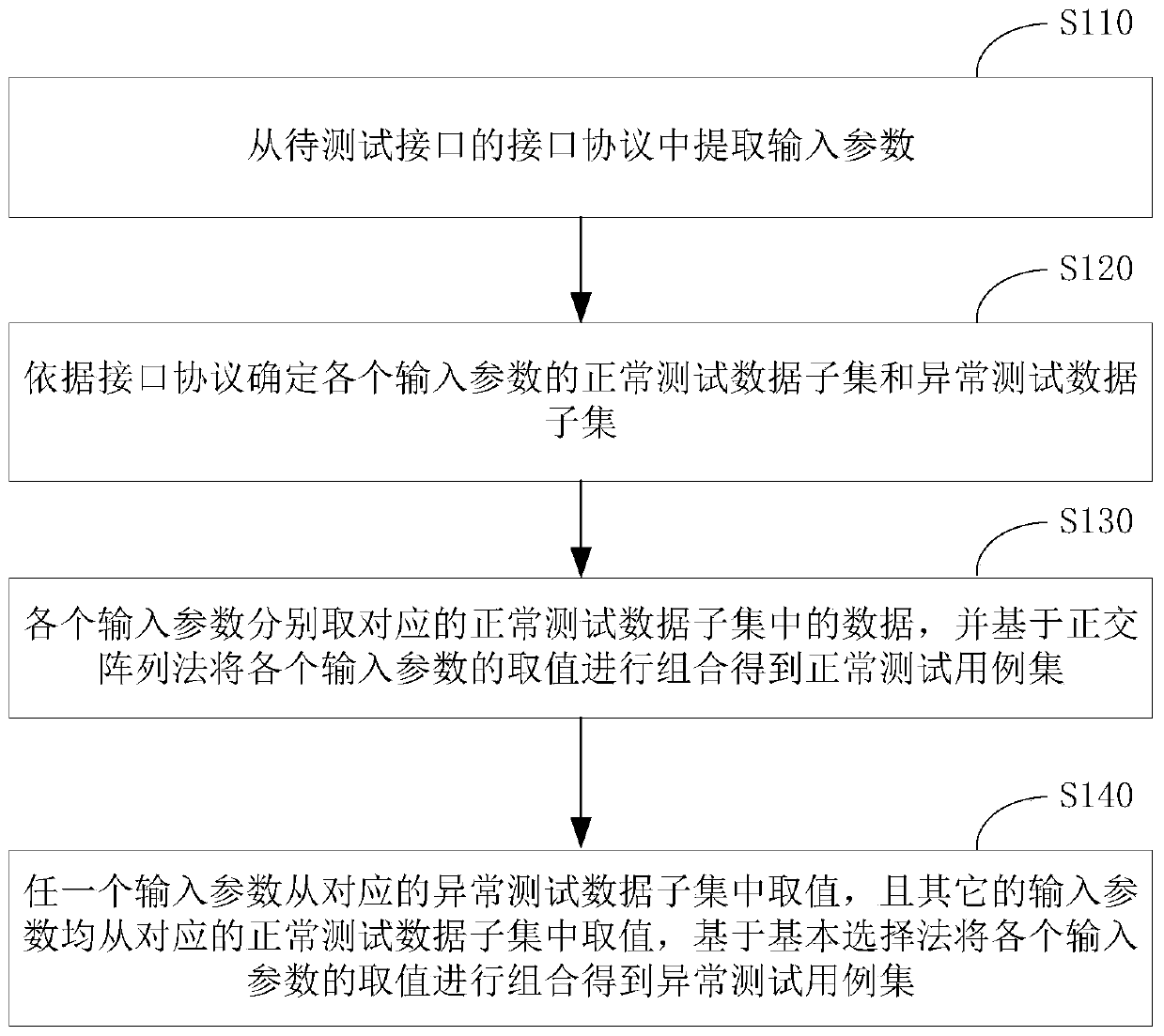

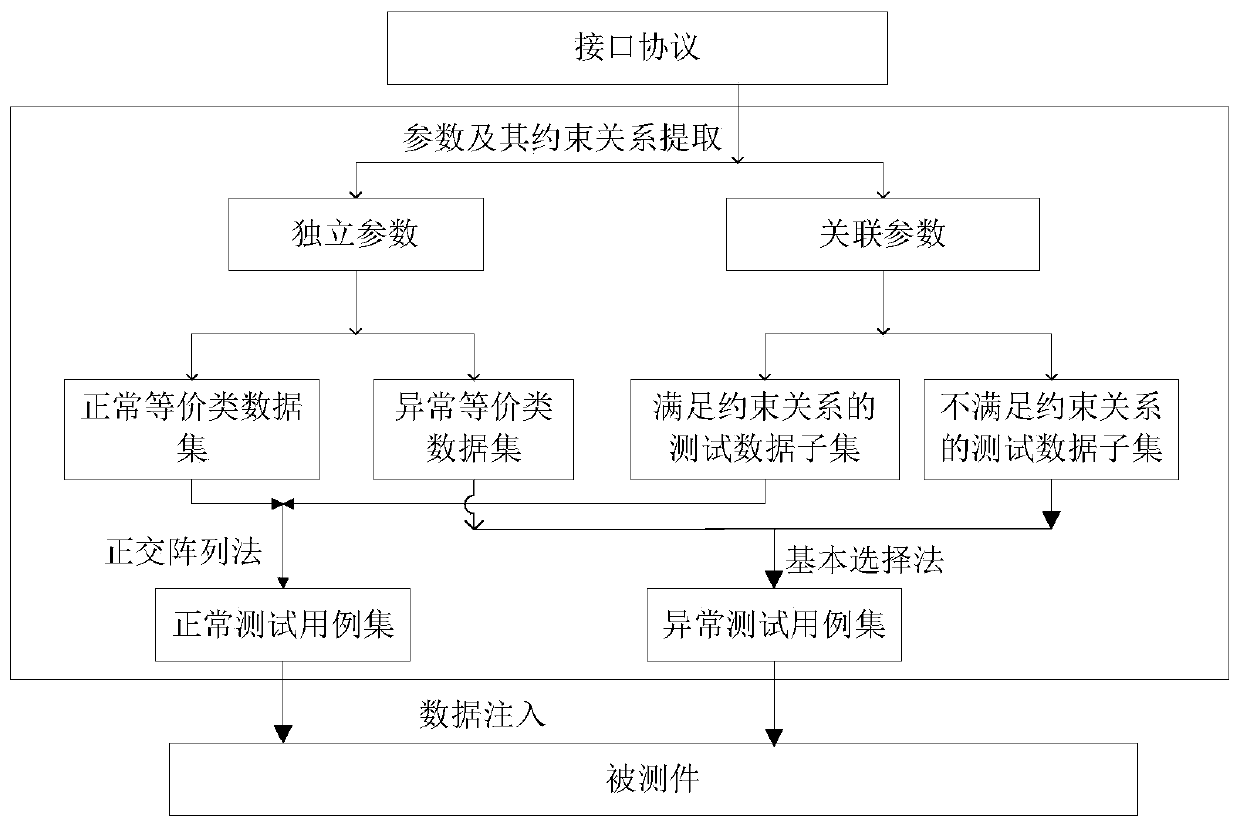

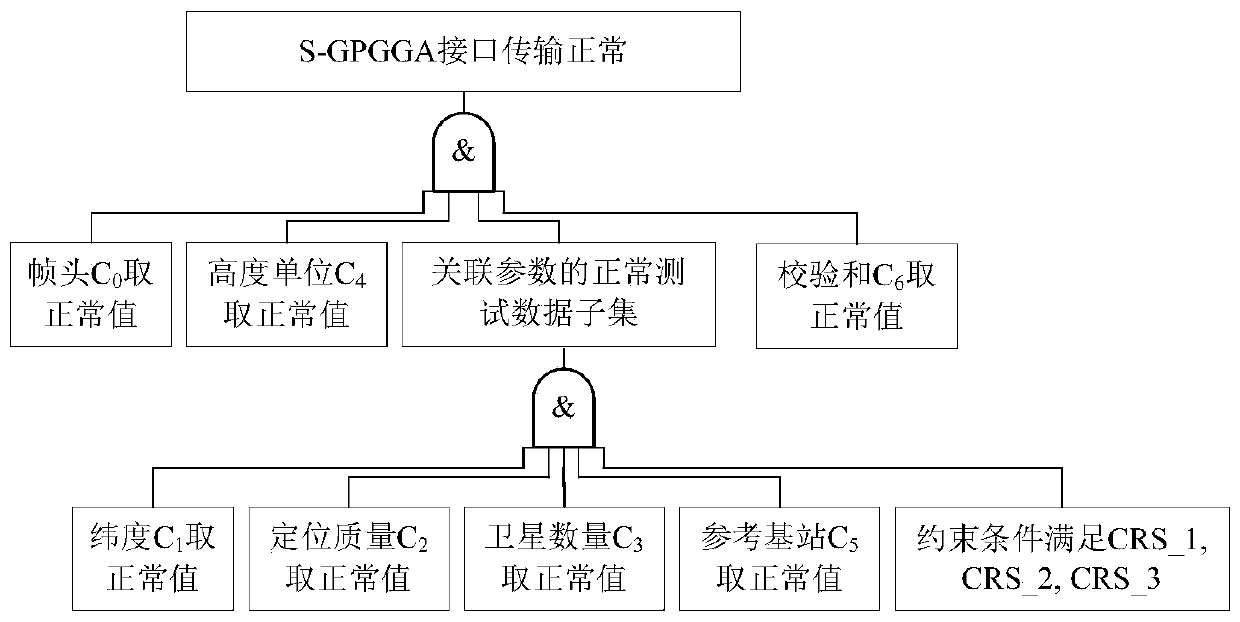

Interface test case generation method and device

PendingCN111444096AImprove test efficiencyPrevent surgeSoftware testing/debuggingEnergy efficient computingOrthogonal arrayTest efficiency

The invention provides an interface test case generation method and device, and the method employs different combination strategies for different parameter input domains, employs an orthogonal array method for the normal test data to generate a pairwise-covered normal test case set, and achieves the verification of the normality of a to-be-tested interface to the maximum degree through employing fewer resources. A single-coverage abnormal test case set is generated by adopting a basic selection method for abnormal test data, so that an abnormal source can be determined, and sharp increase of the number of test cases can be avoided. According to the scheme, good test coverage is obtained, the test overhead is greatly reduced, and the interface test efficiency is effectively improved.

Owner:BEIJING INST OF INFORMATION TECH

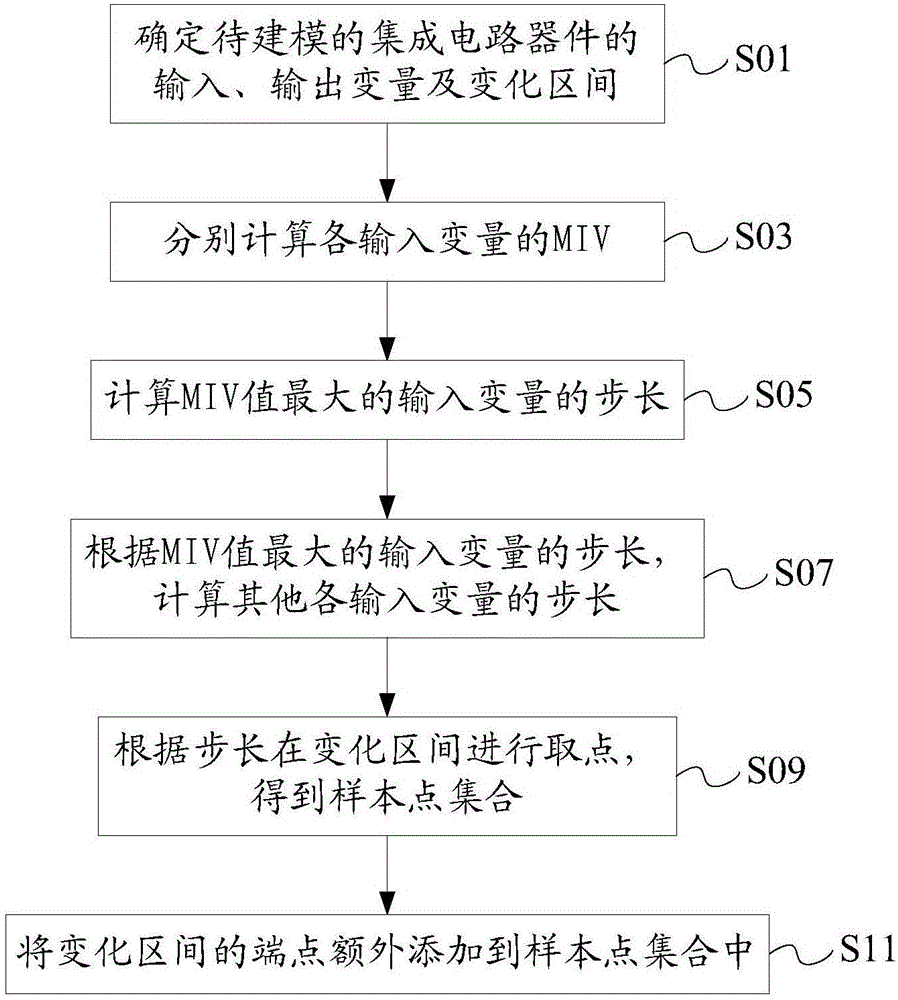

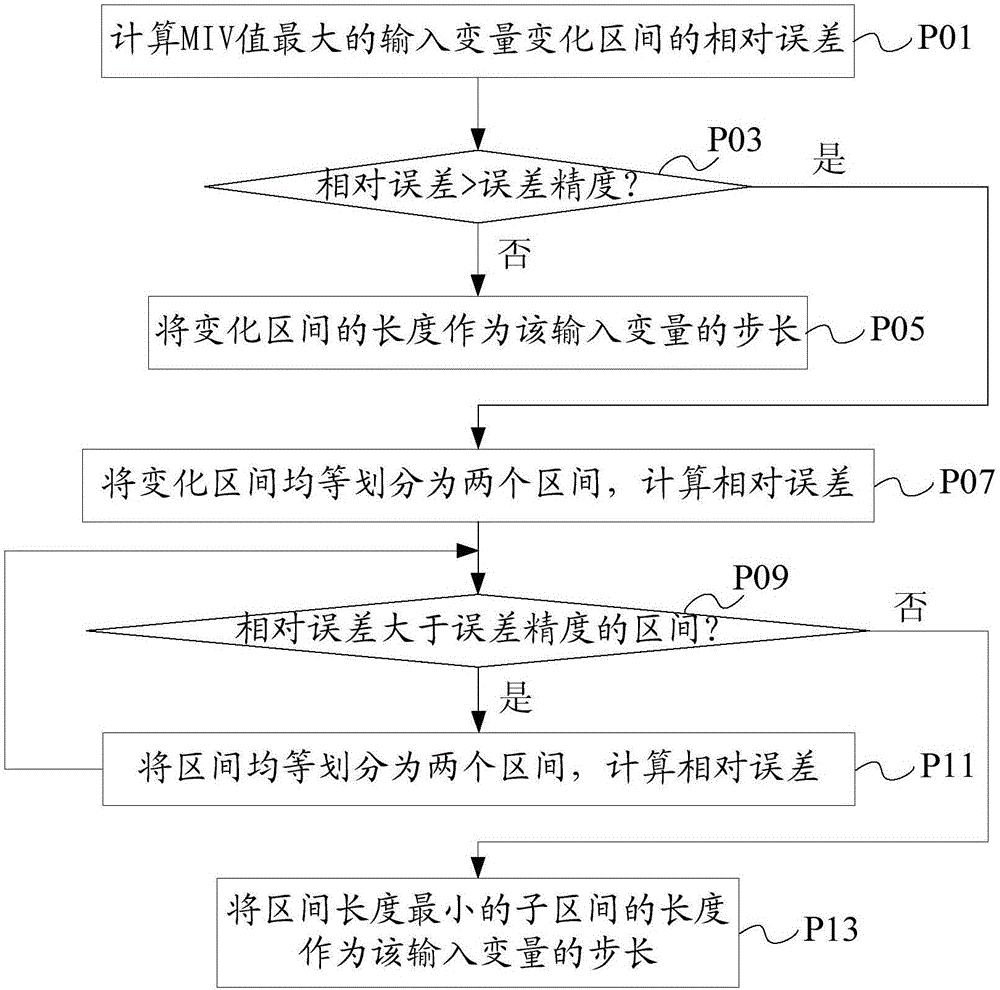

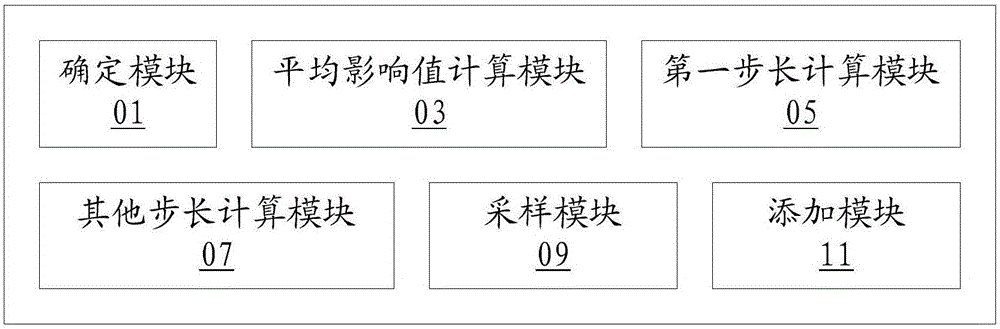

Integrated circuit device neural network modeling sample selecting method and device

ActiveCN106446405AIncrease training speedReduce testing overheadCAD circuit designSpecial data processing applicationsAlgorithmNetwork model

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

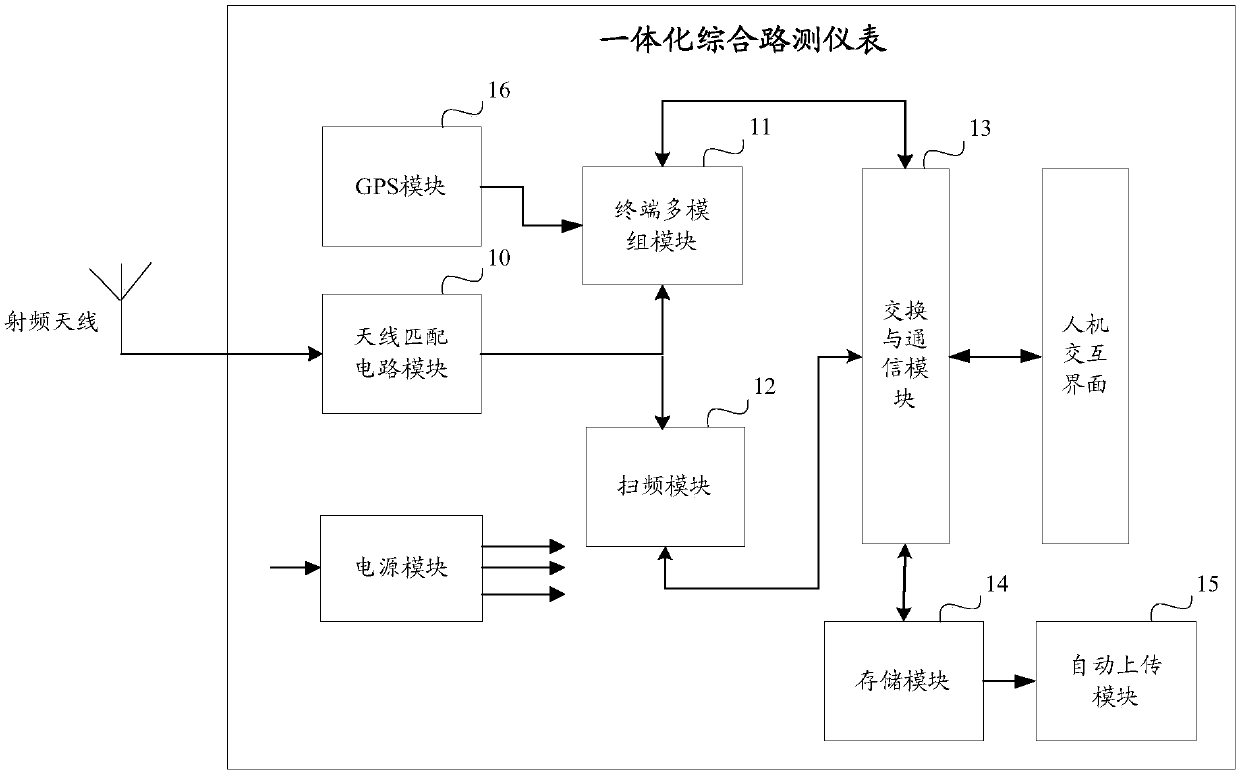

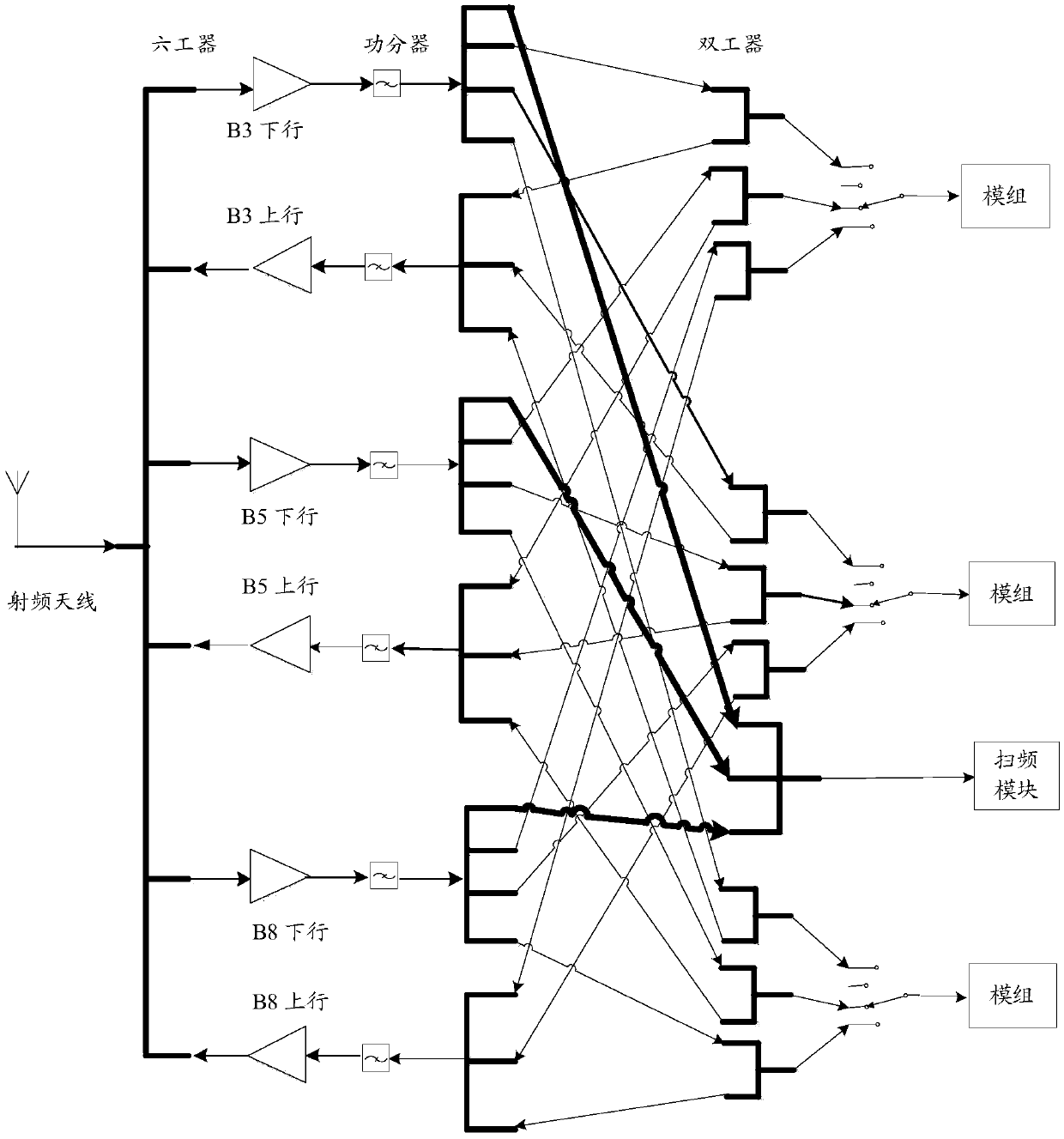

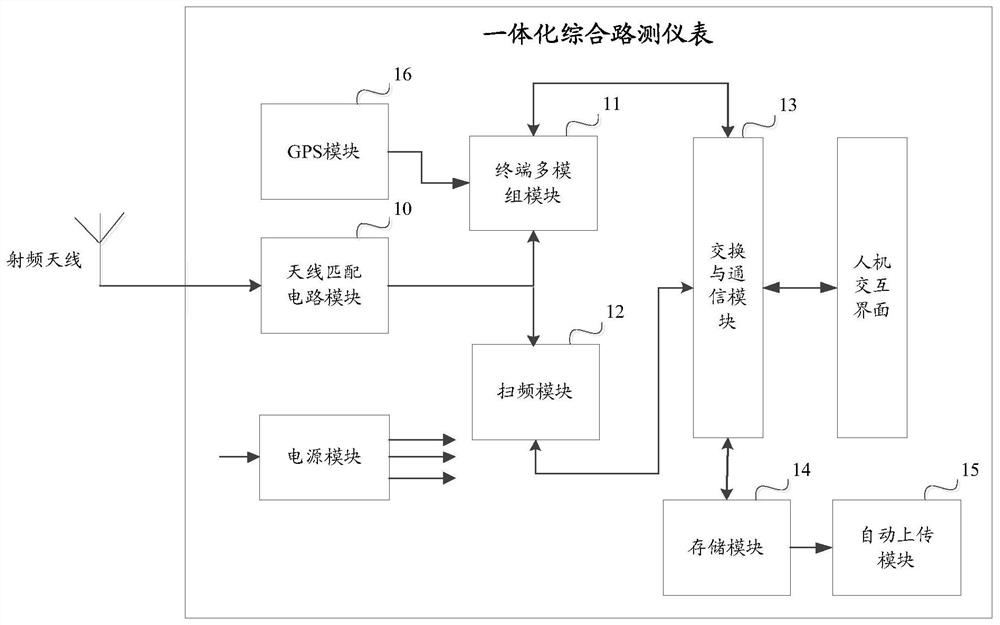

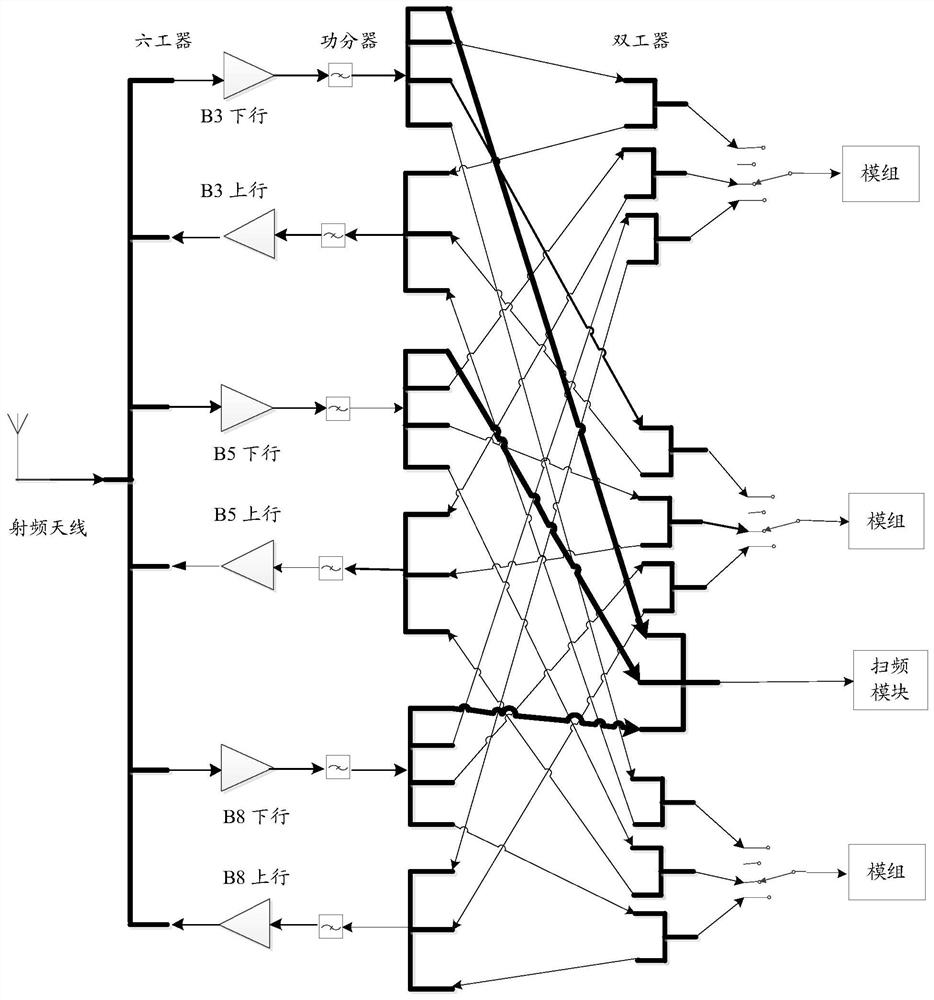

Integrated comprehensive road test instrument

ActiveCN111277339AReduce evaluation errorReduce testing overheadTransmission monitoringSignal onRadio frequency

The invention relates to the field of communication, in particular to an integrated comprehensive drive test instrument. The instrument is used for solving the problem of simultaneous competing test of multiple networks. A method comprises the following steps that an antenna matching circuit module, and the receiving module is used for receiving a total downlink signal sent by the same radio frequency antenna; the antenna matching circuit module is used for distinguishing frequency bands of downlink signals, sending the downlink signals subjected to frequency band distinguishing to the terminal multi-module module, and the terminal multi-module module is connected with the antenna matching circuit module, comprises a first type module set, and is used for receiving one path of downlink signals on the corresponding frequency band and testing and comparing service related parameters. Thus, downlink signals are ensured to come from the same radio frequency antenna; the evaluation error caused by different radio frequency antennas is reduced; compared with the prior art, the accuracy of testing and comparing the related parameters is improved, the service related parameters of different frequency bands belonging to various networks can be tested and compared at the same time, the test comparison of various networks is realized, the test overhead is reduced, the operation process issimplified, and the high efficiency of the test comparison is improved.

Owner:CHINA MOBILE COMM LTD RES INST +1

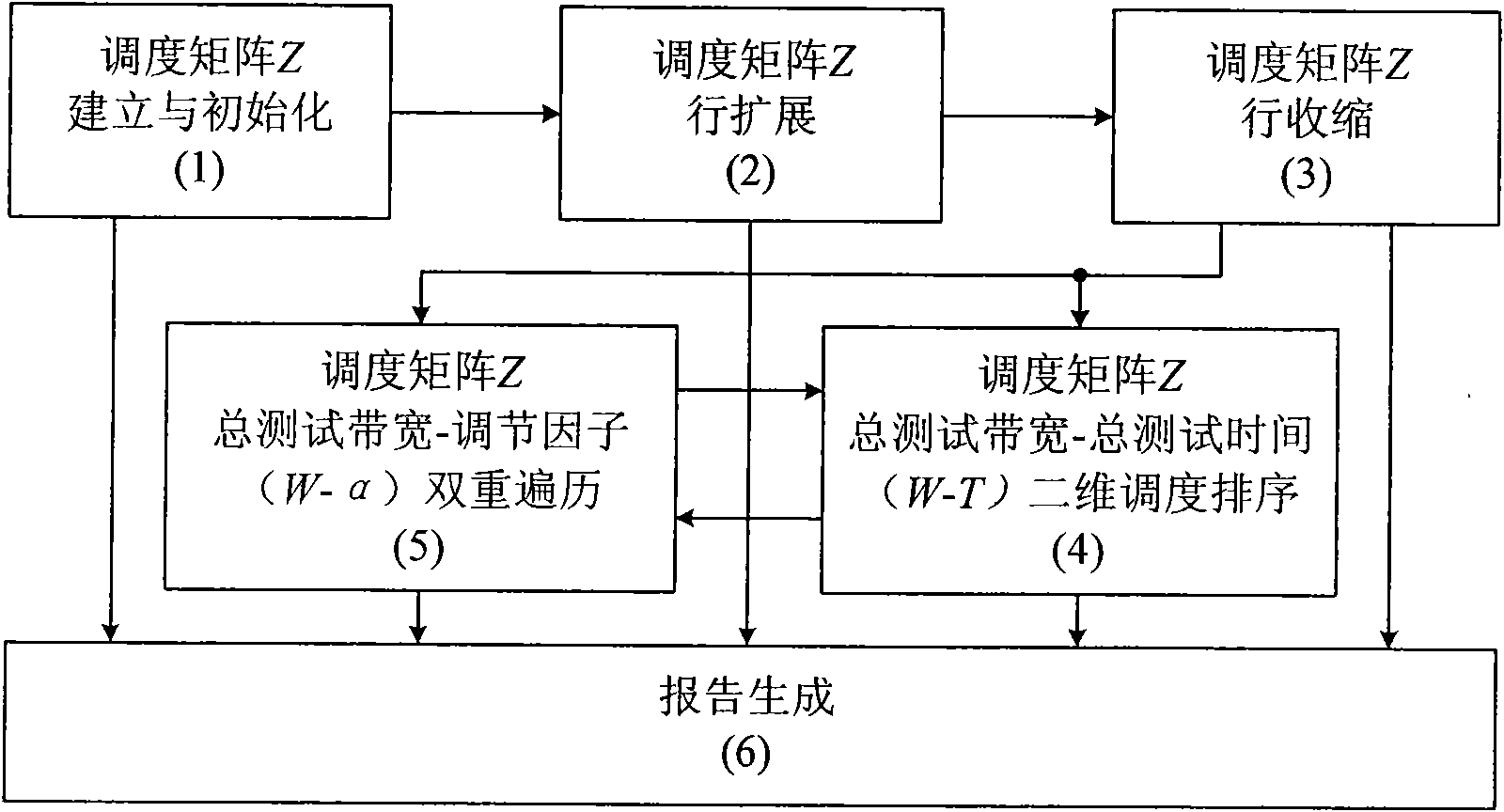

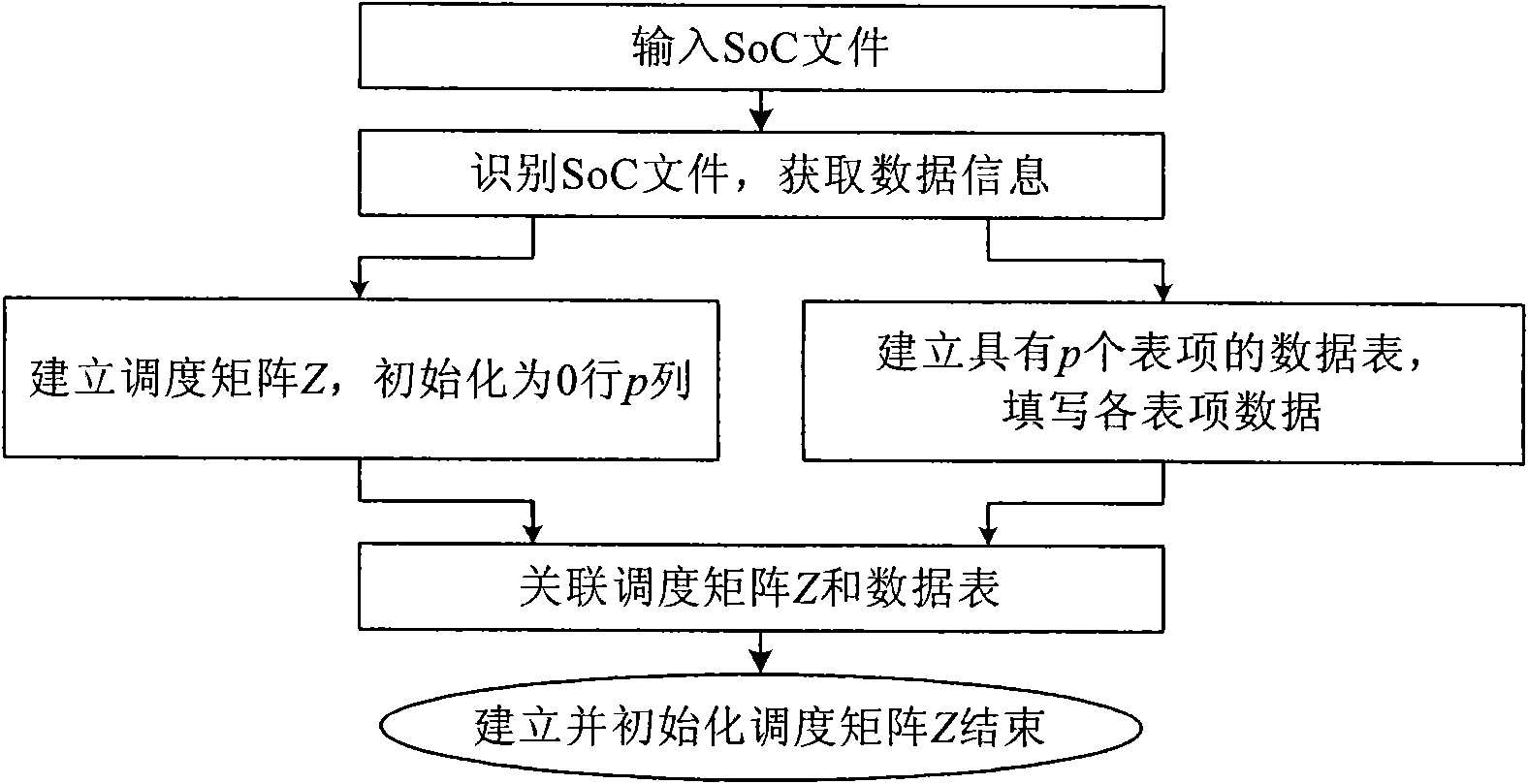

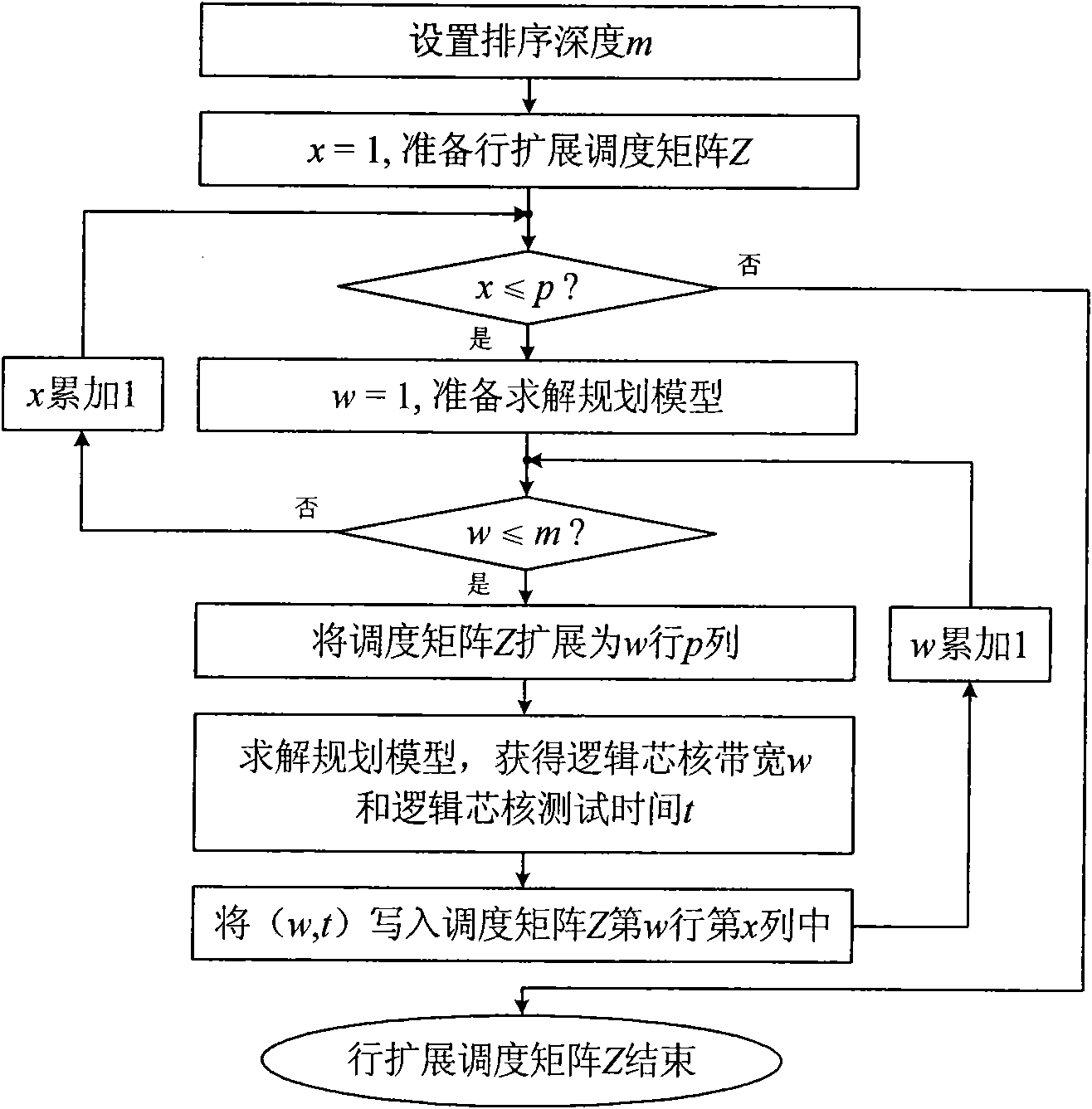

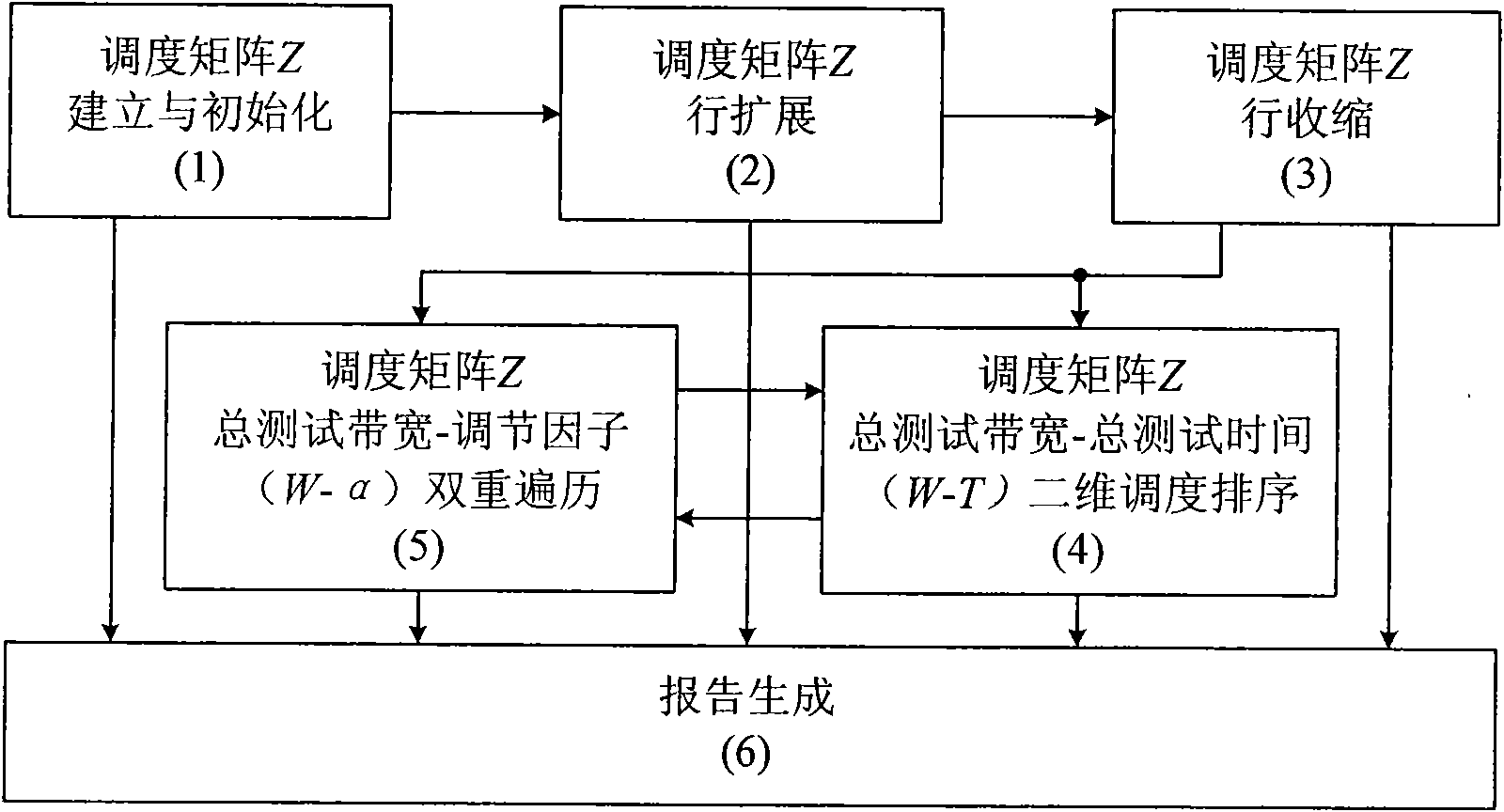

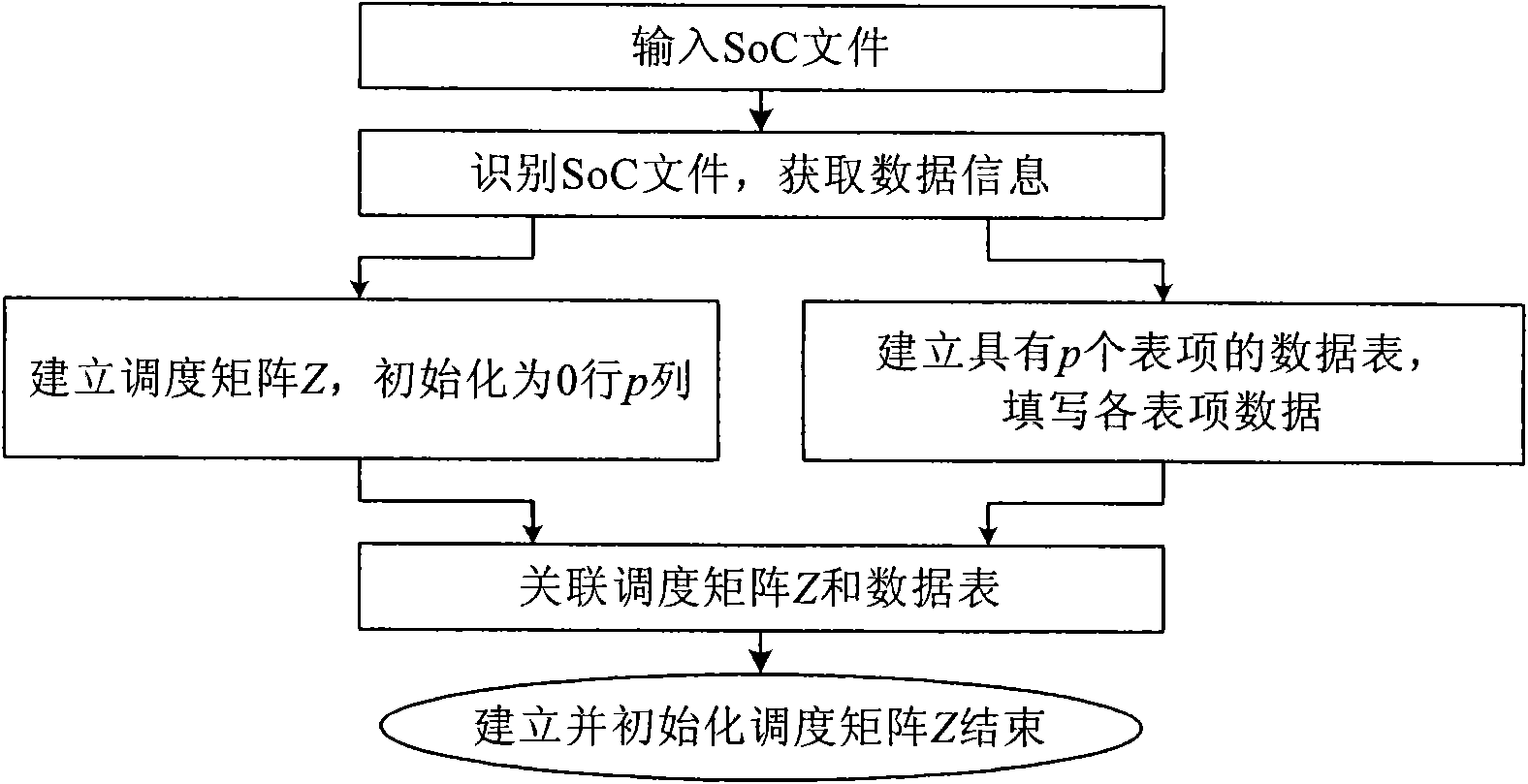

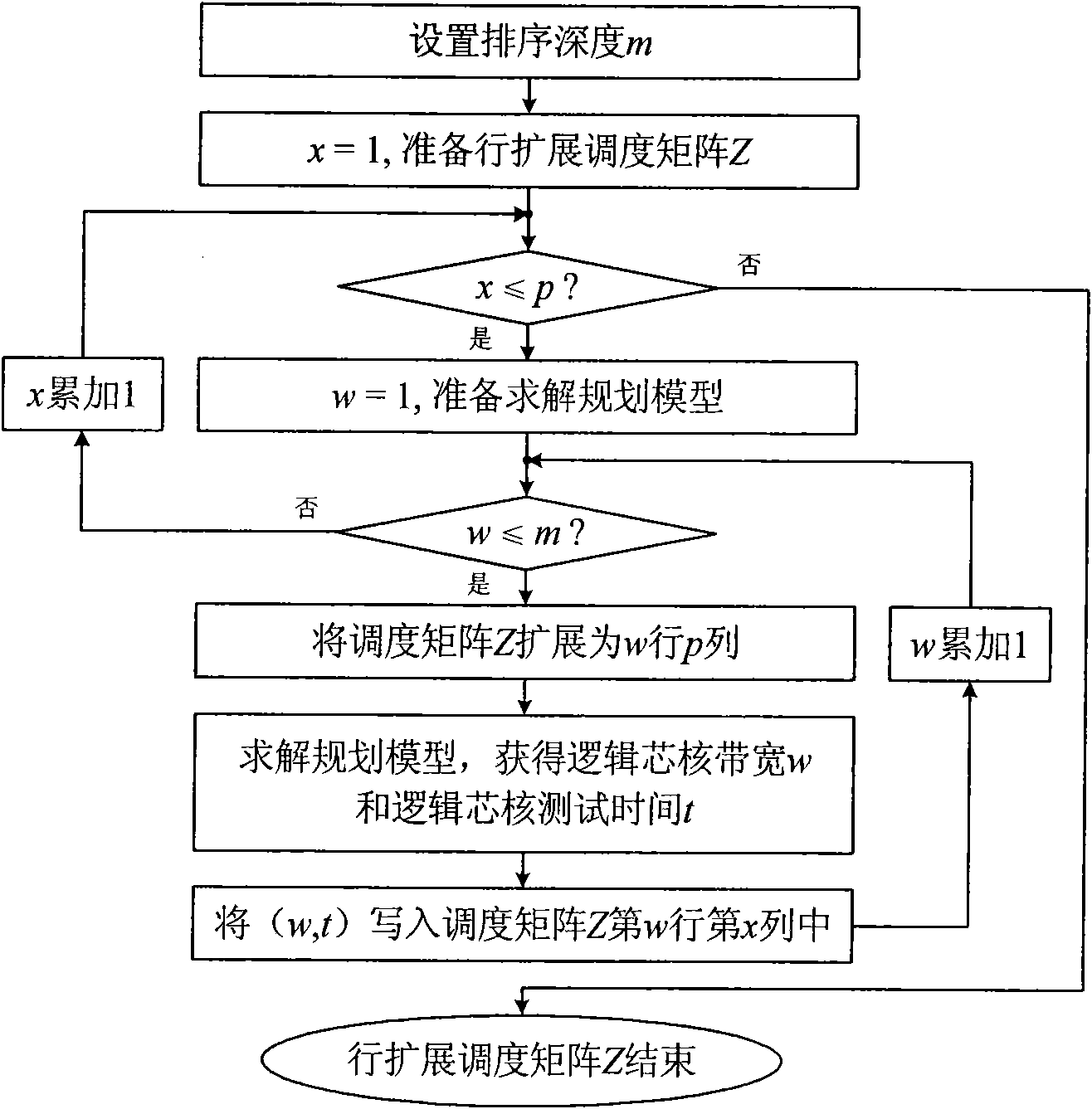

Method for testing dispatching of on-chip systematic embedded logical core by multistage order algorithm

InactiveCN102012480AShorten test timeReduce testing overheadElectrical testingComputer hardwareSorting algorithm

The invention relates to a method for testing dispatching of an on-chip systematic embedded logical core by a multistage order algorithm. The operation method comprises the following steps of: establishing and initializing a dispatching matrix Z; line expanding the dispatching matrix Z; line contracting the dispatching matrix X; two-dimensionally dispatching and sequencing the total testing band width to the total testing time (W-T) of the dispatching matrix Z; double-traversing a total testing band width-adjusting factor (W-alpha) of the dispatching matrix Z; and generating a report. The invention is capable of effectively and integrally solving the two independently problems of the test dispatching of the on-chip systematic embedded logical core and the test link chaining in the logical core, thereby effectively reducing the testing time and testing cost of the on-chip system. The method is convenient in operation, and is applicable to various on-chip systems for finishing the measurability design of the logical core by scanning chain.

Owner:SHANGHAI UNIV

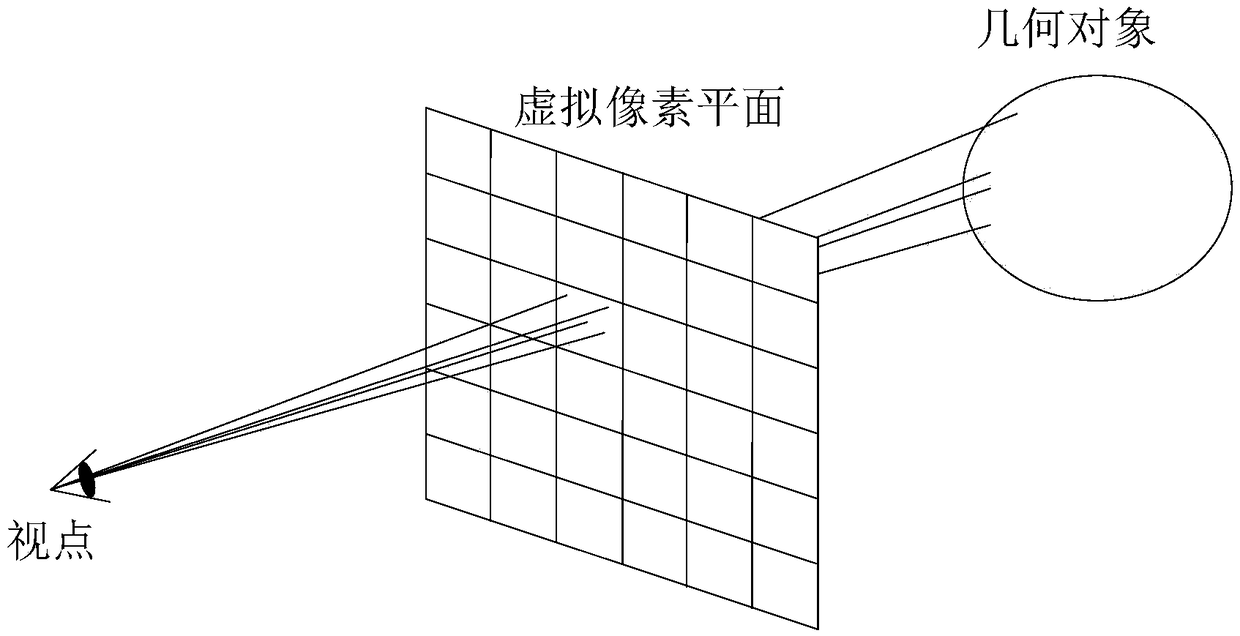

Super-sampling light ray tracking method for multiplexing scene point light source visibility

ActiveCN109493412AReduce testing overheadReduce time overhead3D-image renderingPoint light sourceVisibility

The invention discloses a super-sampling light ray tracking method for reusing scene point light source visibility. According to the method, when oversampling light ray tracing drawing is carried outon a three-dimensional scene; scene points which cannot be directly seen from a viewpoint on a light transmission path are detected; the light source visibility is tested; Firstly, whether scene points adjacent to the grid space data structure exist in a certain range or not is searched for in the grid space data structure; if not, the visibility between the light source and the currently processed scene point is calculated and stored in the grid space data structure, and otherwise, the light source visibility of the nearest scene point in the space position and the normal vector is used as alight source visibility approximate value of the currently processed scene point. According to the method, the light source visibility test expenditure in the super-sampling light ray tracing and drawing can be remarkably reduced, and the speed of the three-dimensional scene super-sampling light ray tracing and drawing is increased.

Owner:CHANGCHUN UNIV OF SCI & TECH

Test method and device under confluence development mode

ActiveCN105302716BTest accurateReduce testing overheadSoftware testing/debuggingTest efficiencyParallel computing

The invention discloses a method and an apparatus for a test in a joint development mode. The method comprises: obtaining a new main code, wherein updated branch codes are combined into a main code to generate the new main code; starting a compiling tool to compile the new main code; monitoring whether an installation package is generated in a compiling process of the new main code or not, and if the installation package is monitored, obtaining the installation package and / or a reference package before the updated branch codes are combined into the main code; and performing an automated test on the installation package and / or the reference package to generate an automated test result. According to the method and the apparatus, the technical problems of inaccurate test result and low test efficiency caused by adoption of a timed test method in a software development mode of combining branch codes with a main code in the prior art are solved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Integrated circuit test system and method

ActiveCN105116317BReduce testing overheadImprove test efficiencyElectrical testingTest efficiencyTest flow

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

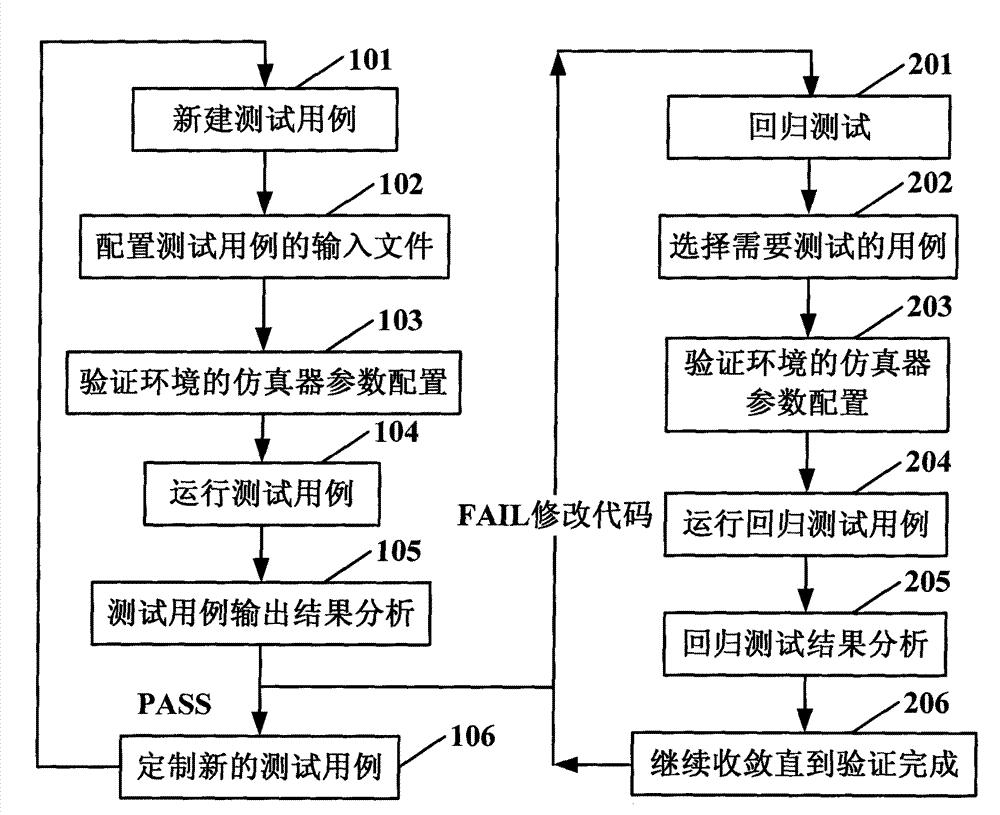

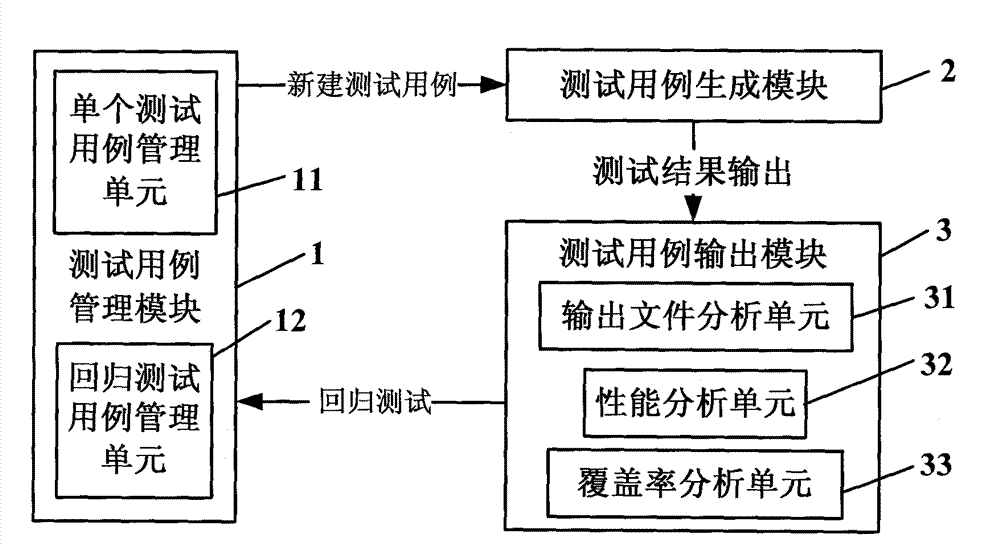

Verifying environment patterned chip verifying method and device

ActiveCN102156784BEasy to operateRealize managementSpecial data processing applicationsRegression testingFunctional testing

Owner:FENGHUO COMM SCI & TECH CO LTD

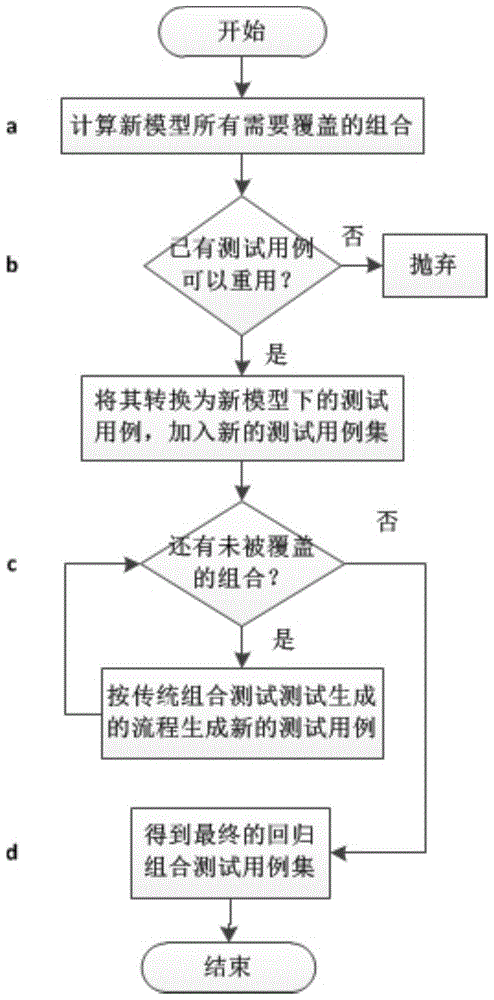

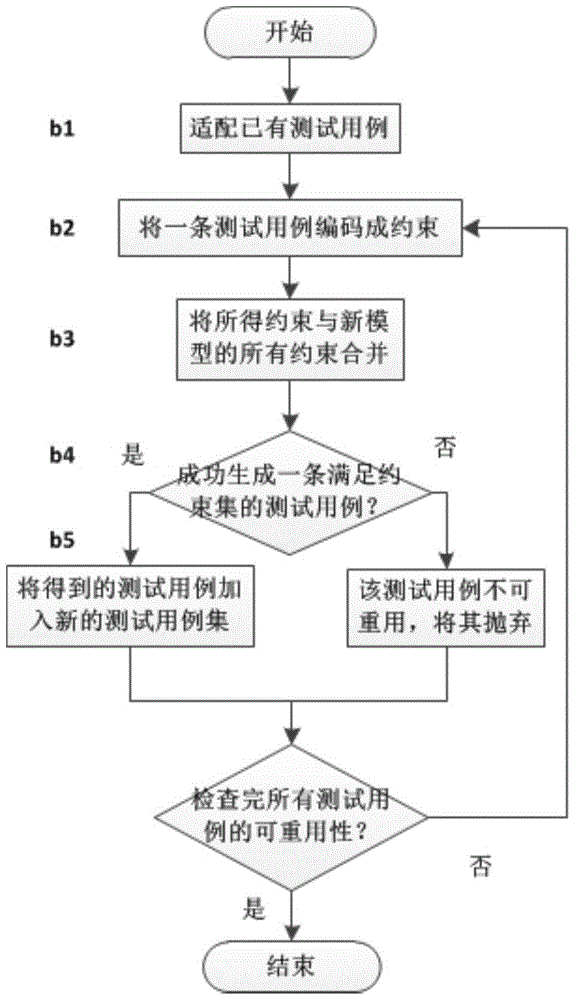

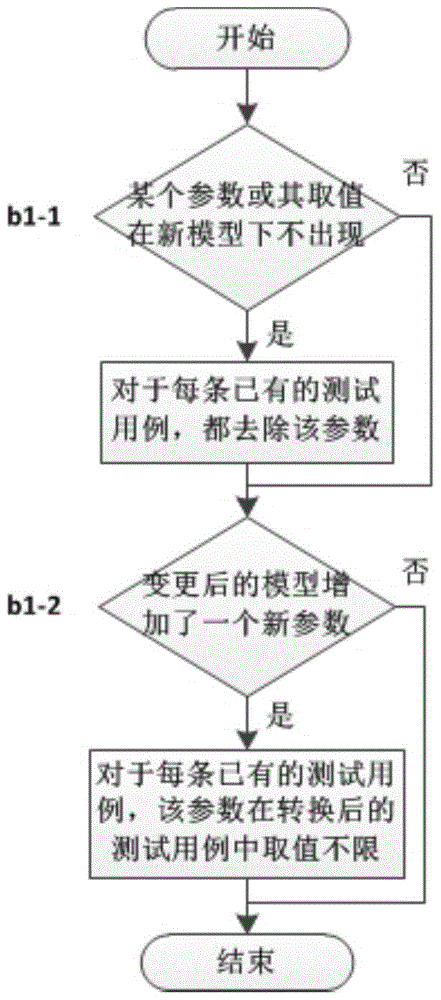

A Regression Test Case Reuse Method Based on Software Composition Testing

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

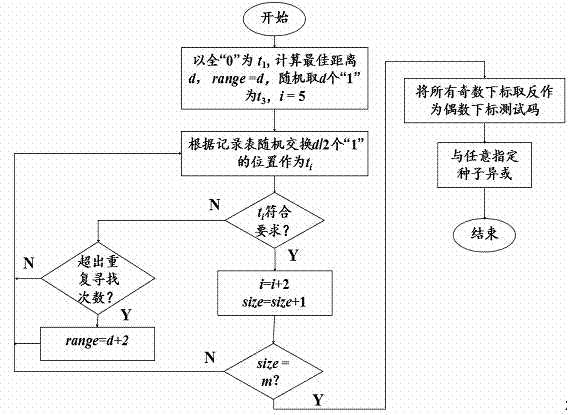

Quasi-full maximum distance random testing method

InactiveCN103870369AReduce testing overheadImprove fault coverageDetecting faulty computer hardwareTest efficiencyResource consumption

The invention relates to a quasi-full maximum distance random testing method. The method comprises the following testing steps: reading the primary input number n of a circuit from a text, and specifying an initial seed n-bit binary code t0 to generate a desired testing code number 2m; generating a subscript odd testing code set which is accordant with a maximum total Descartes distance according to the primary input number n; further acquiring a subscript even testing code set according to the rule of the maximum Hamming distance on the basis of the obtained subscript odd testing code set to form a middle testing set; performing exclusive-or operation on the middle testing set and a specified testing seed t0 to obtain a final complete testing set. By adopting the quasi-full maximum distance random testing method, the problems of huge resource consumption and time consumption for achieving an ideal fault covering rate since random testing codes are not excessive in the conventional random testing algorithm under the condition that the circuit scale increases sharply at present and integrated circuits develop rapidly are solved. The method has the characteristics that the testing efficiency is increased, and the fault covering rate is increased.

Owner:SHANGHAI UNIV

Method for determining performance of Web server

Owner:HANGZHOU DIANZI UNIV

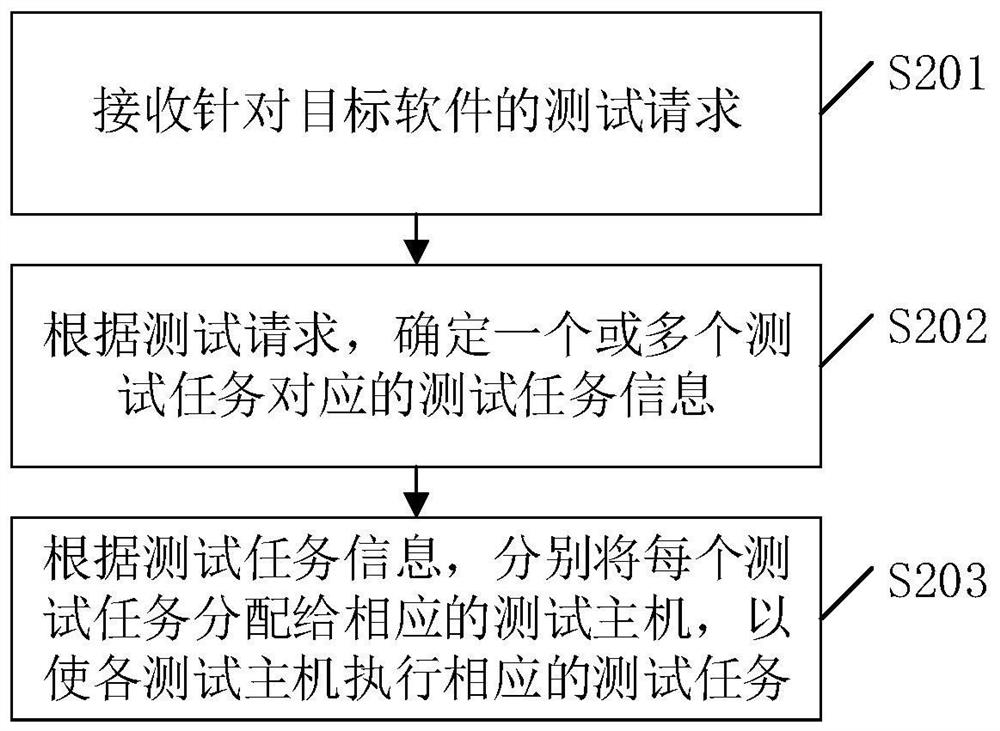

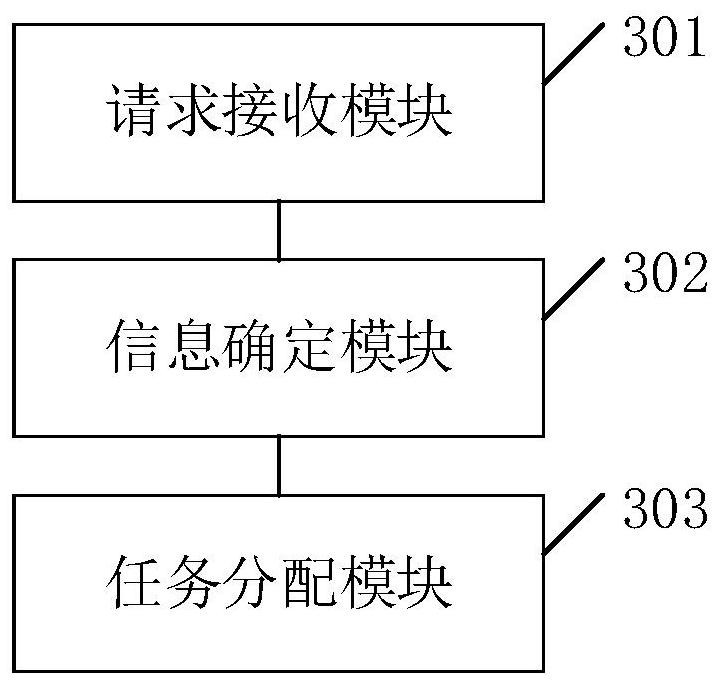

A software testing method and device

ActiveCN107590075BReduce testing overheadShorten the development cycleResource allocationSoftware testing/debuggingTest platformTest group

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

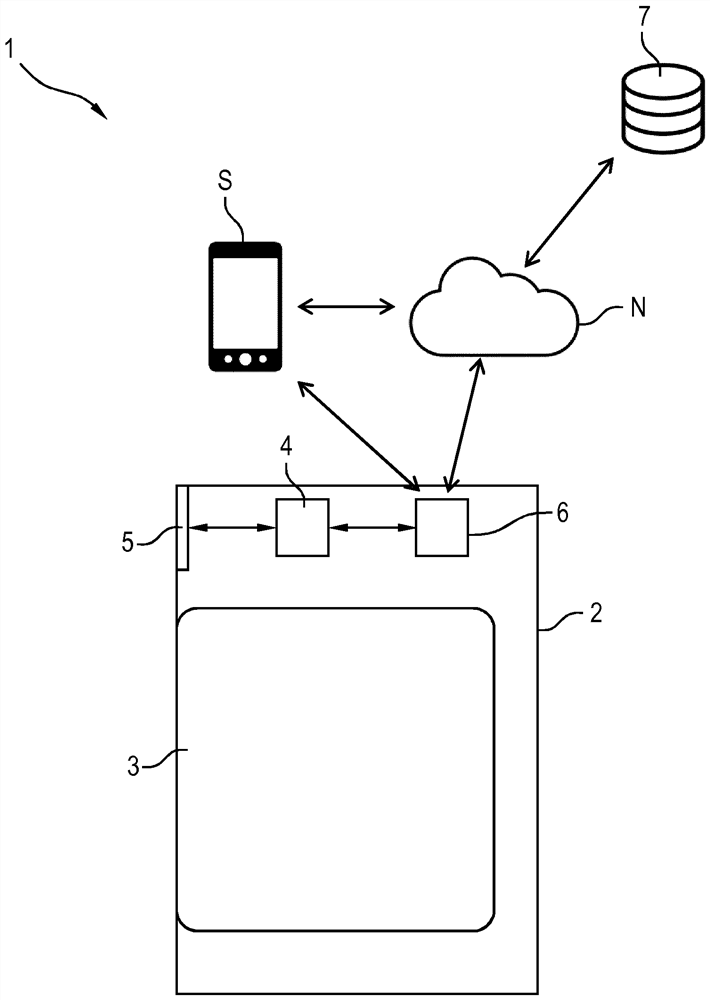

Domestic appliance, domestic appliance system, and method for operating a domestic appliance

PendingCN112703349AReduce riskReduce testing overheadDomestic stoves or rangesLighting and heating apparatusHome applianceOperating system

The invention relates to a network-compatible domestic appliance (2) having a communications device (6) for being coupled via data link to an external database (7), the domestic appliance (2) being designed to receive operating parameters (R1, R2), which are relevant for an operating sequence, from the database (7) via the communications device (6) and to store said operating parameters for carrying out an operating sequence, and, initiated by a user, to transmit the operating parameters (R1, R2), which are relevant for an operating sequence carried out by the domestic appliance (2), automatically to the database (7) via the communications device (6). A domestic appliance system (1) has at least one network-compatible domestic appliance (2) and a database (7) which can be coupled via a network (N) to the at least one domestic appliance (2) and is configured to store operating parameters (R1, R2) for an operating sequence of the domestic appliance (2) and to provide said operating parameters retrievably to the at least one domestic appliance (2). A method (S1-S4) used to operate a network-compatible domestic appliance (2). The invention is particularly advantageously applicable to cooking appliances as domestic appliances.

Owner:BSH BOSCH & SIEMENS HAUSGERAETE GMBH

Crowdsourced testing method

ActiveCN104579854BThe test effect is goodReduce testing overheadData switching networksCrowdsourced testingSoftware engineering

The present invention provides a crowdsourcing testing method, comprising: the test client sends the characteristic information of the test client to the test server, and the test server selects the service to be tested according to the received characteristic information of at least one test client The client to be tested, the test server sends a list of services to be tested to the client to be tested, and the client to be tested tests the services to be tested in the list of services to be tested to obtain the service to be tested test results, and finally, the client to be tested sends the test results to the test server. This crowdsourcing testing method for testing network application services not only significantly improves the testing effect, but also effectively reduces the testing overhead.

Owner:BEIHANG UNIV

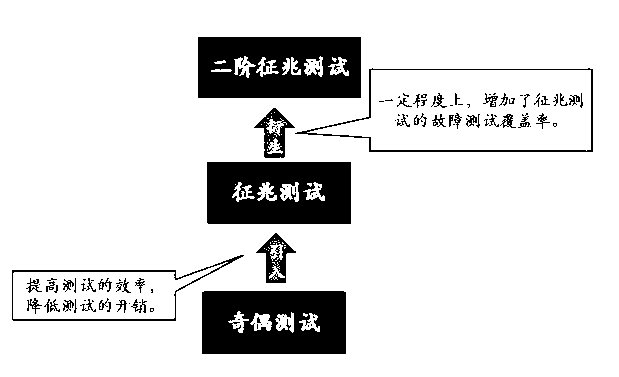

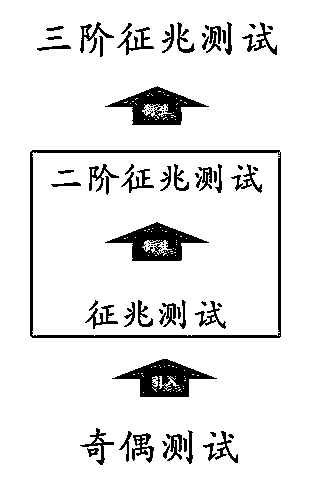

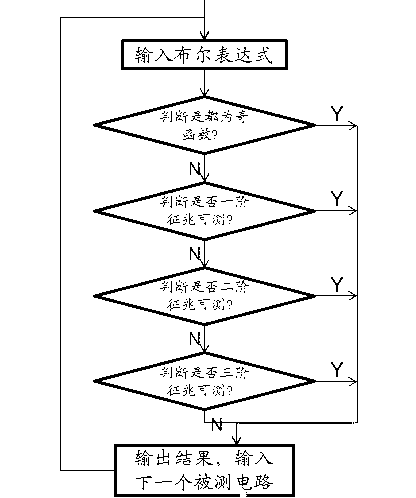

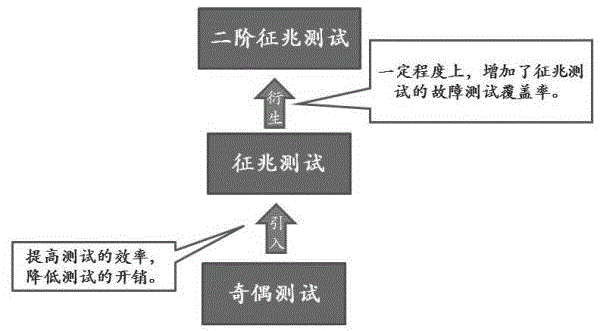

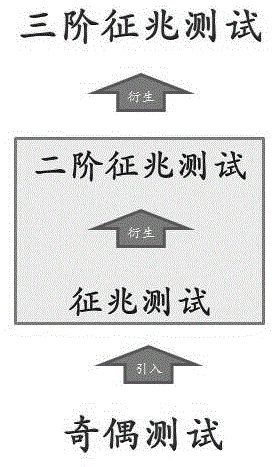

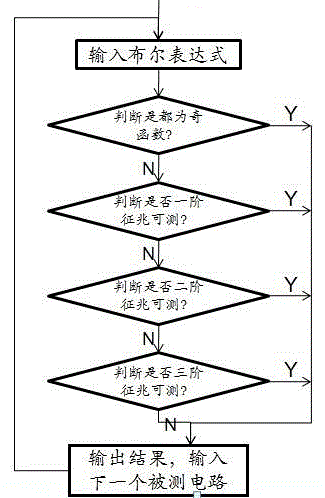

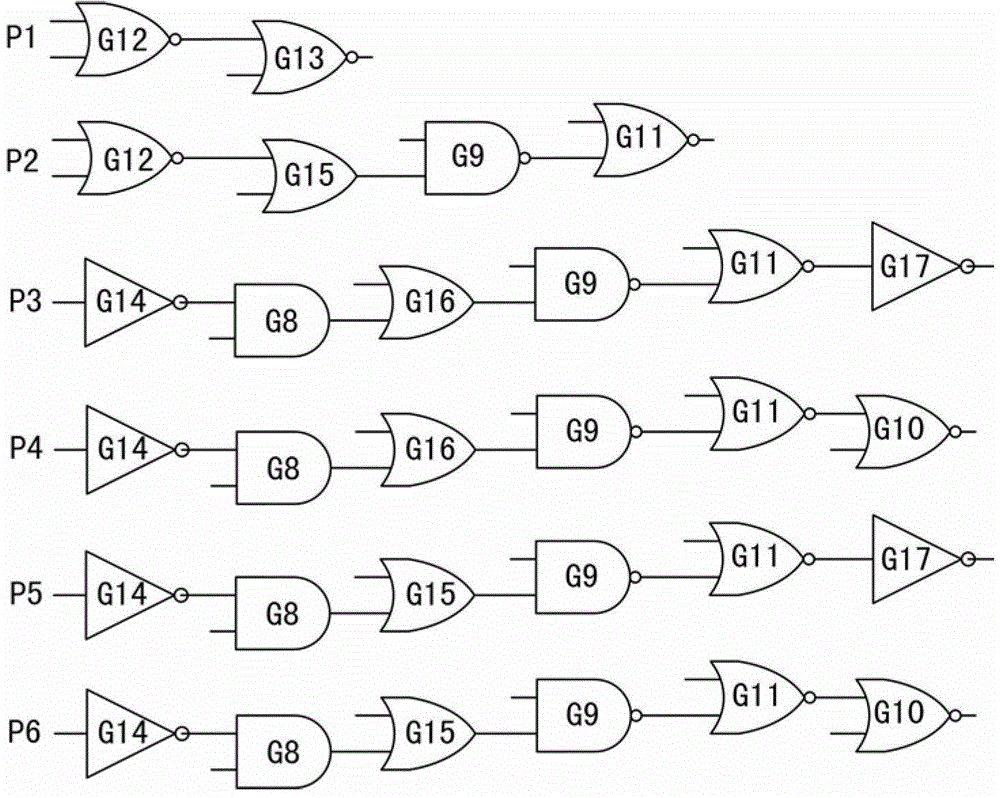

Three-step sign test method combined with odd-even check

InactiveCN102981923AReduce testing overheadImprove fault coverageRedundant data error correctionTest efficiencyComputer hardware

The invention relates to a three-step sign test method combined with odd-even check. Test steps of the three-step sign test method combined with the odd-even check comprise that step 1, the corresponding boolean expression of a circuit is read from a text; step 2, the boolean expression is analyzed to generate corresponding intermediate data and the odd-even check is conducted; step 3 based on a foundation of the odd-even check, a first step sign test judgment, a second step sign test and a third step sign test judgment are conducted according to the intermediate data correspondingly generated; step 4, a test result is recorded in a textual mode. The three-step sign test method combined with the odd-even check has the advantages of improving test efficiency and a failure coverage rate of the sign test simultaneously and enabling a former circuit not capable of testing a sign to be capable of conducting the sign test. The three-step sign test method combined with the odd-even check brings in the odd-even test based on a traditional sign test in the first place, preprocesses the circuit being tested, improves test efficiency, conducts further sublimation process on the sign test to form the second step sign test and the third step sign test, and improves the failure coverage rate of the test.

Owner:SHANGHAI UNIV

Method and system for determining execution sequence of test case sets

InactiveCN103577325BMinimal reconfiguration timesSmall test switching costsSoftware testing/debuggingSequence determinationComputer science

The invention discloses a method and a system for determining an execution sequence of a test case suite. The method comprises the steps as follows: the single case switching cost between any two test cases in an initial test case suite is calculated; h test cases with all combination possibilities are selected from the initial test case suite, and all the possible first optimum execution sequences and first switching costs which are formed by the h test cases are obtained; according to the first switching costs and the single case switching cost, all possible second optimum execution sequences and second switching costs which are formed by h+1 test cases are calculated and obtained; the second optimum execution sequences and the second switching costs are taken as the first optimum execution sequences and the first switching costs respectively, h is increased by 1, a previous step is returned until the second optimum execution sequences comprise all test cases; and a second optimum execution sequence with the smallest second switching cost is taken as the optimum execution sequence, so that minimum reconfiguration times of parameters in a test can be realized, and the expenditure is reduced.

Owner:NANJING UNIV

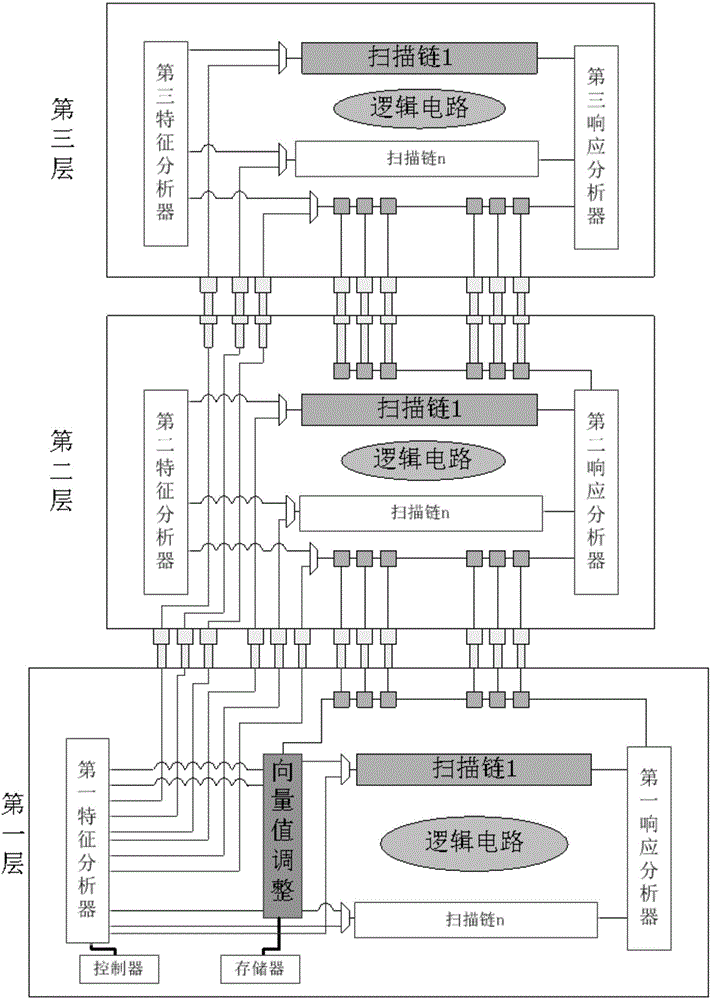

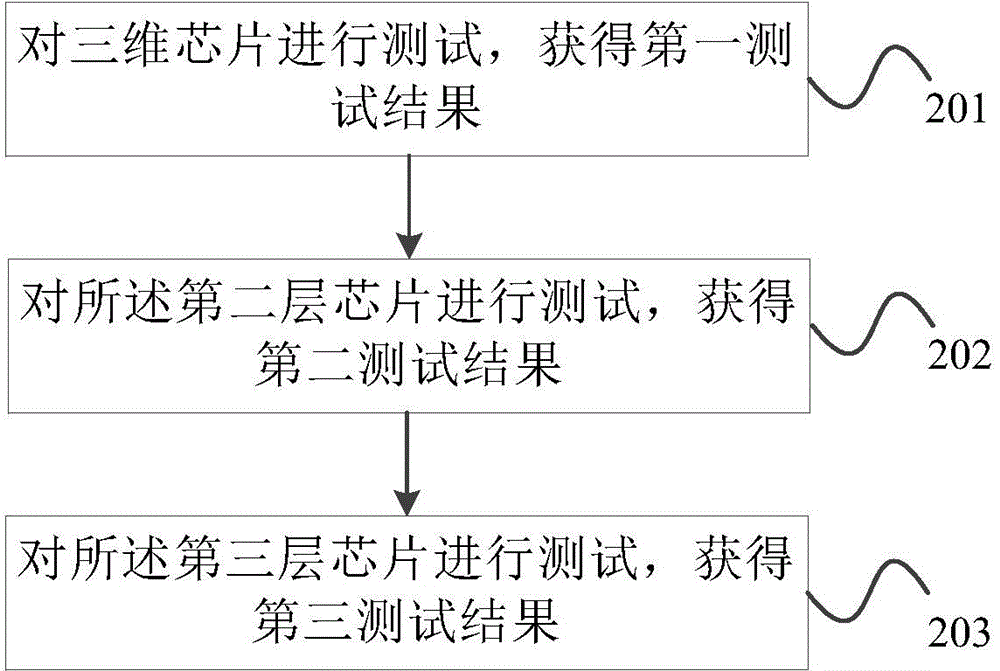

Three-dimensional chip testing method and three-dimensional chip testing device

InactiveCN104597395AReal-time detectionReduce storageElectronic circuit testingThree-dimensional integrated circuitComputer science

The invention provides a three-dimensional chip testing method and a three-dimensional chip testing device. The three-dimensional chip testing device comprises a first feature analyzer, a second feature analyzer and a third feature analyzer, wherein the first feature analyzer arranged on a first-layer chip is connected with the first-layer chip, a second-layer chip and a third-layer chip and is used for testing a three-dimensional chip to obtain a first testing result; the second feature analyzer arranged on the second-layer chip is used for testing the second-layer chip to obtain a second testing result; the third feature analyzer arranged on the third-layer chip is used for testing the third-layer chip to obtain a third testing result. The three-dimensional chip is a chip formed by binding of the first-layer chip, the second-layer chip and the third-layer chip. The three-dimensional chip testing method and the three-dimensional chip testing device have the advantages that testing of each chip before binding and the three-dimensional chip obtained after binding of the chips is achieved; the feature analyzers for chip testing are arranged inside the three-dimensional chip, so that the chips can be detected in real time, storage of a great number of data is unneeded, storage capacity is reduced and testing overheads are lowered.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

An embedded boundary scan data compression and synthesis method and device

ActiveCN103675650BReduce data volumeSave storage spaceElectronic circuit testingData compressionComputer hardware

The invention discloses an embedded boundary scan data compression and synthesis method and device. The method comprises the steps of: obtaining a standard scan chain data; obtaining a pin data used in the test, a test matrix and a response matrix; storing the standard scan chain data, the pin data used in the test, the test matrix and the response matrix into the chip of the embedded test device; obtaining the standard scan chain data, the pin data used in the test, the test matrix and the response matrix stored in the chip; calculating the position of the scan unit on the standard scan chain data of each pin used in the test to use the vector synthesis standard scan chain data in the test matrix and the vector synthesis standard scan chain data in the response matrix. The method and device effectively solves the problems of small storage space and being unable to conduct the boundary scan test of a large quantity of data of the test device. The data quantity of the boundary scan datum is effectively compressed, storage space is saved, test time and cost are reduced, and production efficiency is increased.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

A Three-Order Symptom Test Method Combined with Parity Check

InactiveCN102981923BReduce testing overheadReduce resource requirementsRedundant data error correctionTest efficiencyComputer hardware

Owner:SHANGHAI UNIV

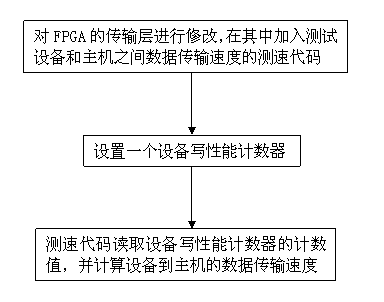

Method of testing the speed of data transmission from PCI Express equipment to host on the basis of FPGA (field programmable gate array)

InactiveCN103324558AImprove test accuracyFast testDetecting faulty computer hardwarePCI ExpressData transmission

The invention discloses a method of testing the speed of data transmission from PCI Express equipment to a host on the basis of FPGA (field programmable gate array). The method includes the steps of S1, modifying an FPGA transmission layer, adding a speed measurement code, for the speed of data transmission between test equipment and the host, into the FPGA transmission layer; S2, setting an equipment writing performance counter; S3, allowing the speed measurement code to read a counted value of the equipment writing performance counter, and calculating the speed of data transmission from the equipment to the host according to the equation: S=V / (C / H)=V*H / (C / (P-1)*P). The method has the advantages that testing accuracy is high, measuring speed is high, testing objectivity is high, and testing cost is low.

Owner:CHENGDU LINHAI ELECTRONICS

Circuit ageing detection method based on self-oscillation circuit

InactiveCN103116121BAvoid interferenceReflect the actual aging degreeElectronic circuit testingStatic timing analysisNegation

The invention discloses a circuit ageing detection method based on a self-oscillation circuit. The method includes choosing an ageing characteristic access collection T in a to-be-detected circuit according to static timing analysis and correlation among ways, remaining logical negation with odd power on each to-be-detected way in the ageing characteristic access collection T to form the self-oscillation circuit, producing a detection vector quantity to excite the self-oscillation circuit to produce a detection level signal by means of a detection production method of a fixed-type fault, and obtaining a circuit ageing characteristic value through the fact that a counter samples the self-oscillation circuit and measuring the ageing degree of the to-be-detected circuit. The method can precisely measure the ageing degree of the circuit at low power consumption, and provides precise bases for circuit ageing failure protection.

Owner:HEFEI UNIV OF TECH

An integrated comprehensive road test instrument

ActiveCN111277339BReduce evaluation errorReduce testing overheadTransmission monitoringSignal onControl theory

The invention relates to the communication field, in particular to an integrated comprehensive drive test instrument. It is used to solve the problem of multiple network competition tests at the same time. The method is: the antenna matching circuit module is used to receive the total downlink signal sent by the same radio frequency antenna, and send each downlink signal after frequency band division to the terminal multi-module group The module is a terminal multi-module module, which is connected to the antenna matching circuit module and includes a first-type module set for receiving a downlink signal on a corresponding frequency band and testing and comparing service-related parameters. In this way, it is ensured that the downlink signals come from the same radio frequency antenna, the evaluation error caused by different radio frequency antennas is reduced, the accuracy of the test comparison of related parameters is improved, and the business correlation of different frequency bands belonging to multiple networks can be simultaneously Test and compare parameters, realize test comparison of various networks, reduce test overhead, simplify operation process, and improve the efficiency of test comparison.

Owner:CHINA MOBILE COMM LTD RES INST +1

Method for testing dispatching of on-chip systematic embedded logical core by multistage order algorithm

InactiveCN102012480BShorten test timeReduce testing overheadElectrical testingComputer hardwareSorting algorithm

The invention relates to a method for testing dispatching of an on-chip systematic embedded logical core by a multistage order algorithm. The operation method comprises the following steps of: establishing and initializing a dispatching matrix Z; line expanding the dispatching matrix Z; line contracting the dispatching matrix X; two-dimensionally dispatching and sequencing the total testing band width to the total testing time (W-T) of the dispatching matrix Z; double-traversing a total testing band width-adjusting factor (W-alpha) of the dispatching matrix Z; and generating a report. The invention is capable of effectively and integrally solving the two independently problems of the test dispatching of the on-chip systematic embedded logical core and the test link chaining in the logical core, thereby effectively reducing the testing time and testing cost of the on-chip system. The method is convenient in operation, and is applicable to various on-chip systems for finishing the measurability design of the logical core by scanning chain.

Owner:SHANGHAI UNIV