Testing device for a memory chip in a hybrid circuit

A memory chip and test device technology, applied in static memory, instruments, etc., can solve problems such as hard-to-fail memory fault location and diagnosis, functional test vector development and debugging difficulties, and the inability to directly apply hybrid integrated circuits, etc., to achieve easy test generation , the effect of small test vector size and small external resource overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The technical solution of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

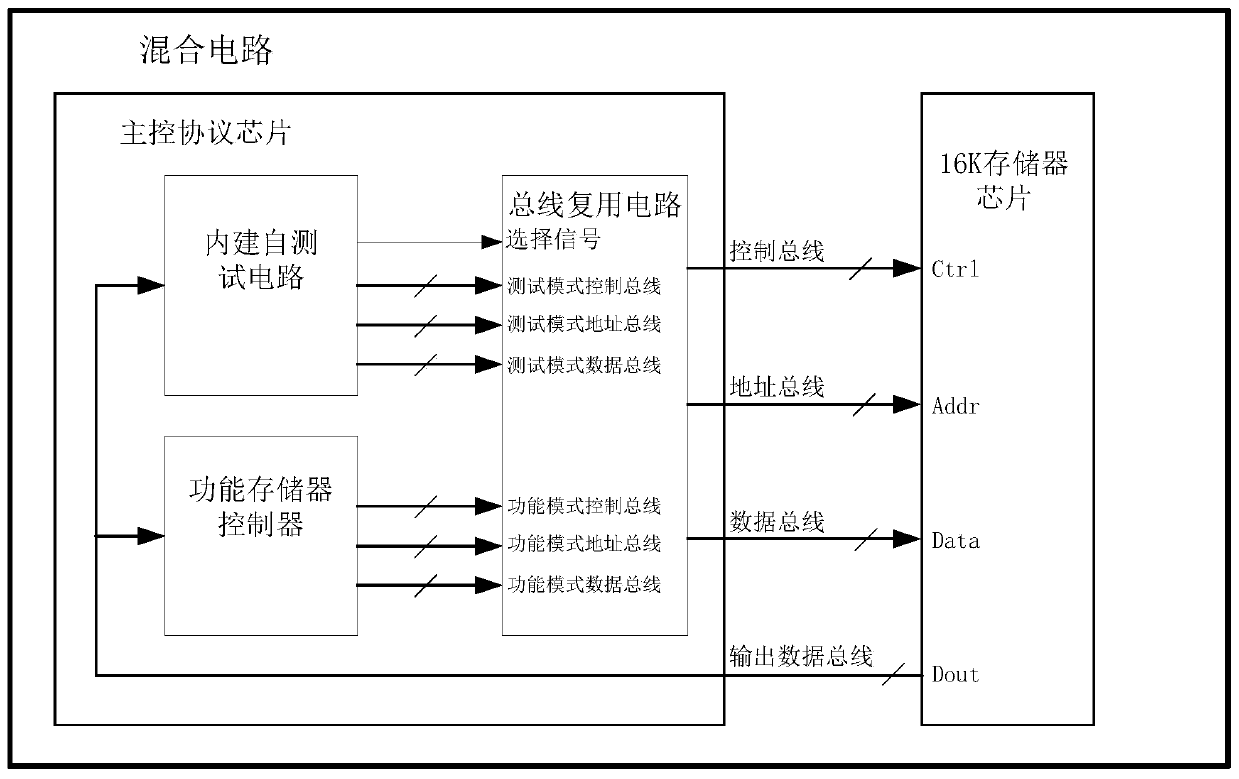

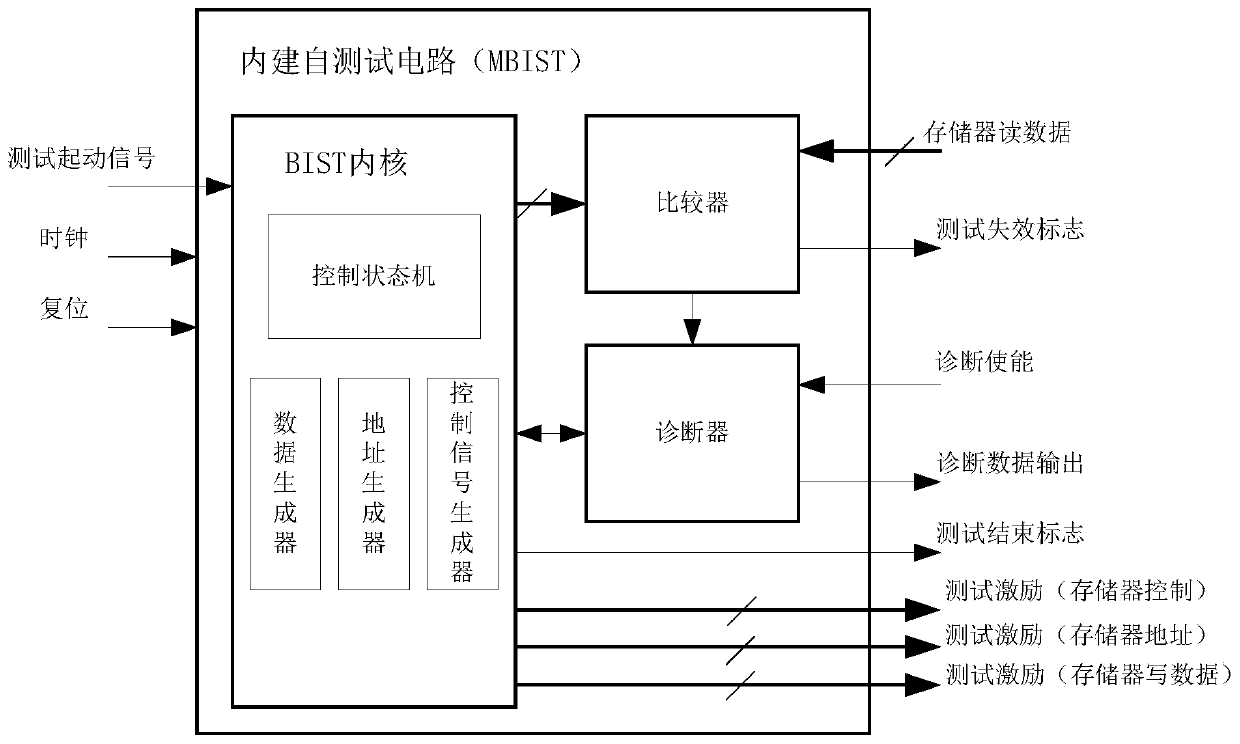

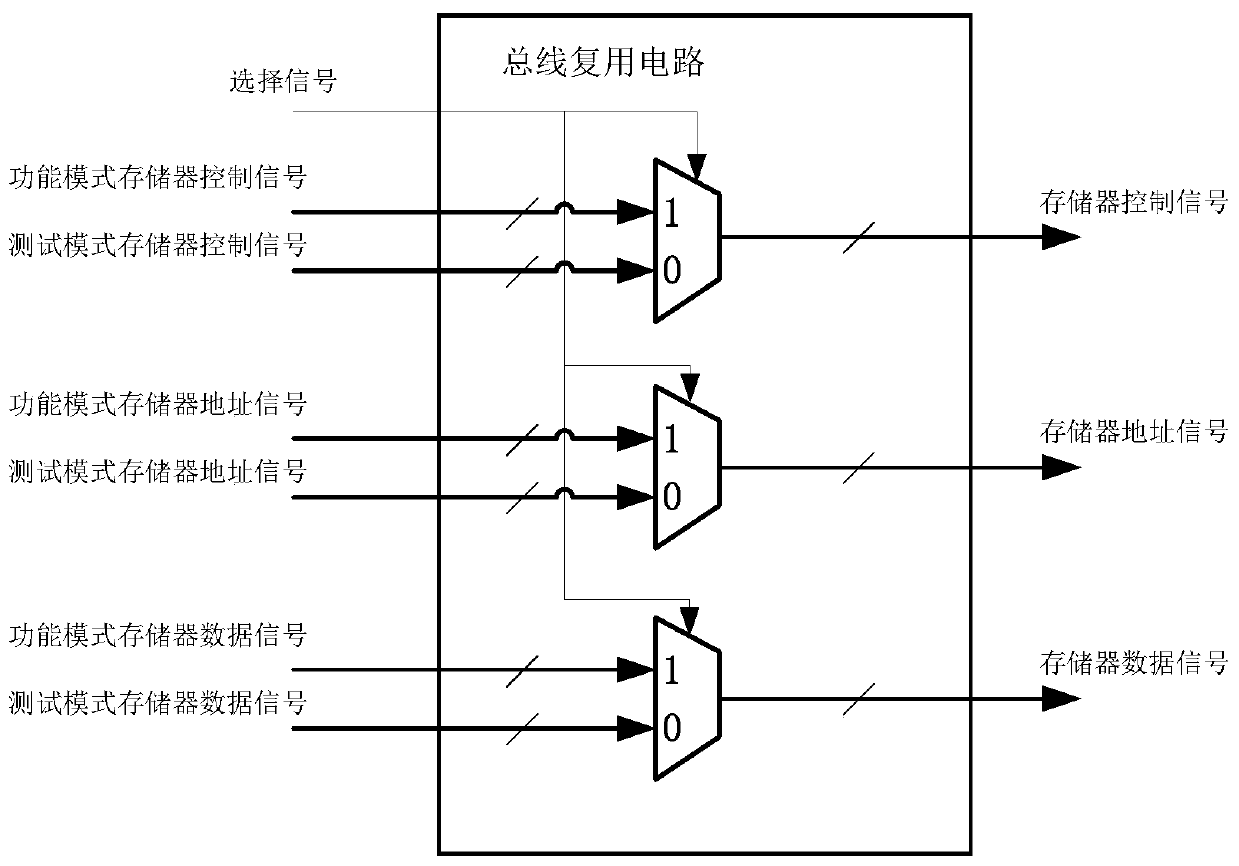

[0019] The invention provides a test device for a memory chip in a hybrid circuit. The device utilizes the characteristics of data interaction between the memory chip and the main control protocol chip in the hybrid circuit, designs a built-in self-test circuit in the main control chip of the hybrid circuit, and multiplexes The function data and the control bus are used to realize the test access to the memory chip. The test device mainly includes a built-in self-test circuit and a bus multiplexing circuit.

[0020] Such as figure 1 As shown, the device includes a built-in self-test circuit, a functional memory controller and a bus multiplexing circuit, and the built-in self-test circuit, a functional memory controller and a bus multiplexing circuit are arranged on the main control protocol chip; at the same time, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More