Method for testing dispatching of on-chip systematic embedded logical core by multistage order algorithm

A technology of logic core and sorting algorithm, which is applied in the field of test scheduling of embedded logic core in system-on-chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

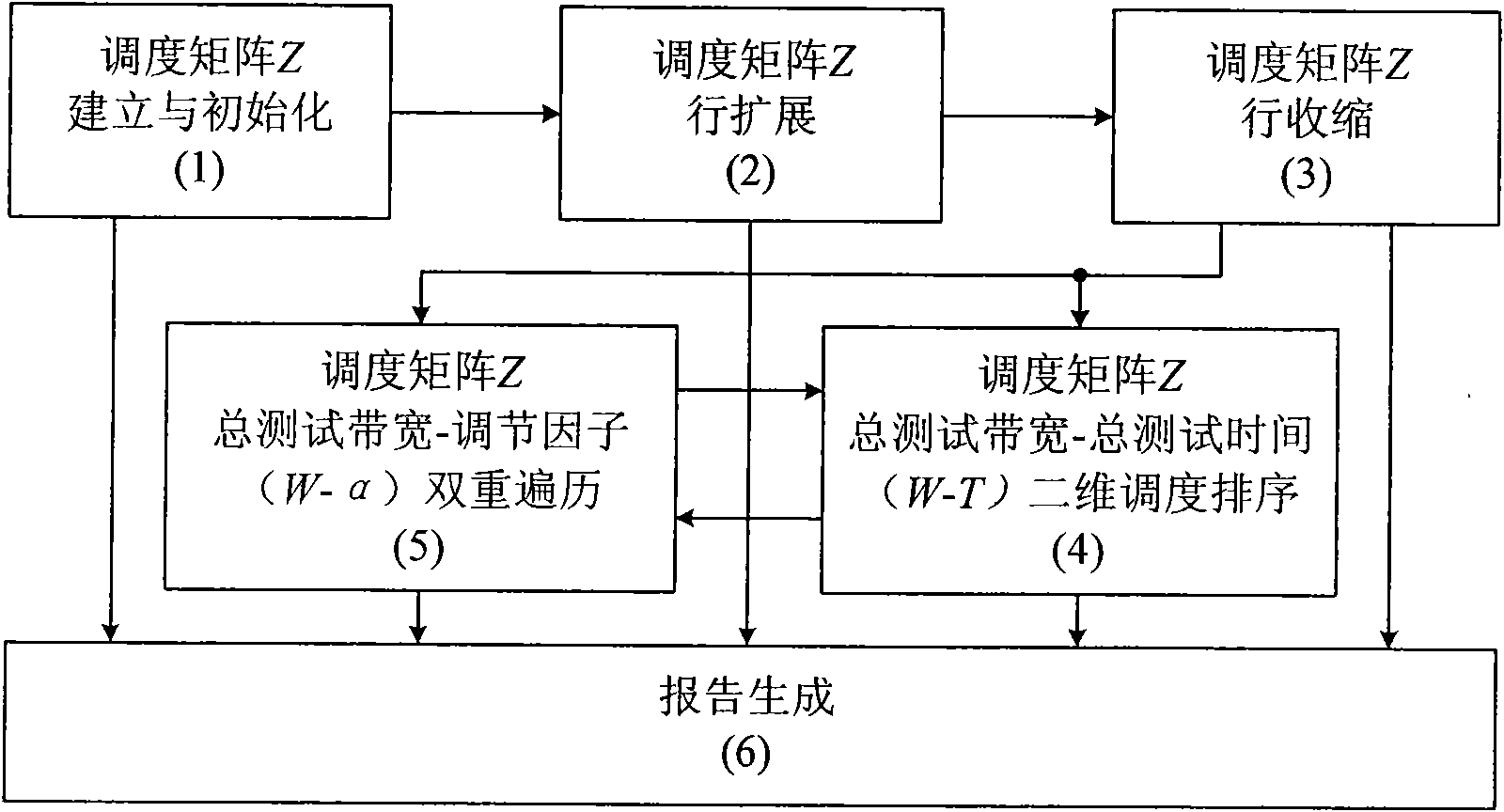

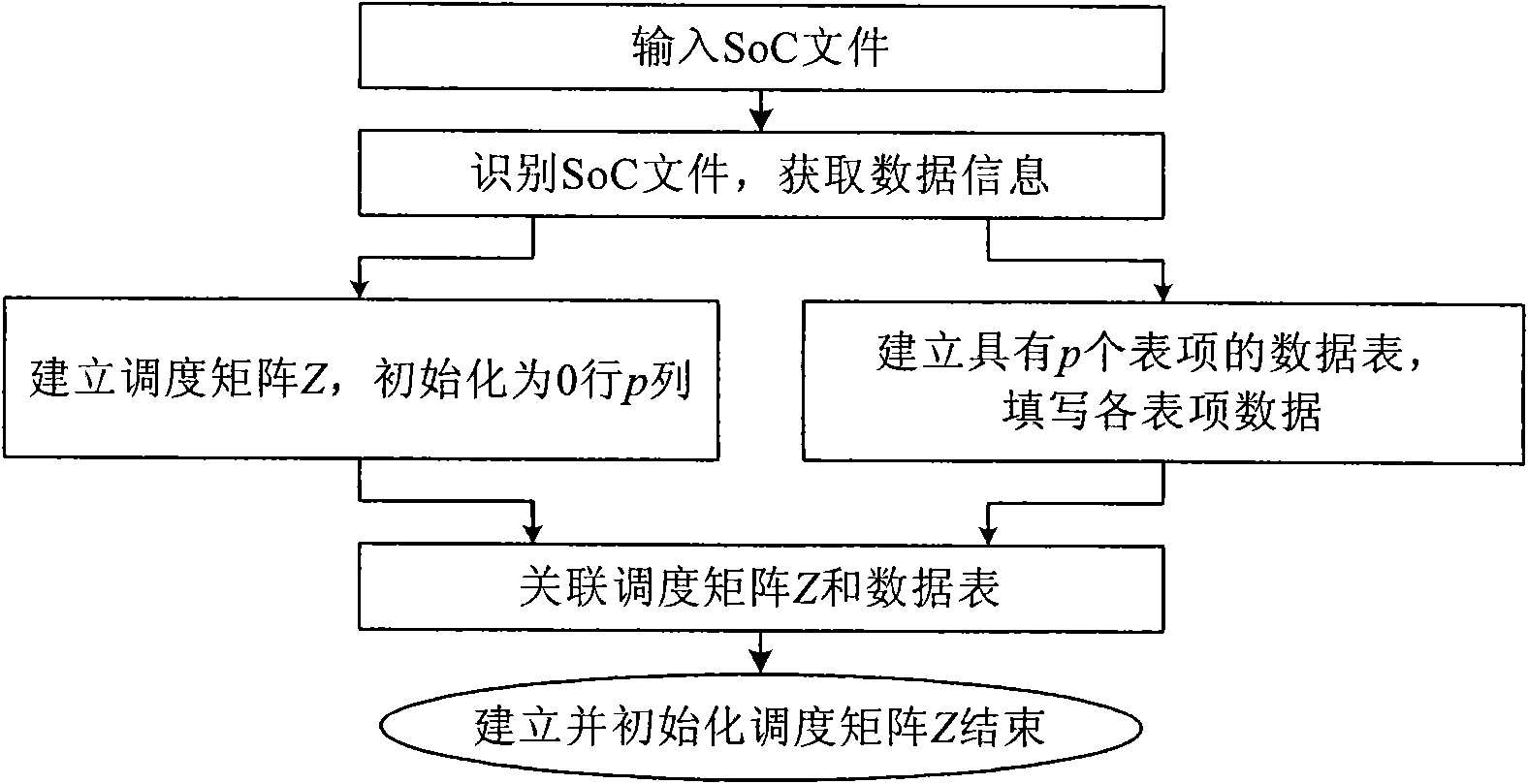

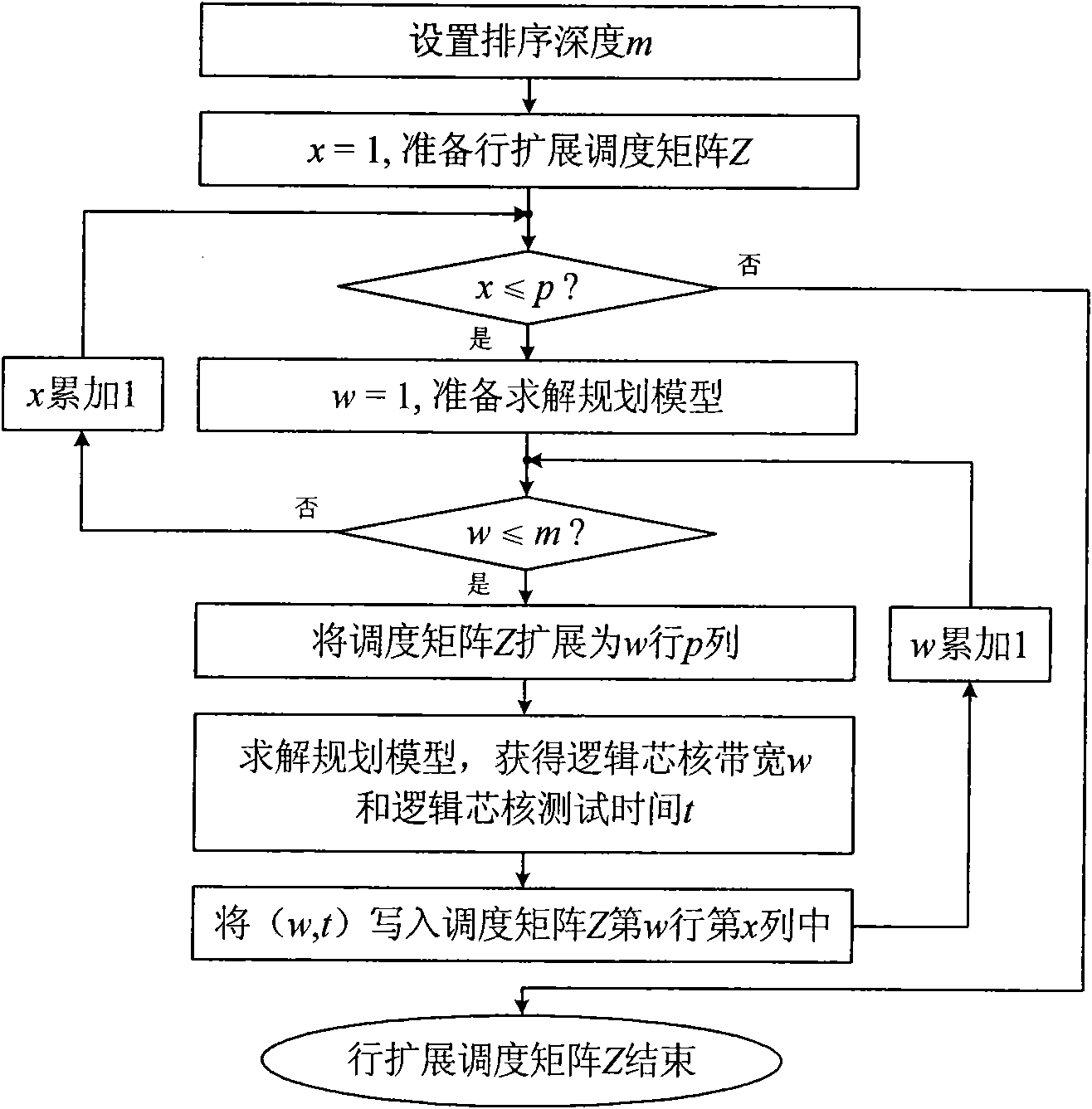

[0044] A preferred embodiment of the present invention is: see figure 1 , the method of applying the multi-level sorting algorithm to the test scheduling of the embedded logic core of the system on chip, which reads in the SoC file, sets the sorting depth and the priority standard, and uses the multi-level sorting algorithm to obtain the optimal logic core test scheduling. The logic core test scheduling results of the logic core, the operation steps are (1) scheduling matrix Z establishment and initialization, (2) scheduling matrix Z row expansion, (3) scheduling matrix Z row contraction, (4) scheduling matrix Z total test bandwidth - total Test time (W-T) two-dimensional scheduling sorting, (5) double traversal of scheduling matrix Z total test bandwidth-adjustment factor (W-α) and (6) report generation; step (1) scheduling matrix Z establishment and initialization are: read SoC file, which conforms to the SoC file format formulated by ITC'02 (International TestConference 200...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More