Logic optimizing and parallel processing method of integrated circuit

A parallel processing and logic optimization technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as load balancing problem improvement, and achieve the effect of reducing parallel processing time and improving processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

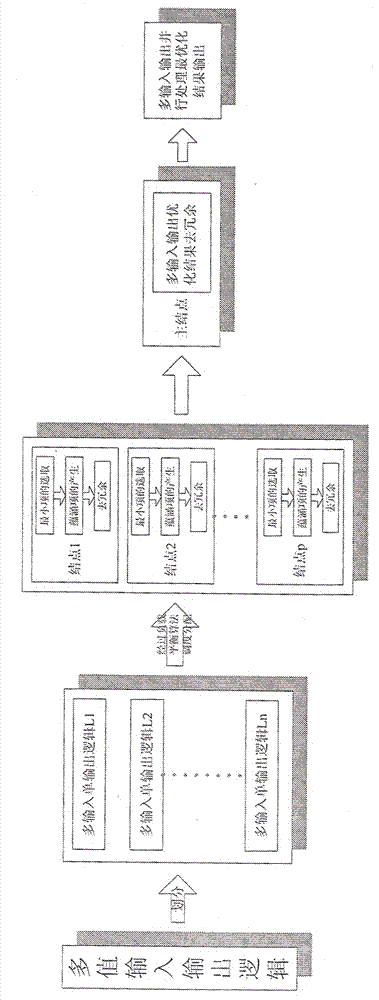

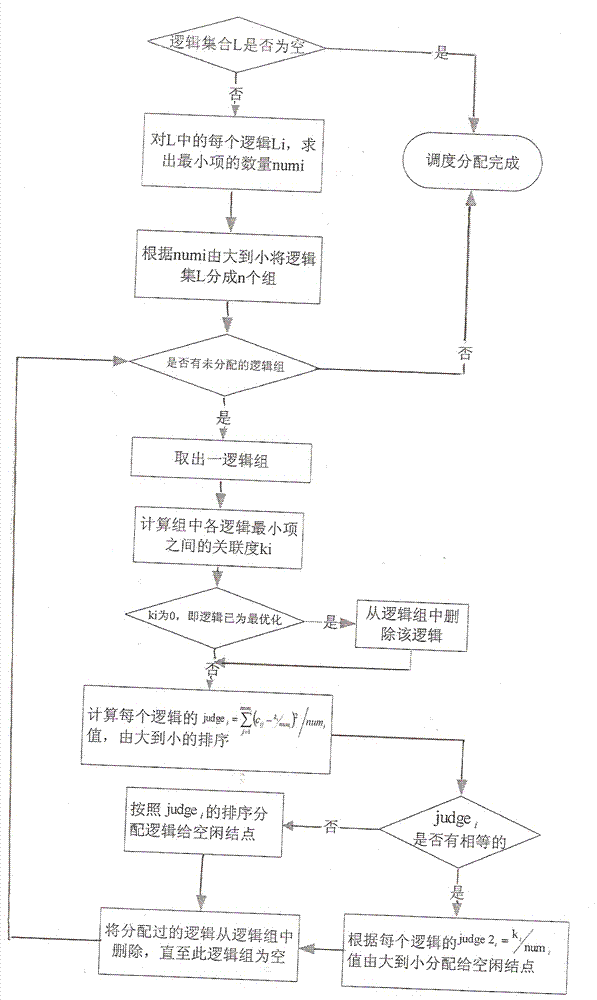

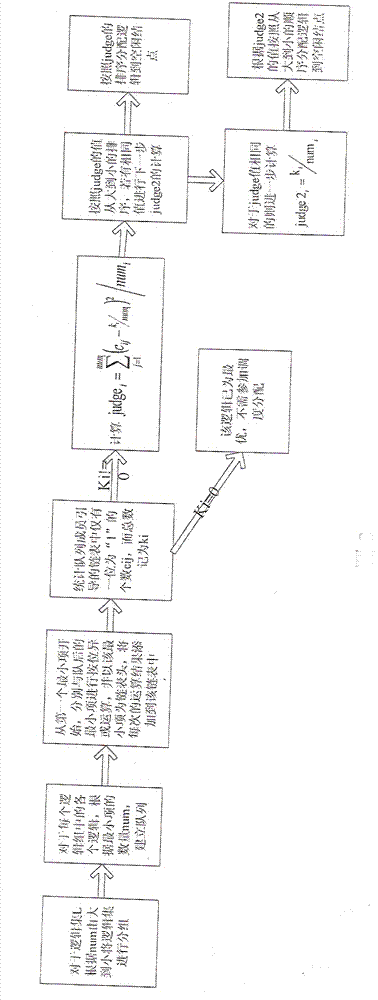

Method used

Image

Examples

example

[0040] There is a logic function F(x) with four inputs and eight outputs,

[0041] f 1 = x 2 ‾ x 3 x 4 + x 1 ‾ x 3 ‾ x 4 ‾ + x 1 x 2 x 3 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More