A planar semiconductor thermoelectric chip and its preparation method

A semiconductor, planar technology, used in the manufacture/processing of thermoelectric devices, thermoelectric devices using only the Peltier or Seebeck effect, etc. There are no problems such as complete isolation, to achieve the effect of increasing the number of thermocouple pairs, good temperature distribution characteristics, and good process compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0091] The thermocouple material is P-type polysilicon and N-type polysilicon, the support layer is Pyrex7740 heat-resistant glass, and the bonding method is silicon-glass anode bonding.

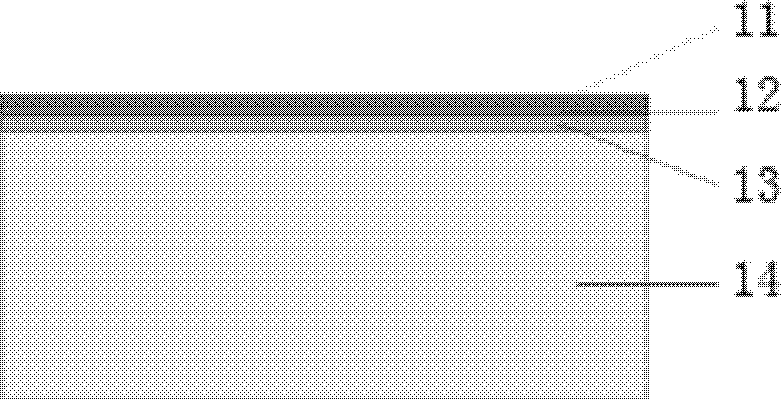

[0092] 1) Take (100) silicon wafer 14 (single crystal silicon), and grow silicon oxide 13, silicon nitride 12, and polysilicon film (11) on the front surface of the silicon wafer by thermal oxidation and two LPCVD methods. See diagram 2-1 .

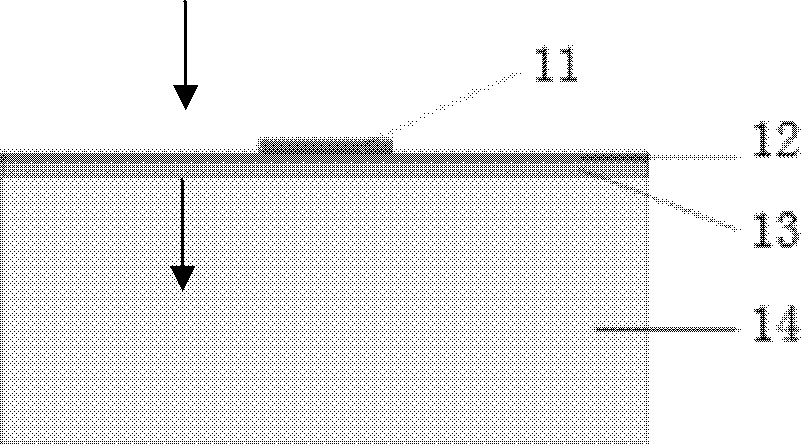

[0093] 2) Perform P-type and N-type ion doping on polysilicon, and dry etching to form two types of resistors, P and N. See Figure 2-2 .

[0094] 3) Aluminum 15 is sputtered and alloyed after wet etching to form an aluminum electrode to realize the electrical connection of the thermocouple pair. See Figure 2-3 .

[0095] 4) Dry etching of silicon nitride and silicon oxide to expose the silicon substrate and reserve a bonding area. See Figure 2-4 .

[0096] 5) Take a Pyrex7740 glass sheet 16, perform isotropic wet etching on the surface, and...

Embodiment 2

[0105] The thermocouple material is polysilicon and metal aluminum, and its specific implementation steps are basically the same as in Example 1. The main difference is that in step 2, the polysilicon film is ion-doped once to make it conductive, and in step 3, aluminum is patterned to form electrodes. Corresponding thermocouples are also formed, paired with polysilicon resistors to form thermocouple pairs, and the rest remain unchanged.

Embodiment 3

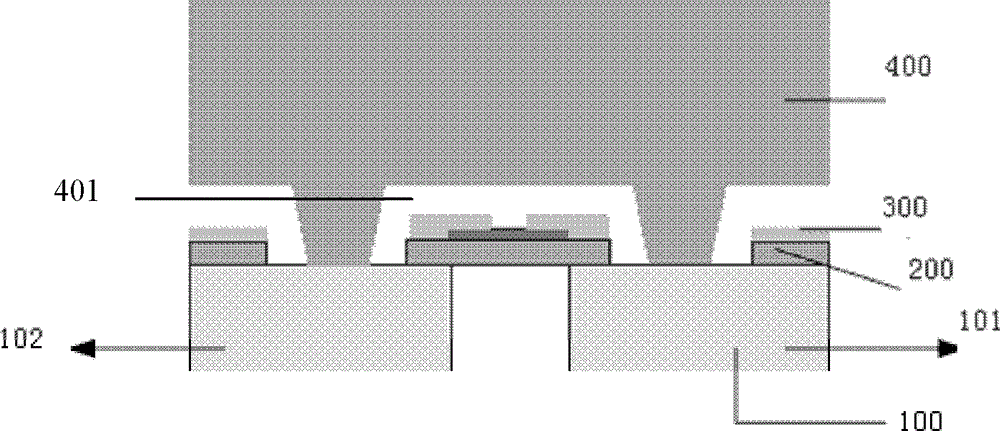

[0107] The lower support layer is added to the structure of Example 1. The specific implementation steps are basically the same as in Example 1. After step 6, a bonding process is added to realize bonding with the lower heat-insulating support layer. The material of the support layer is Pyrex7740 heat-resistant glass. See Figure 4 .

[0108] The present invention proposes a planar thermoelectric chip structure and a manufacturing method. The thermoelectric chip structure includes four parts: a heat conduction layer, an electrical insulation layer, a power generation layer, and a support layer. On the support layer, the middle part of the heat conduction layer is made into a comb-tooth structure, and an electrical insulation layer is made on the surface. The two ends of the thermocouple arms on the electrical insulation layer are connected to the adjacent comb-tooth arms. The leads are connected to form the power generation layer, such as figure 1 , as shown in Figure 2.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More