High duty cycle ddr2 digital delay chain circuit

A delay chain, duty cycle technology, applied in high-speed DDR, DDR3 digital circuit design, DDR2 field, can solve the problem of low frequency of digital delay chain application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

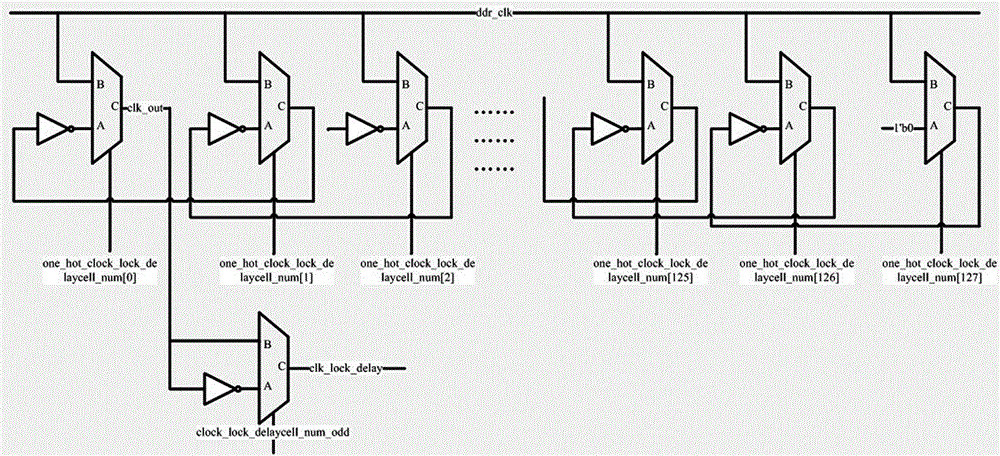

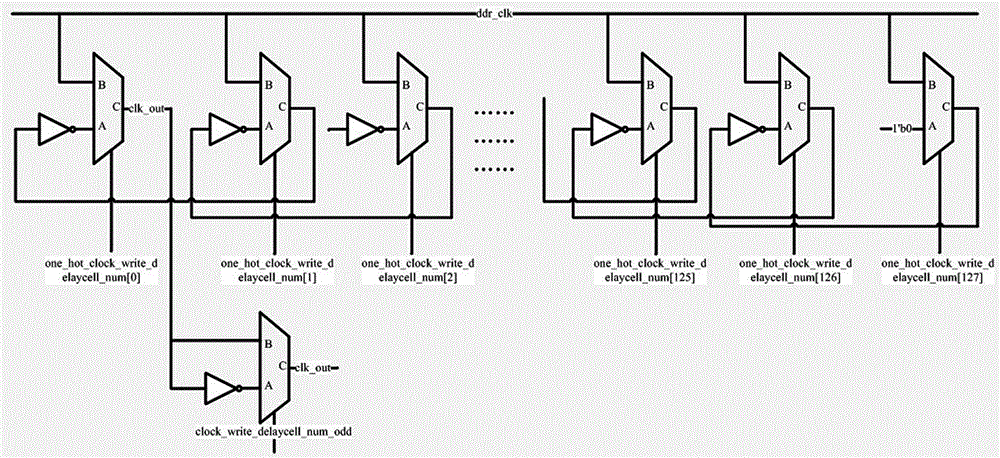

Embodiment Construction

[0038] The present invention will be described in detail below with reference to the drawings and specific embodiments. In this paper, a 128-level digital delay chain is used. The DDR2 system clock cycle is 3.75ns, the frequency is 266Mhz, the DDR2 memory is 533Mhz, the bit width of the DDR2 system configurable phase offset register is 8 bits, and the delay of each digital delay unit is 0.1ns. The initial delay stages of the clock-locked digital delay chain are 11. As an embodiment, the described embodiment is only one embodiment of the present invention, not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

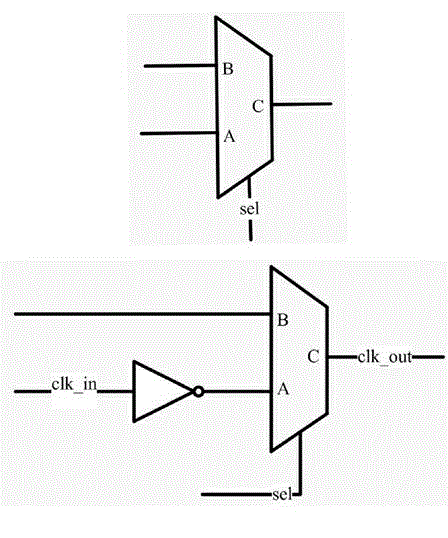

[0039] The implementation of the present invention discloses a high duty ratio DDR2 digital delay chain circuit, comprising: a digital delay unit, a clock-locked digital delay chain, a write oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com