Power and area efficient interleaved ADC

A multiplexer, hold circuit technology, applied in the direction of analog/digital conversion, code conversion, electrical components, etc., can solve problems such as doubling power consumption and increasing noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

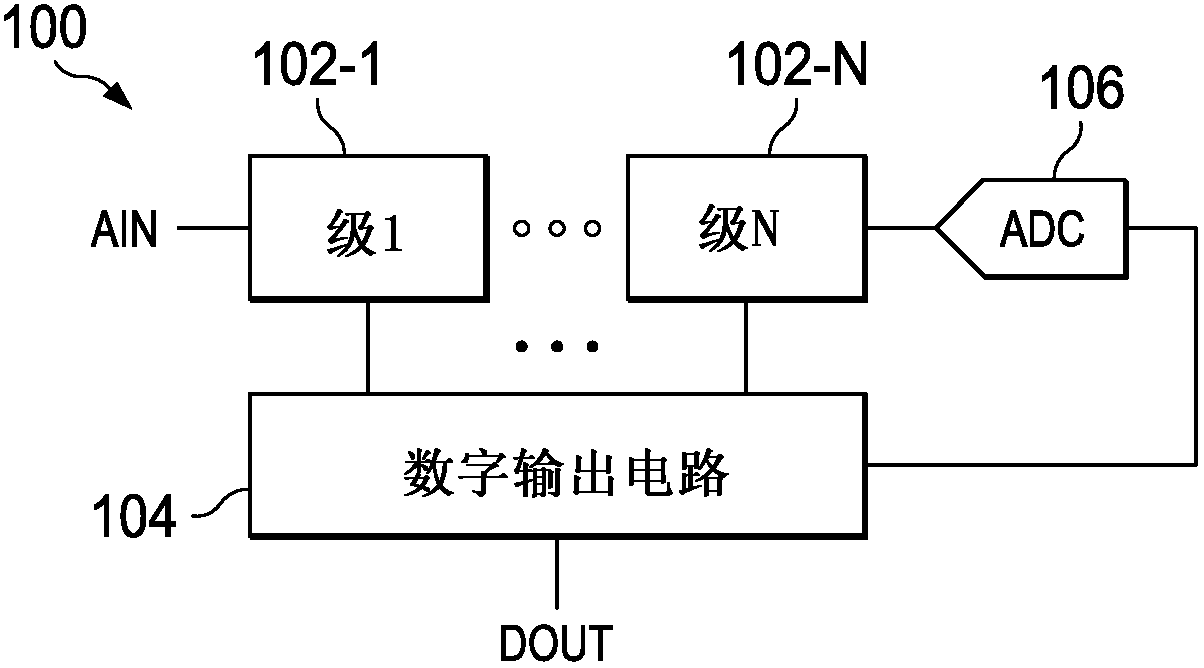

[0027] exist Figure 3A In , an ADC 300 according to an exemplary embodiment of the present invention is presented. ADC 300 has substantially the same functionality as ADC 100 . However, there is a difference in the pipeline; that is, stages 102-1 to 102-N are replaced by stages 302-1 to 302-N and clock circuit 303.

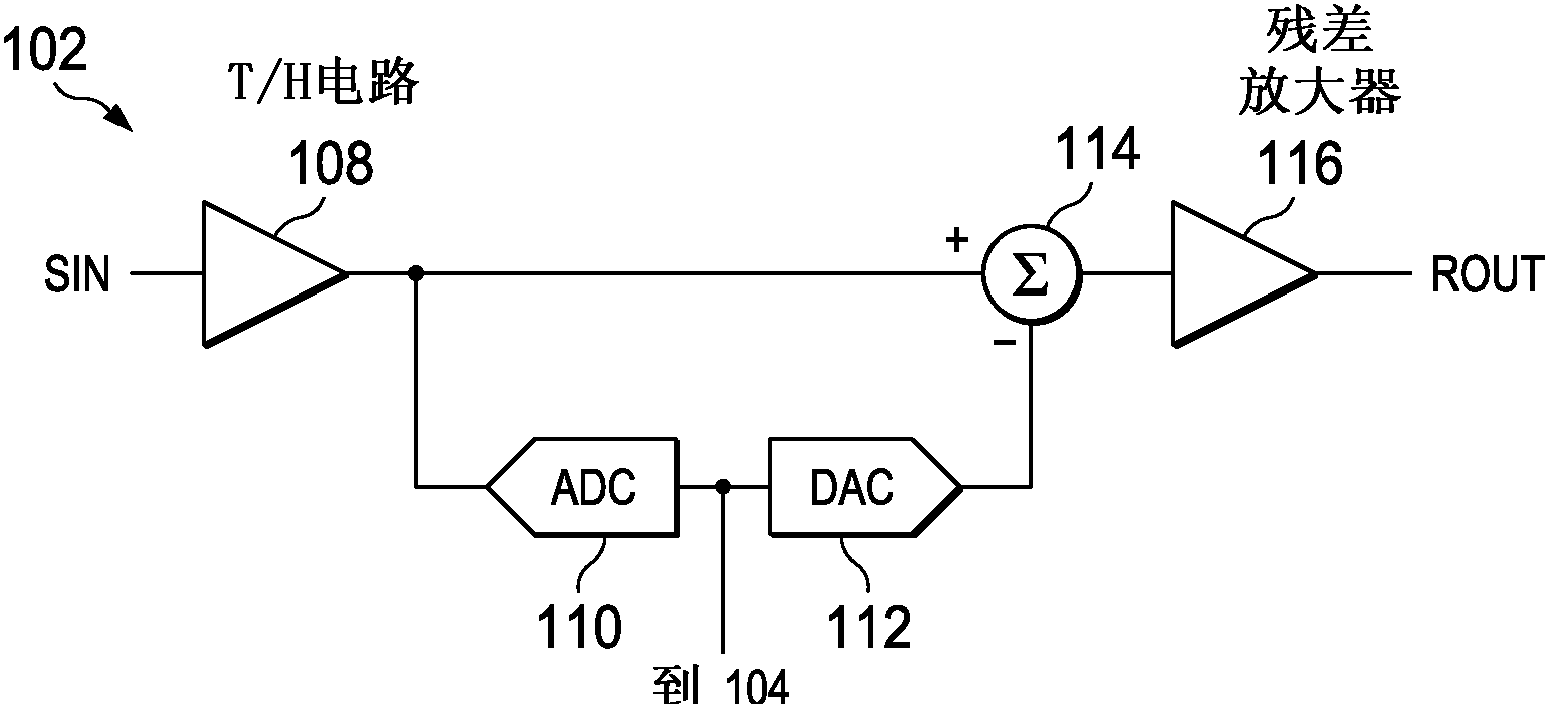

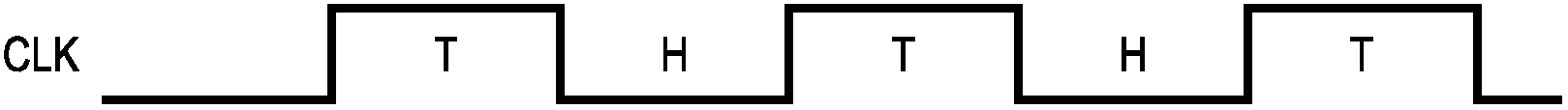

[0028] refer to Figure 3B and Figure 3C, stages 302-1 to 302-N (hereinafter 302) can be seen in more detail. In operation, T / H circuits 304 and 306 are coupled to receive an analog input signal (analog input signal AIN or a residual signal from a previous stage). Since these T / H circuits 304 and 306 are arranged in parallel with each other, the timing of the T / H circuits 304 and 306 can be designed such that sampling occurs on substantially non-overlapping logic stages or phases of the clock signal. Preferably, the clock circuit 303 generally includes a clock divider (ie, a clock divider with a frequency divided by 2) to generate a clock signal CLK / 2 with a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More