Address alignment SIMD (Single Instruction Multiple Data) acceleration method of array addition operation assembly library program

An address alignment and assembly library technology, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as insignificant optimization effect and difficulty in popularization and application.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

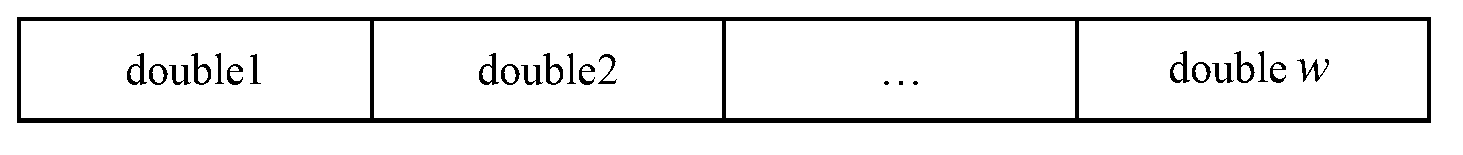

[0125] figure 1 Example for vector register format

[0126] The illustrated vector register includes w double-precision floating-point components, that is, the vector width is w, and the data width size is the number of bytes occupied by the double-precision floating-point type.

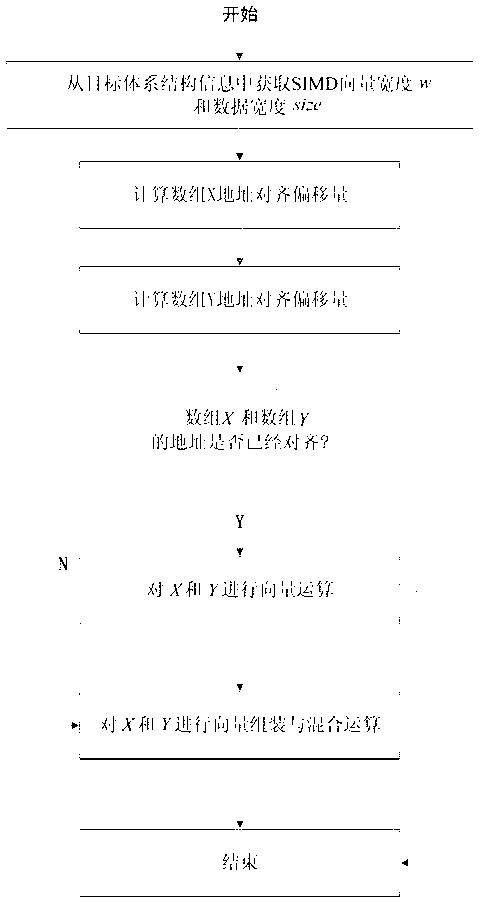

[0127] figure 2 Is the general flowchart of the present invention. The present invention comprises the following steps:

[0128] Step 1: Obtain the SIMD vector width w and data width size from the target architecture information.

[0129] Step 2: Calculate the array X address alignment offset.

[0130] Step 3: Calculate the array Y address alignment offset.

[0131] Step 4: Determine whether the addresses of array X and array Y are aligned according to the address alignment offset. If they are aligned, execute step 5; otherwise, execute step 6.

[0132] Step 5: Perform vector operations on X and Y.

[0133] Step 6: Carry out vector assembly and mixed operations on X and Y.

[0134] Step Seve...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap