phase locked loop

A technology of phase-locked loop and frequency and phase detector, which is applied in the field of phase-locked loop circuit design, can solve the problems of control voltage Vctrl fluctuations and influence on the stability of the phase-locked loop, and achieve frequency stability and loop stability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

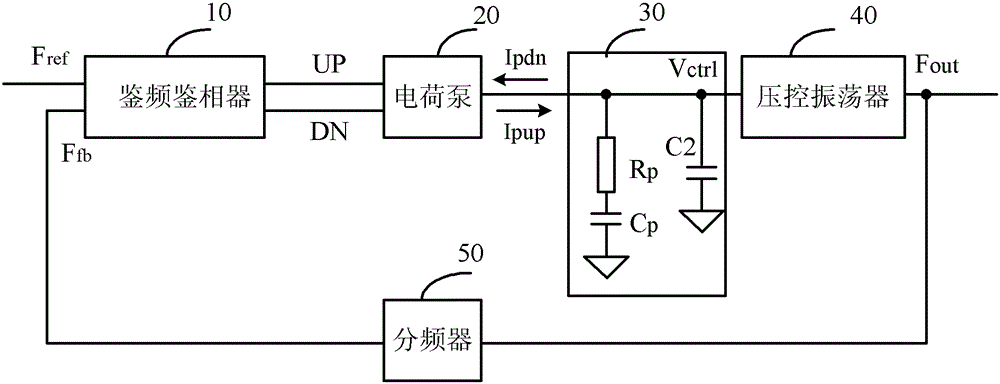

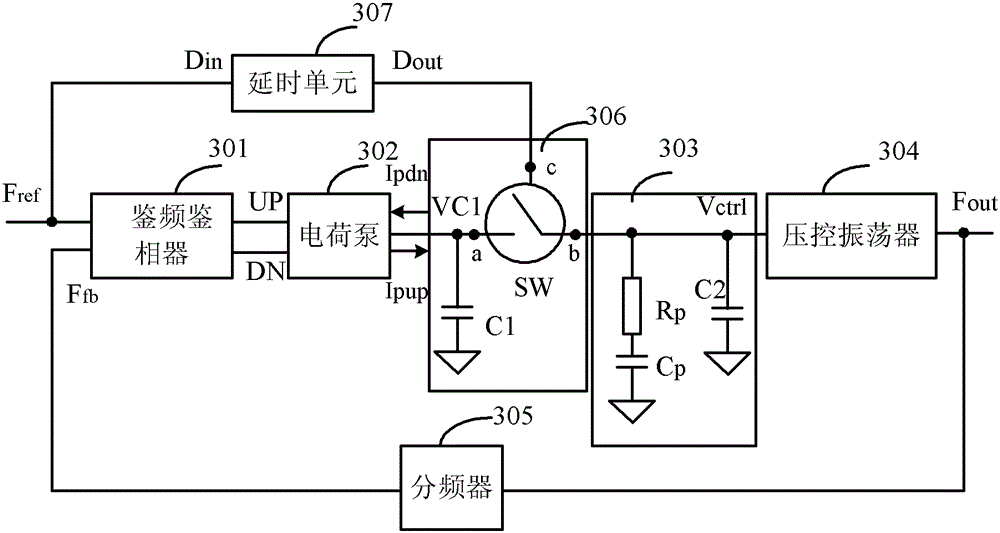

[0032] When the phase-locked loop is locked, ideally, the frequency and phase of the reference clock Fref and the feedback signal Ffb are consistent, but in practical applications, due to the characteristics of the device in the Influenced by factors such as mismatch and leakage current, when the PLL is locked, the frequencies of the feedback signal Ffb and the reference clock Fref are equal, and the phase difference is a small constant value, generally less than 0.5 nanoseconds. Fluctuations in the control voltage Vctrl may be caused, causing unwanted spurs in the output signal Fout.

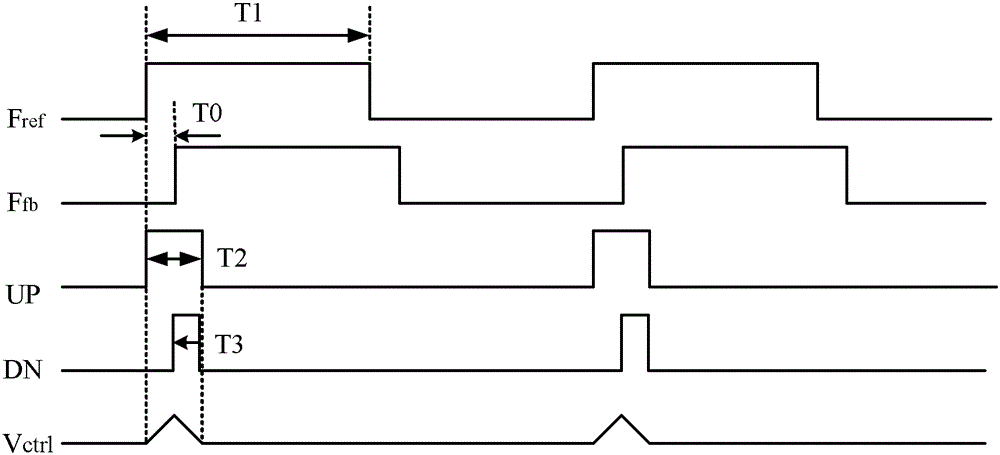

[0033] Please refer to figure 2 , figure 2 for figure 1 The shown schematic diagram of the pulse signal of the phase locked loop circuit in the locked state, including: an active high input signal Fref, a feedback signal Ffb, a pulse control signal UP, a pulse control signal DN and a control voltage output by the low-pass filter 30 Vctrl, the frequency of the output signal Fout is the same...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More