Network-on-chip-based many-core chip management structure fault tolerance method

An on-chip network and management method technology, applied in hardware redundancy for data error detection, response error generation, etc., can solve problems such as the scrapping of the entire chip and the inability to maintain the chip to continue to work.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

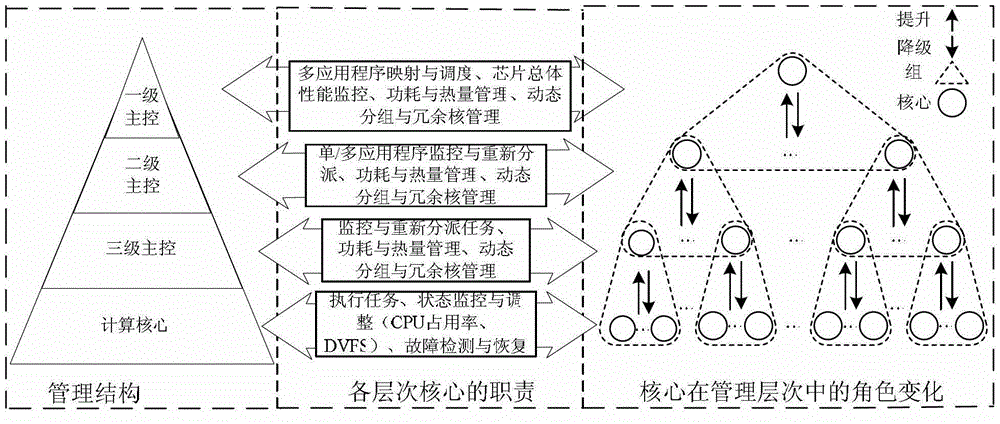

[0010] Specific implementation mode 1: The fault-tolerant method of many-core chip management structure based on network-on-chip described in this implementation mode,

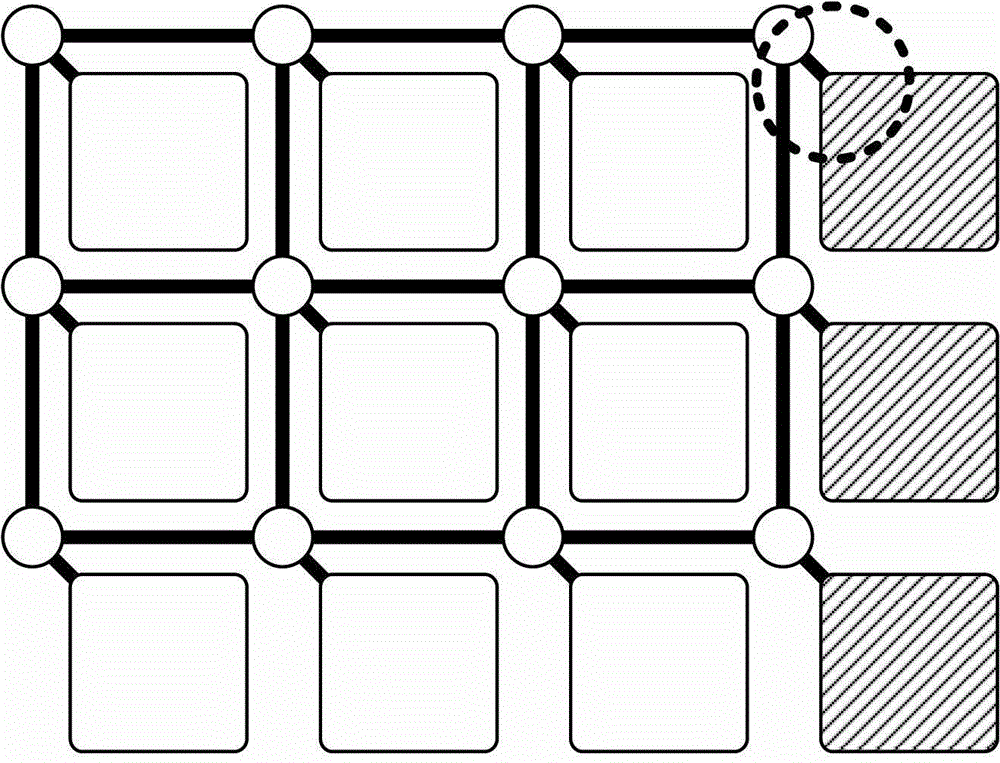

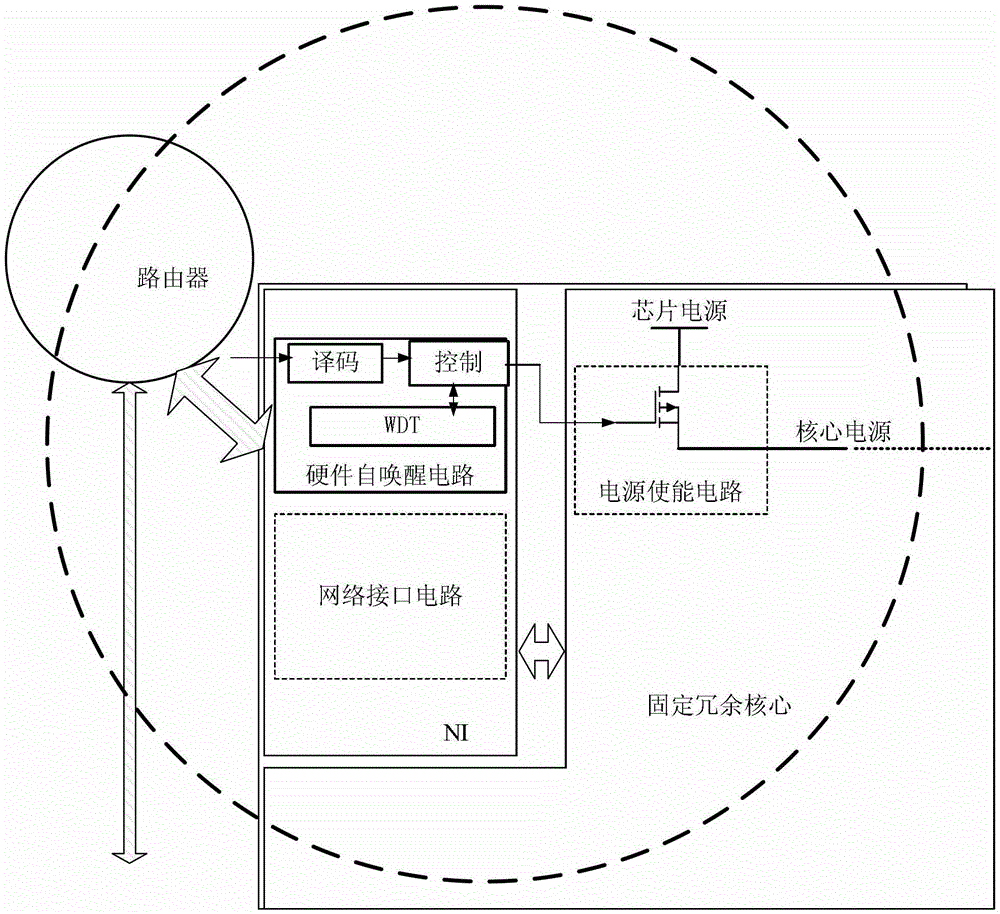

[0011] The network-on-chip-based many-core chip management structure includes multiple cores, the multiple cores include master control cores and redundant cores at various levels, and the redundant cores are divided into fixed redundant cores and dynamic redundant cores. Core, group the management structure of the chip, and use the management method of mutual monitoring within the group for each group; adopt the self-adaptive management method for all cores of the chip; use the election management method in each group; The core adopts the management method of hardware self-awakening, and the management method of software self-awakening is adopted for the dynamic redundant core.

specific Embodiment approach 2

[0012] Specific implementation mode two: combination figure 1 Describe this embodiment, this embodiment is to further limit the fault-tolerant method of the network-on-chip-based many-core chip management structure described in the first embodiment,

[0013] The method for grouping the management structure of the chip is as follows:

[0014] The chip management structure is grouped according to the jurisdiction areas of the main control cores at different levels: each group includes a group leader core and multiple team member cores, and the team leader core is the main control core at a certain level in the chip. If the team member core is at the bottom of the chip management structure, then the team member core is the computing core, otherwise, the team member core is the master control core of the next level of the team leader core; The main control core also includes a redundant core; the computing core also includes a redundant core;

[0015] Each group obtained after t...

specific Embodiment approach 3

[0018] Embodiment 3: This embodiment further limits the fault-tolerant method of the many-core chip management structure based on the network-on-chip described in Embodiment 2.

[0019] The method for adopting adaptive management to all cores of the chip is as follows:

[0020] The responsibilities of the main control core of each group at least include redundant core management and dynamic grouping, and all cores of the chip dynamically select a corresponding management method according to their current roles in the management hierarchy.

[0021] Such as figure 1 As shown, each level of the main control core has its own responsibilities.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More