Shifting register unit, gate driving circuit and display device

A shift register, gate connection technology, applied in the field of gate drive circuits, display devices, and shift register units, can solve the problems of complex structure, difficult to use number of transistors, etc., to simplify the structure, reduce the number of use, and reduce the number of Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

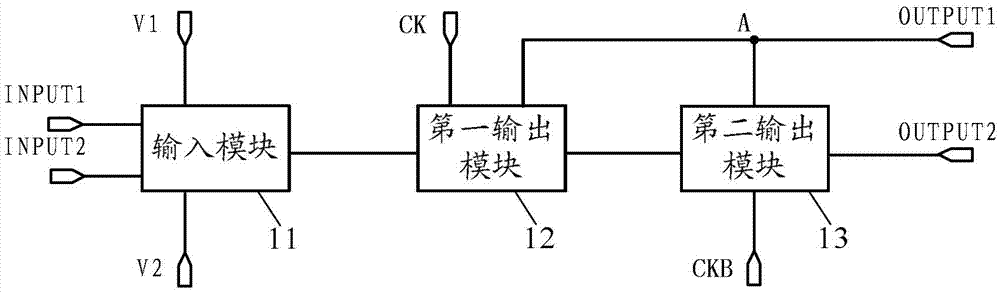

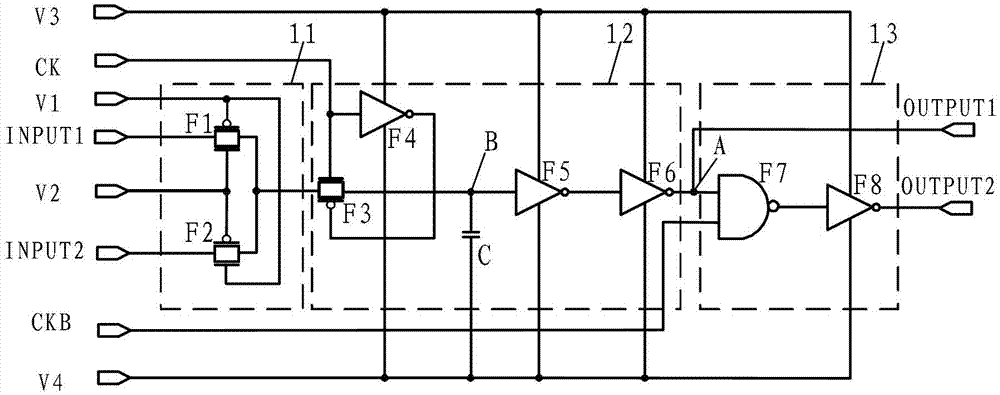

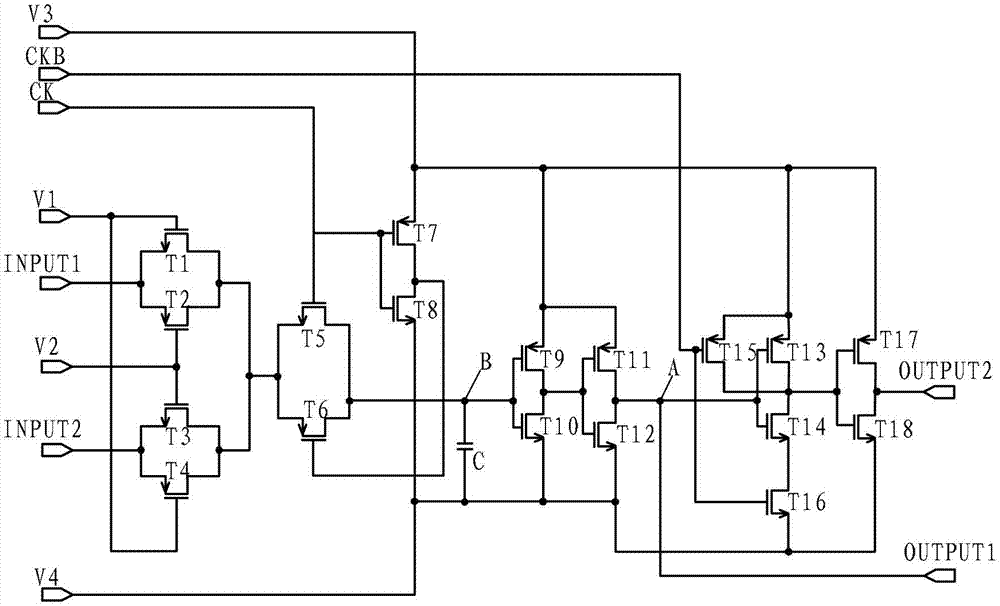

[0021] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. All other embodiments obtained by persons of ordinary skill in the art based on the embodiments of the present invention belong to the protection scope of the present invention.

[0022] The transistors used in all embodiments of the present invention can be thin film transistors or field effect transistors or other devices with the same characteristics. Since the source and drain of the transistors used here are symmetrical, there is no difference between the source and the drain. of. In the embodiment of the present invention, in order to distinguish the two poles of the transistor except the gate, one of the poles is called the first pole, and the other pole is call...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More