IRIG-B (Inter Range Instrumentation Group) encoding and decoding system and method based on FPGA (Field Programmable Gate Array)

A decoding system and encoding technology, applied in the application of multi-bit parity error detection coding, error correction/detection using block codes, data representation error detection/correction, etc., can solve the problem that the accuracy of decoding functions cannot be solved get test etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

[0040] Specific implementation mode one: see figure 1 Describe this embodiment, the FPGA-based IRIG-B code encoding and decoding system described in this embodiment includes GPS / Beidou dual system module 1, FPGA2, single-chip microcomputer 3, DAC chip 4, comparator chip 5, host computer 6 and PCI riser card 7,

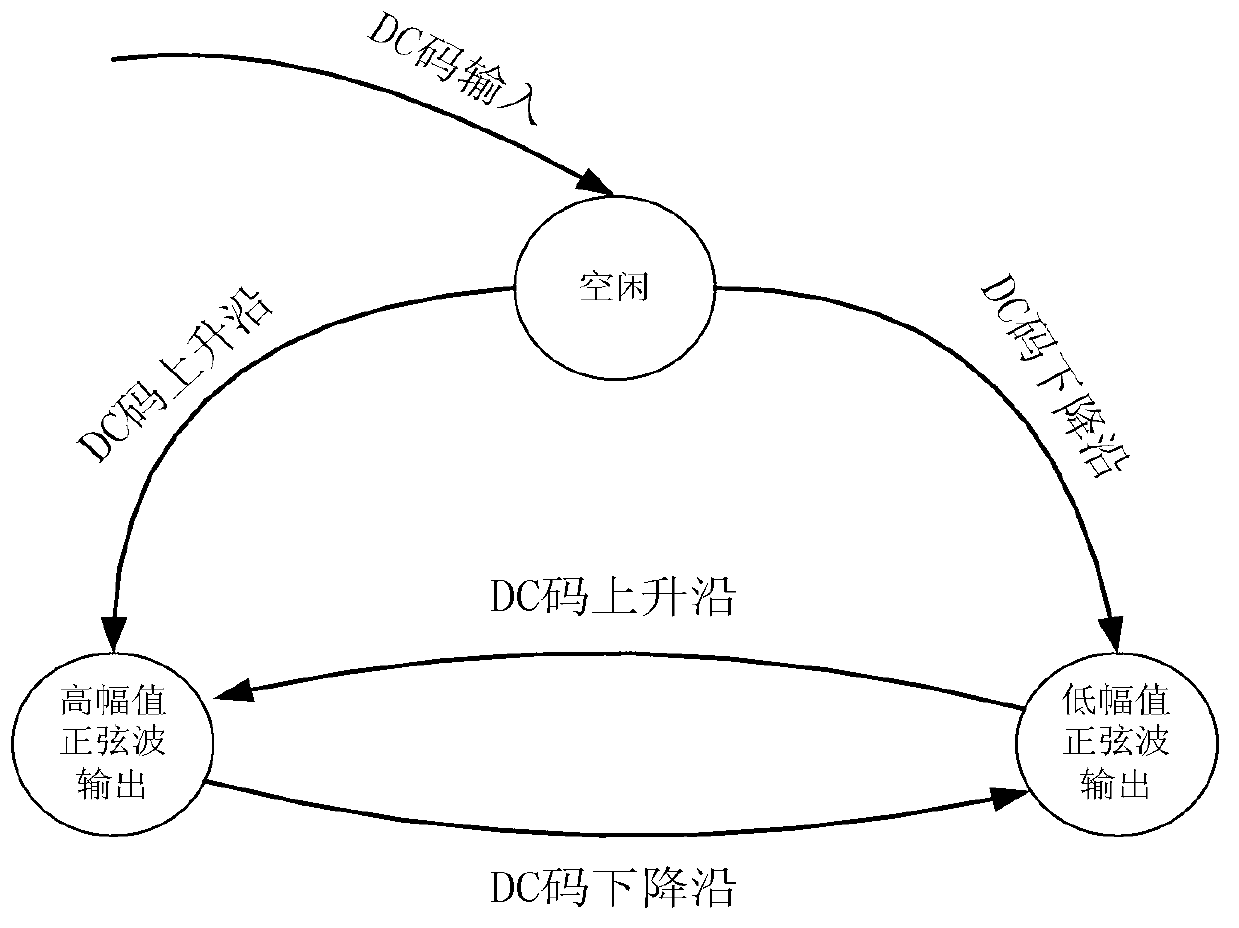

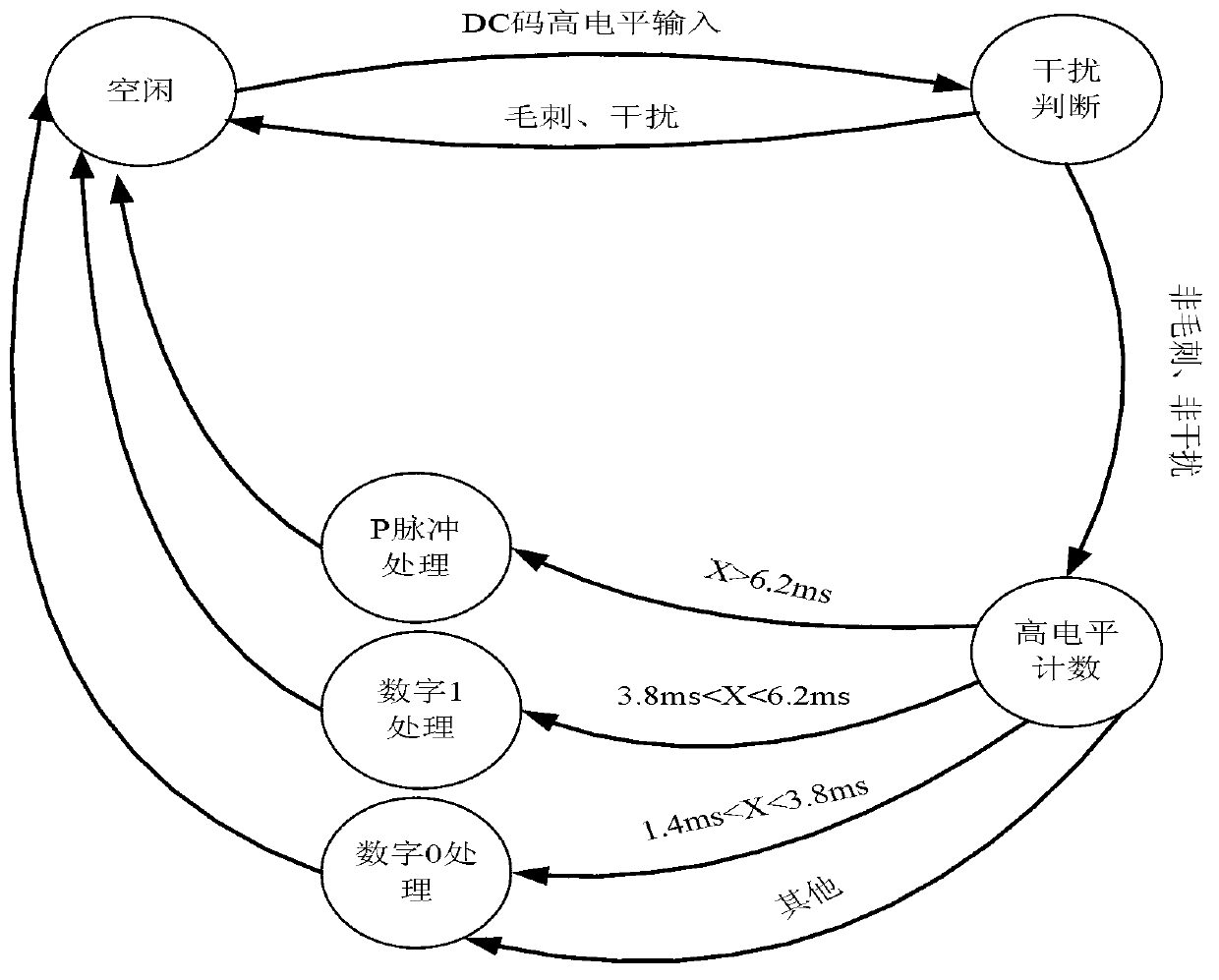

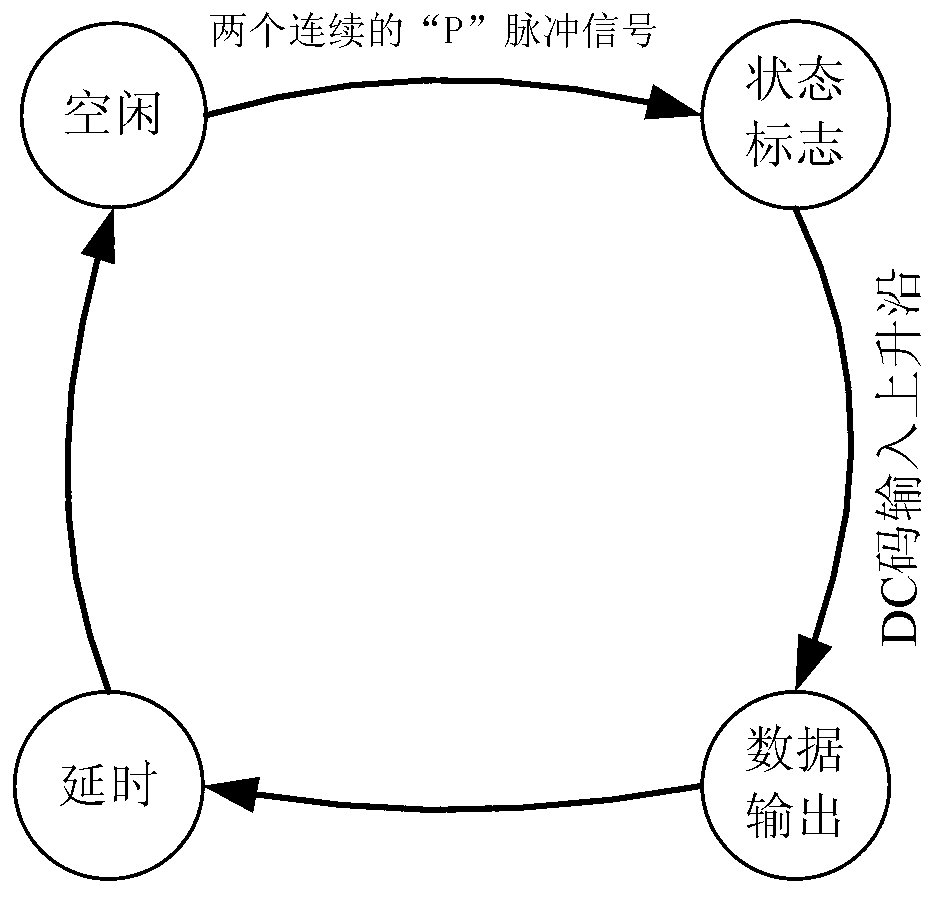

[0041] FPGA2 embedded storage control module 2-1, AC code encoding control logic module 2-2, DC code encoding control logic module 2-3, DC decoding control logic module 2-4 and AC code decoding control logic module 2-5 ,

[0042] The GPS / Beidou dual system module 1 is used to output time information and send it to the single-chip microcomputer 3 and the storage control module 2-1 at the same time,

[0043] The storage control module 2-1 is used to use the received time information as the original time source, and is also used to input the original time source to the host computer 6 through the PCI adapter card 7,

[0044] The single-chip microcomputer 3 is used for ...

specific Embodiment approach 2

[0053] Embodiment 2: This embodiment is a further limitation of Embodiment 1. The DAC chip 4 is realized by a DAC7714, and the DAC7714 is a 12-bit serial input D / A converter.

specific Embodiment approach 3

[0054] Embodiment 3: This embodiment is a further limitation of Embodiment 1. The comparator chip 5 is a zero-crossing comparator chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More