Patents

Literature

207results about How to "Implement self-test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

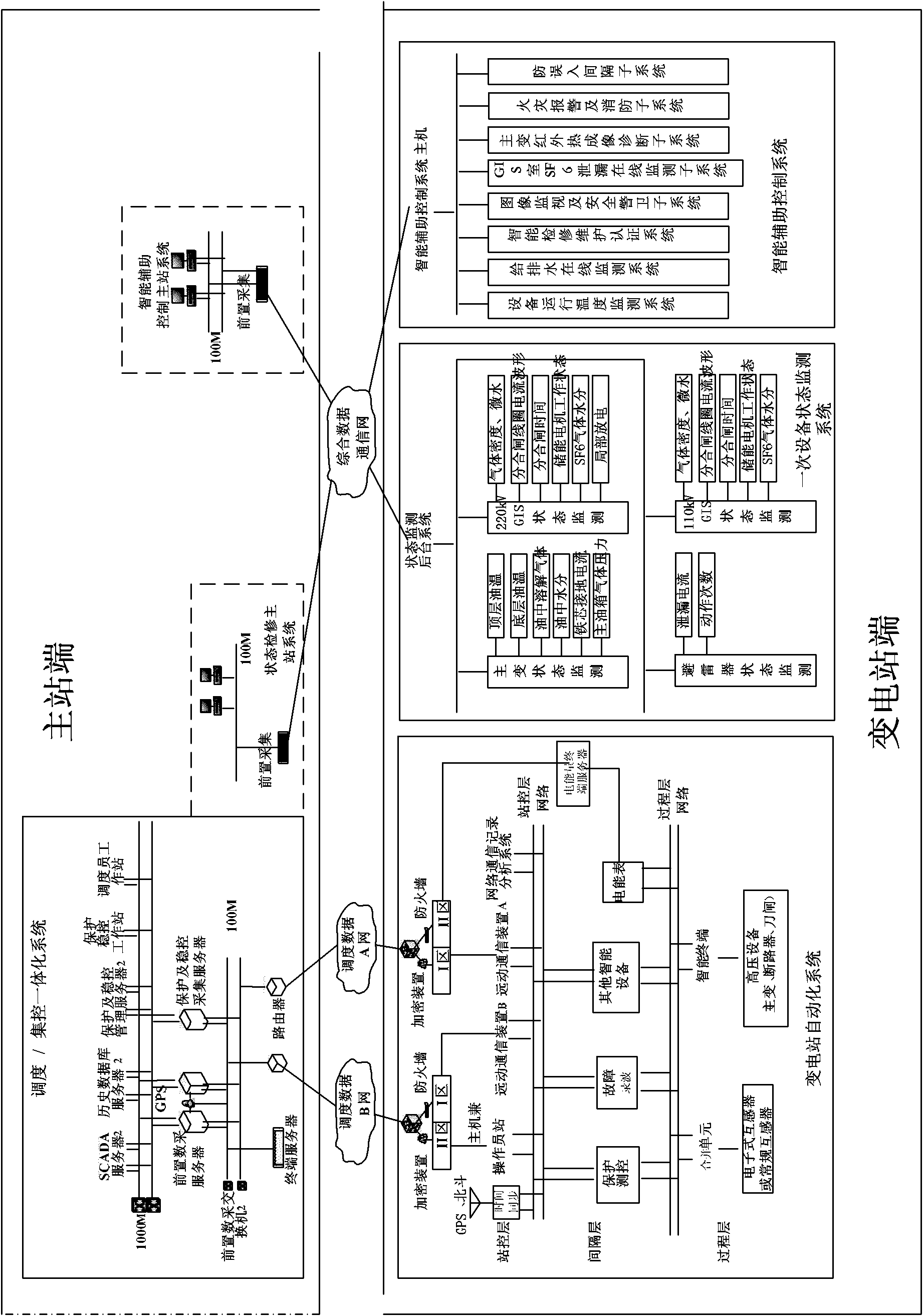

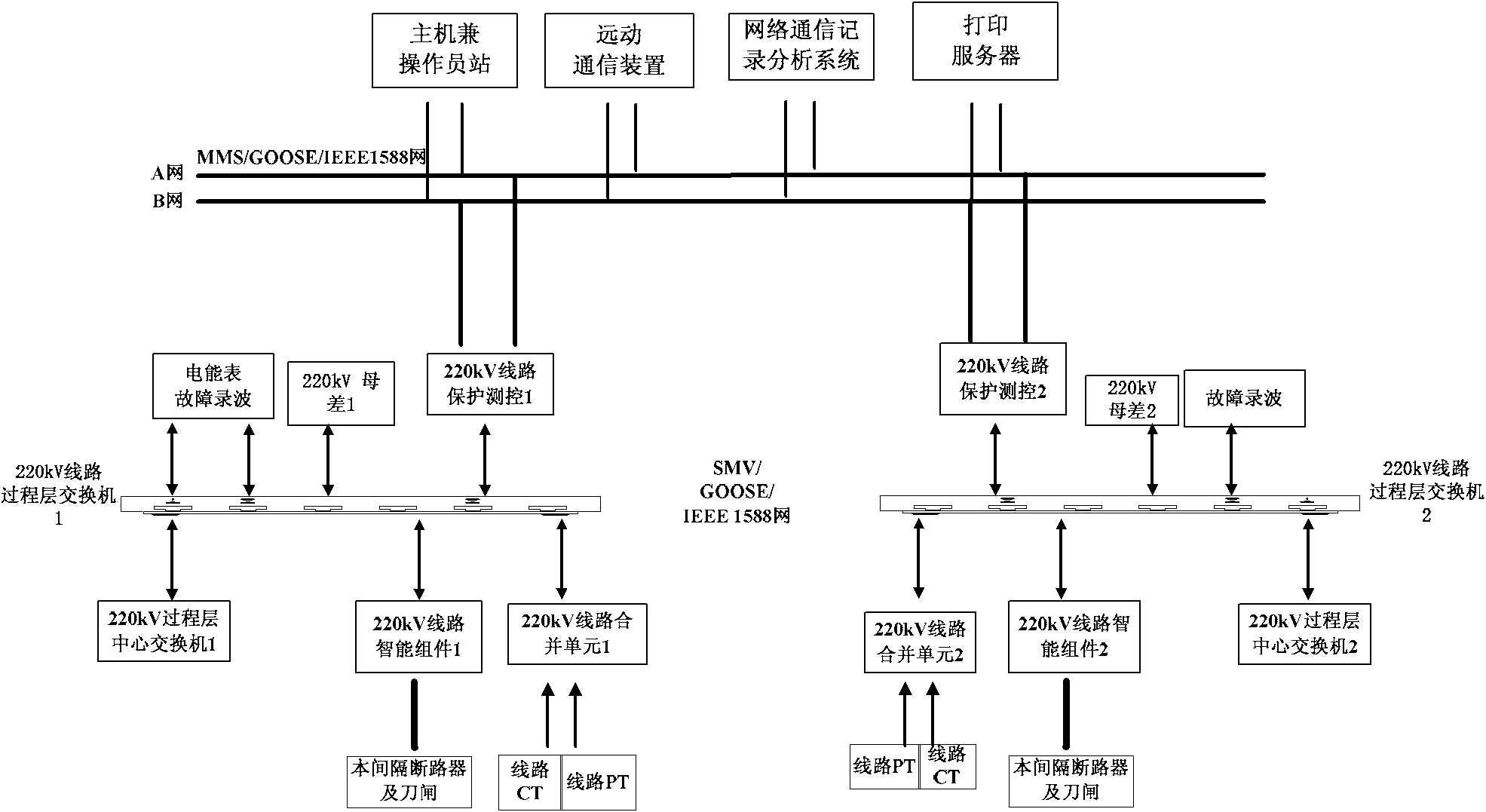

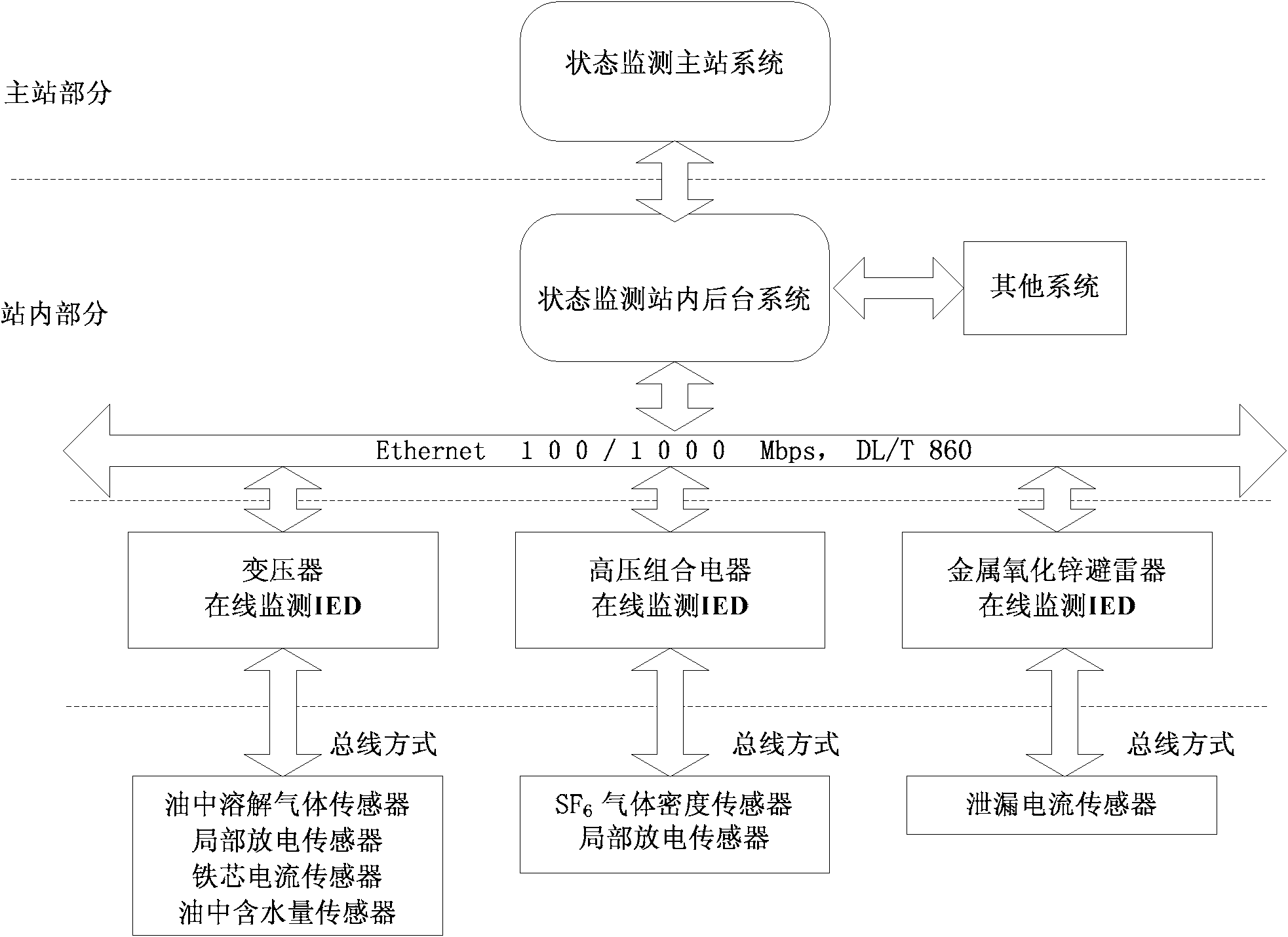

Intelligent substation based on sensor, communication network and expert system

InactiveCN102122844ARealize functionRealize online monitoringCircuit arrangementsInformation technology support systemThe InternetCapacitive voltage divider

The invention discloses an intelligent substation based on sensors, a communication network and an expert system. The intelligent substation comprises a substation automation system, a primary equipment condition monitoring system and an intelligent auxiliary control system. The intelligent substation is characterized in that the real-time data of equipment operation are acquired by additionally installing various sensors, the IEC61850 standard is utilized to realize information modeling of the sensor data, a communication network is utilized to build a physical channel for information transmission, and advanced application of the substation automation system and intelligent monitoring and linkage of the primary equipment condition monitoring and auxiliary systems are realized by a background expert system, thus realizing intelligent operation and patrol functions of the substation; the sensors include an all-fiber electronic current transformer, a capacitive voltage divider type electronic voltage transformer, a primary equipment condition monitoring sensor and an internet sensor with an auxiliary system things; and the advanced application of the substation automation system includes sequential control, equipment condition visualization, intelligent alarm, distributed condition estimation, substitution function and the like. Intelligent operation and patrol functions of the substation can be realized.

Owner:CEEC JIANGSU ELECTRIC POWER DESIGN INST +2

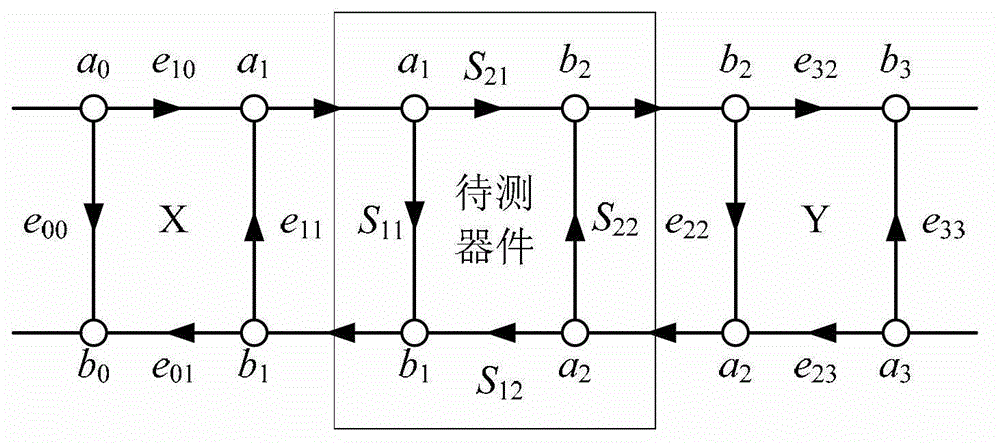

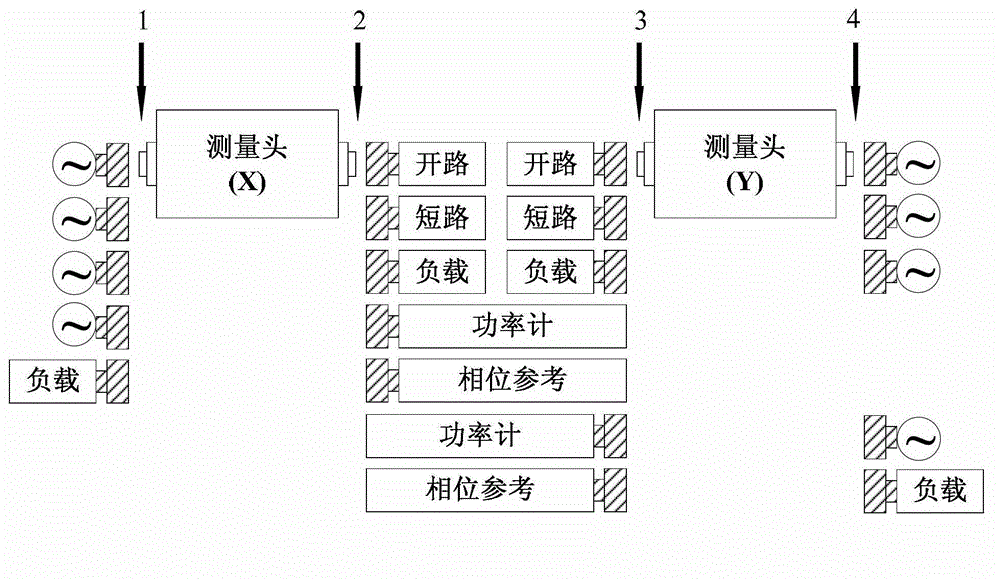

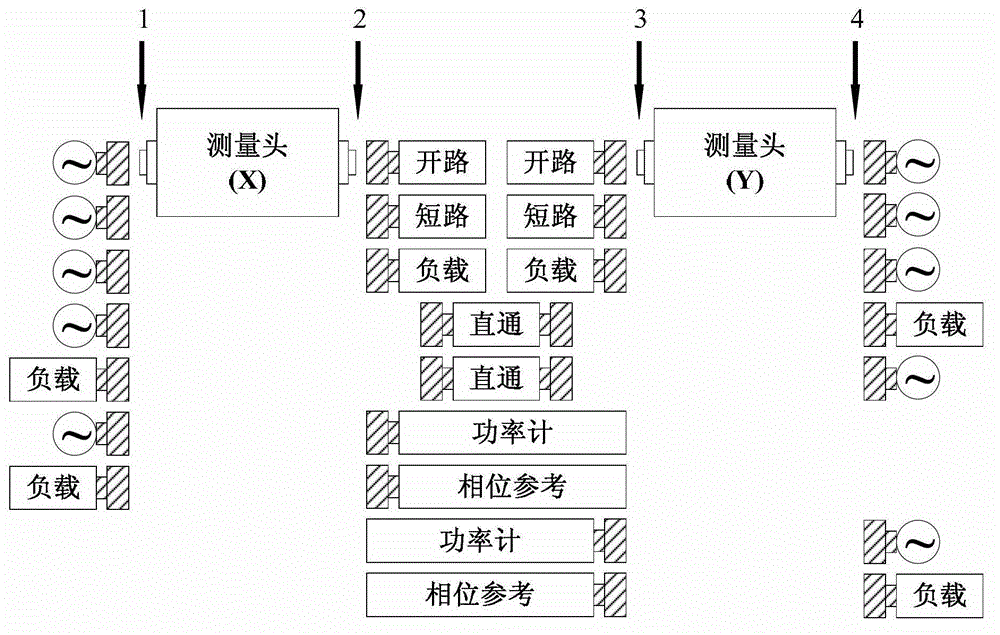

Twin port calibration method for nonlinearity vector network analyzer

The invention discloses a twin port calibration method for a nonlinearity vector network analyzer, relates to the technical field of microwave millimeter wave measurement and solves the problems that twin port calibration technology of existing nonlinearity vector network analyzers is single, and self-checking of a calibration result is difficult. Two ports of the nonlinearity vector network analyzer are utilized to perform open circuit, short circuit, loading, power, phase position and through calibrations respectively to obtain a nominal value and an actual measured value of a calibrated workpiece, eight error models are determined according to all obtained coefficients, and the calibration for the nonlinearity vector network analyzer is achieved. The twin port calibration method for the nonlinearity vector network analyzer is applicable to signal analysis and the most in-depth analysis for characteristics of non-linear devices.

Owner:HARBIN INST OF TECH

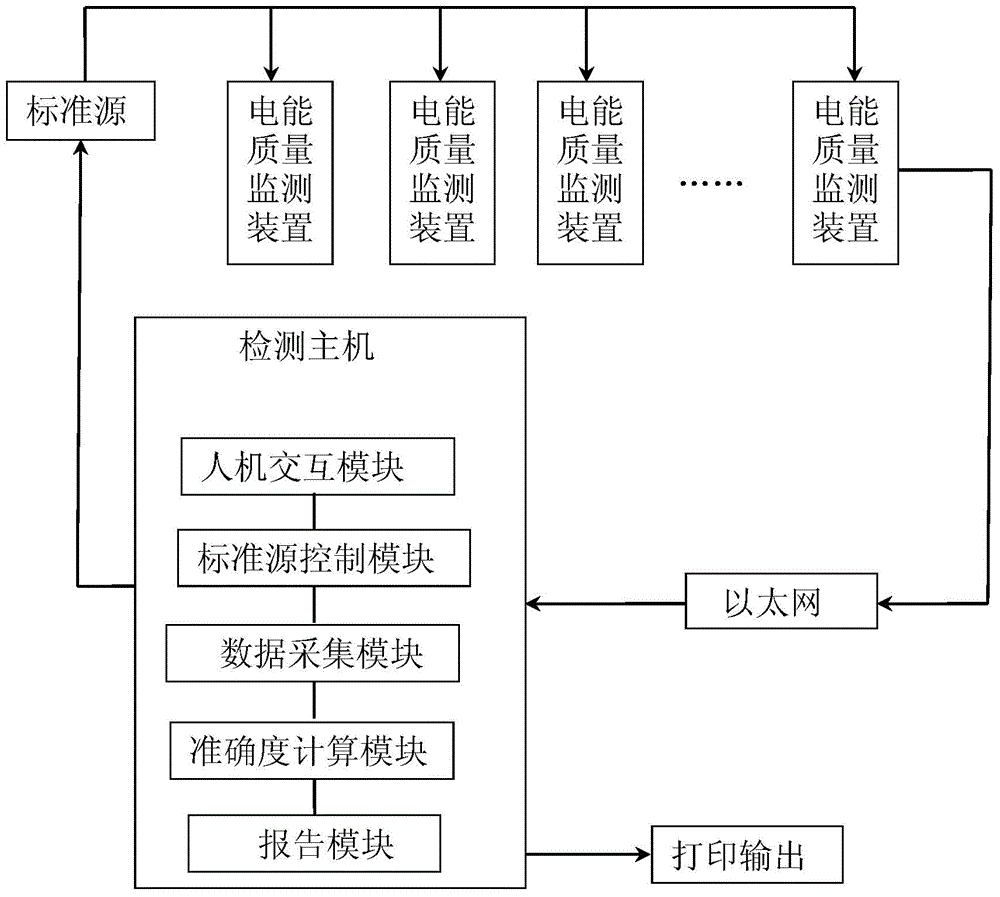

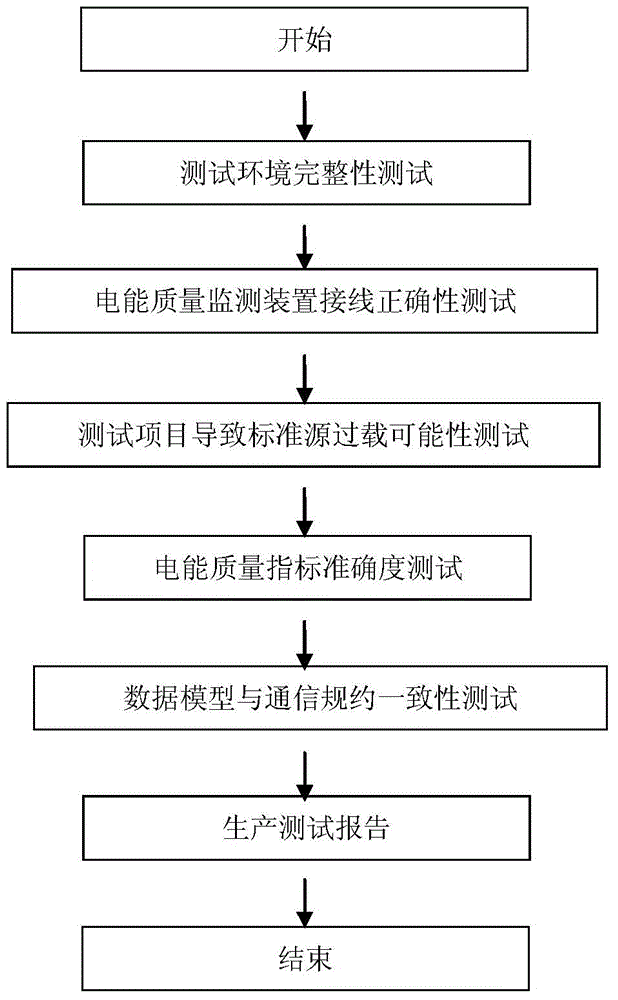

System for testing power quality monitoring device and testing method thereof

ActiveCN104569891AImprove intelligenceHigh degree of automationElectrical measurementsTest powerPower quality

The invention belongs to the technical field of full automatic detection of power equipment and particularly relates to a system for testing a power quality monitoring device and a testing method of the system. The system comprises a detecting host, a standard source and the power quality monitoring device. The detecting host is connected with the stand source through a GBIP bus in a communicating mode. The standard source is electrically connected with the power quality monitoring device through a test signal line. The power quality monitoring device and the detecting host form a closed loop communication control system through the Ethernet. According to the system and the testing method of the system, the accuracy of power quality indexes, a data model and communication protocols can be tested, the automatic system detection and fault recognition alarm functions of standard source overload judgment, power quality monitoring device wiring correctness, closed loop testing environment integrity and the like can be achieved, the intelligence and the automation degree of testing the power quality monitoring device are improved, and the work benefits of testing the power quality monitoring device are increased.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD

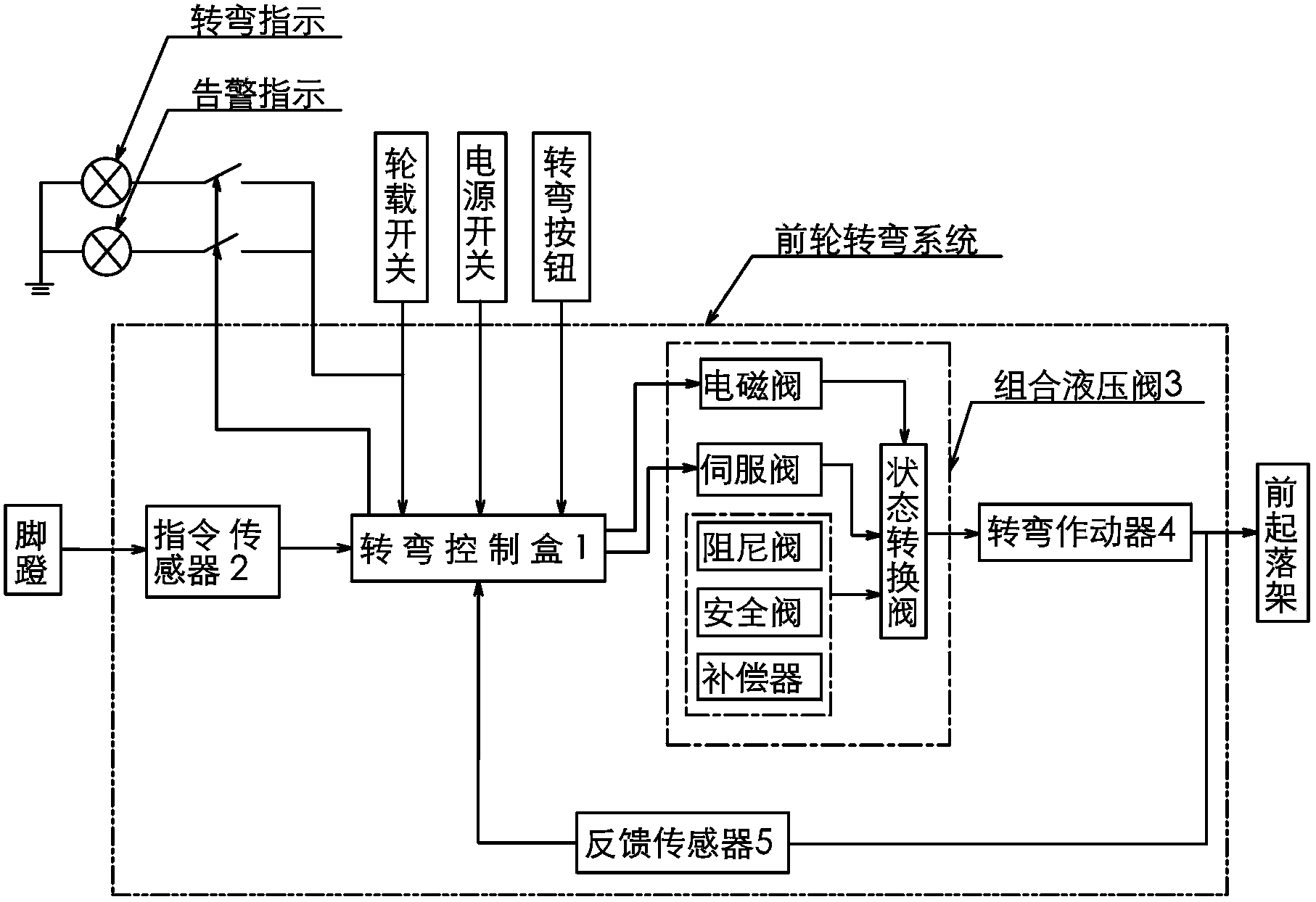

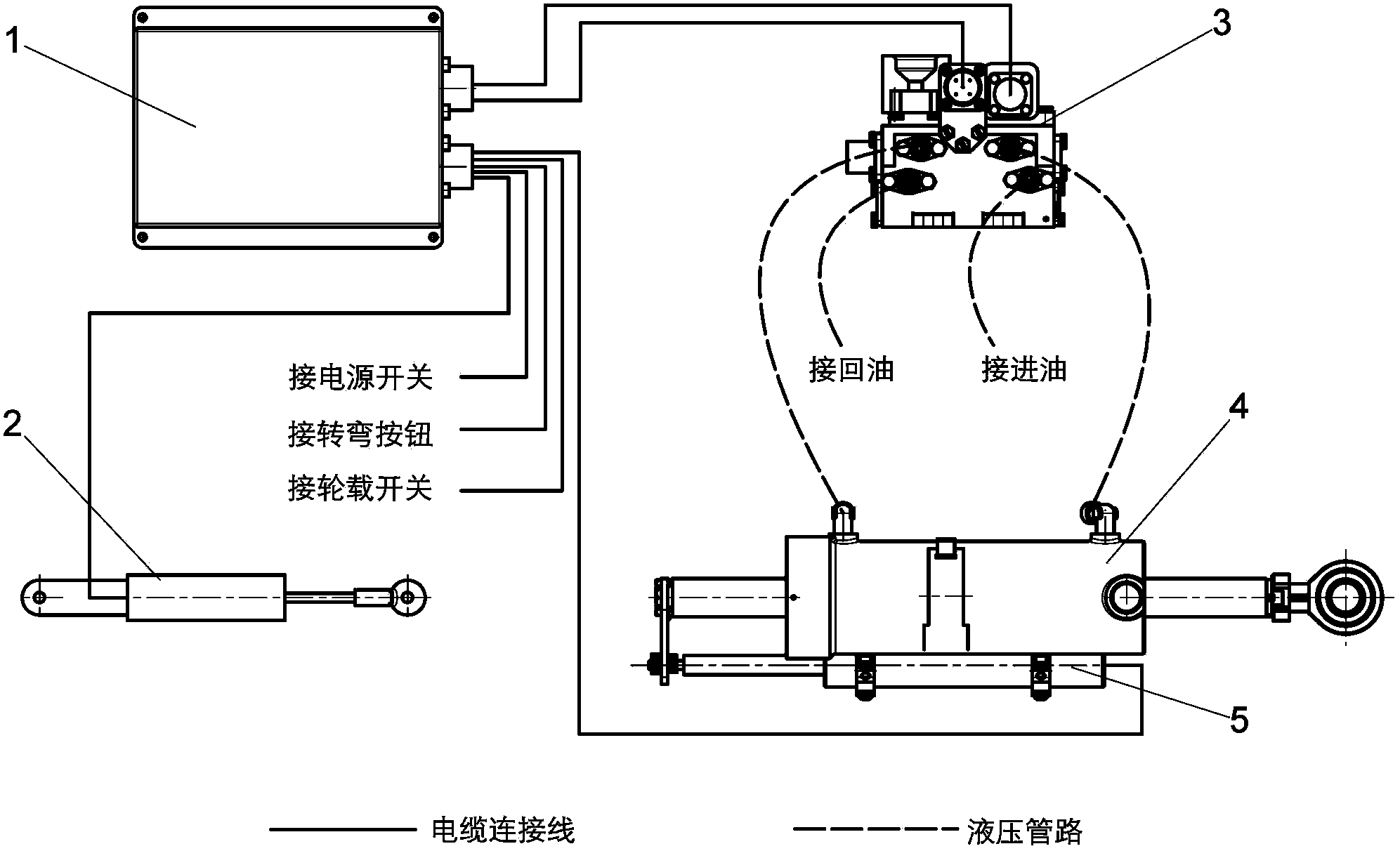

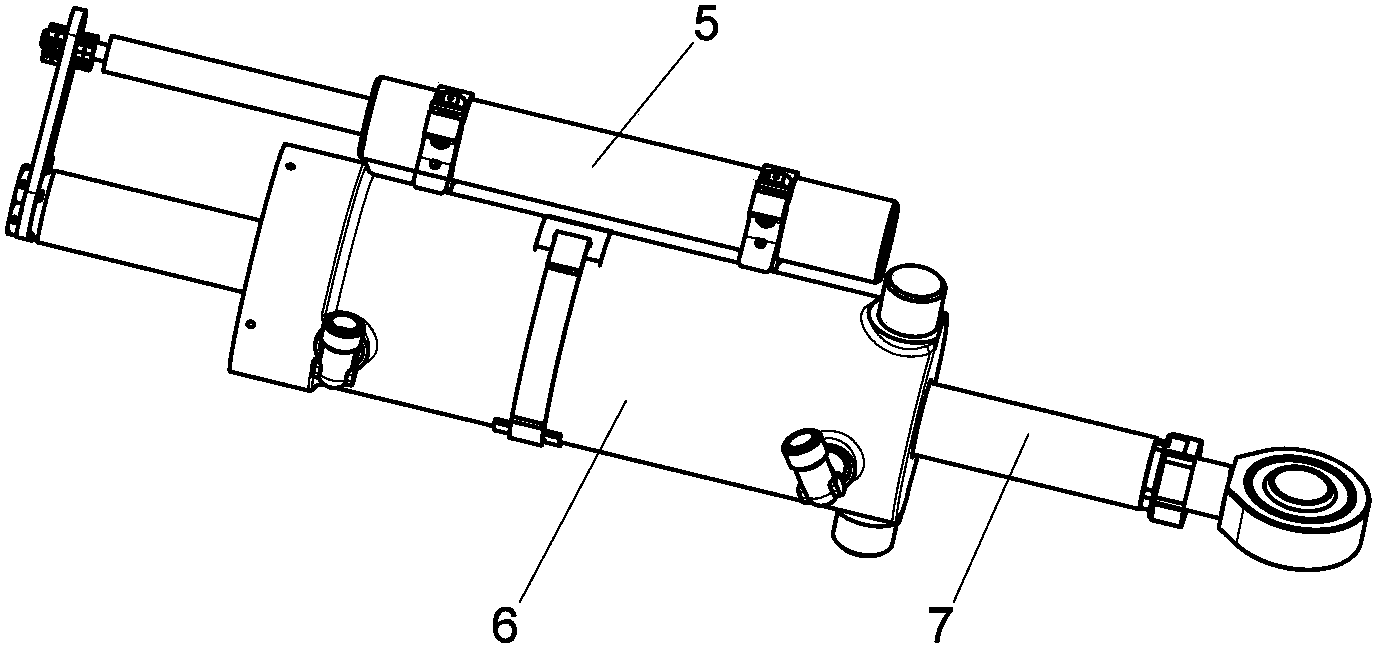

Nose-wheel steering system of aircraft

InactiveCN103523217AIncrease flexibilityImprove stabilityWheel arrangementsAviationAviation engineering

The invention belongs to the field of aircraft engineering, and provides a nose-wheel steering system of an aircraft. According to the nose-wheel steering system, a steering control box is connected with an instruction sensor, a combined hydraulic valve and a feedback sensor through cables; one end of the instruction sensor is fixedly arranged below a floor of a cockpit of the aircraft by using bolts, and the other end of the instruction sensor is hinged to a foot pedal through bolts; the combined hydraulic valve is fixedly arranged on a bulkhead plate of a nose landing gear through bolts; the feedback sensor is arranged on a steering actuator; one end of the feedback sensor is fixedly arranged on a steering actuator shell through a hoop, and the other end of the feedback sensor is connected with a piston rod of the steering actuator through a clamping piece; the steering actuator is arranged on the nose landing gear of the aircraft; a piston rod of the steering actuator is hinged to a rotary sleeve of the nose landing gear through a joint bearing and a bolt. The nose-wheel steering system of the aircraft is used for steering at a low-speed stage and swing prevention at a high-speed stage during sliding of the aircraft, and has good operation flexibility and anti-swing stability.

Owner:HARBIN

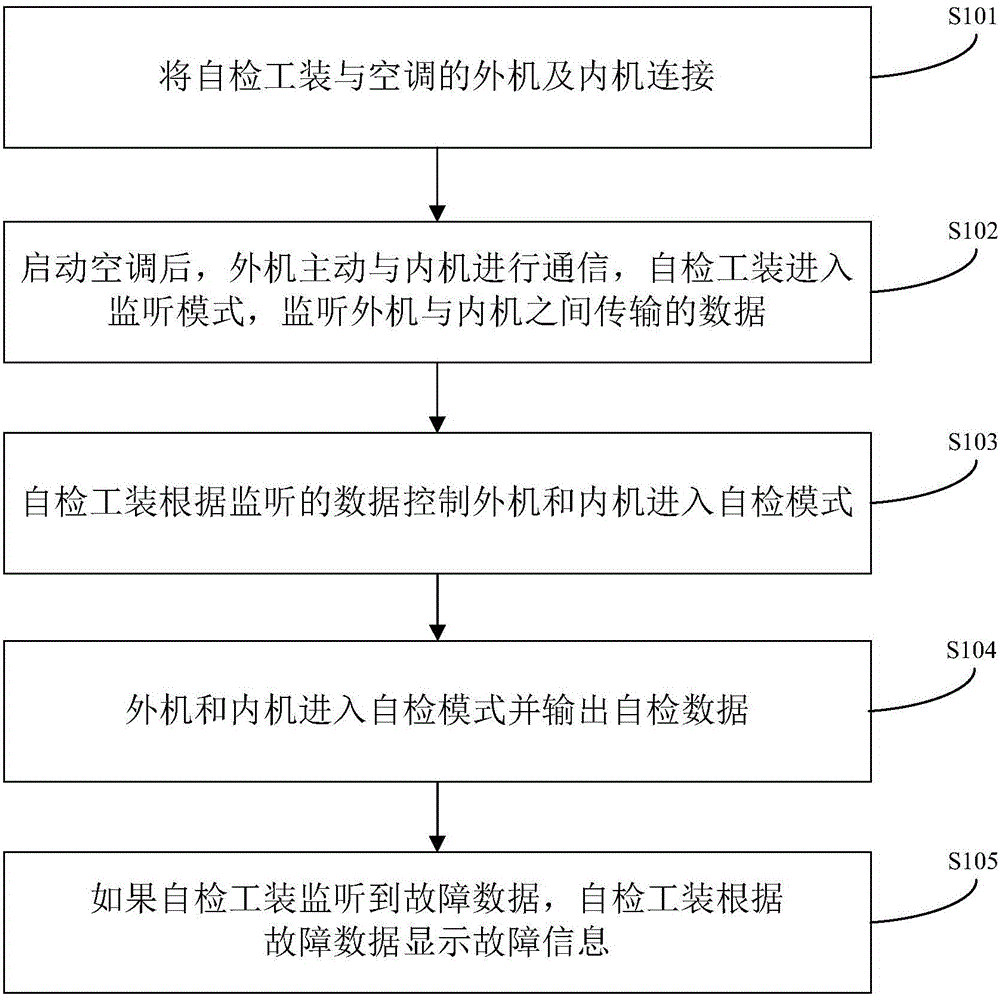

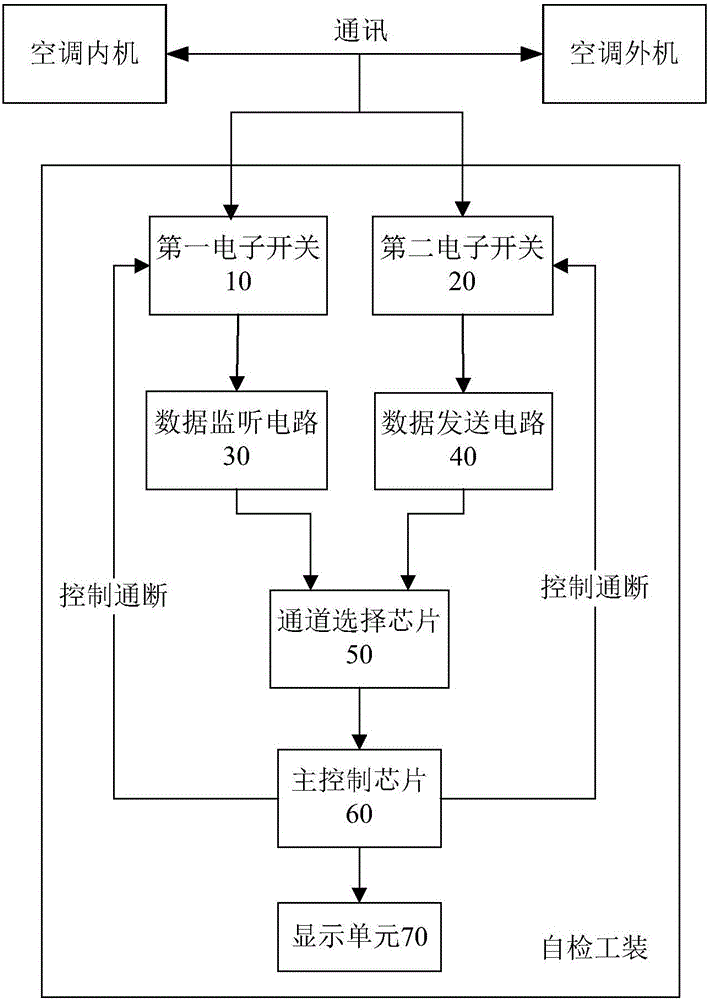

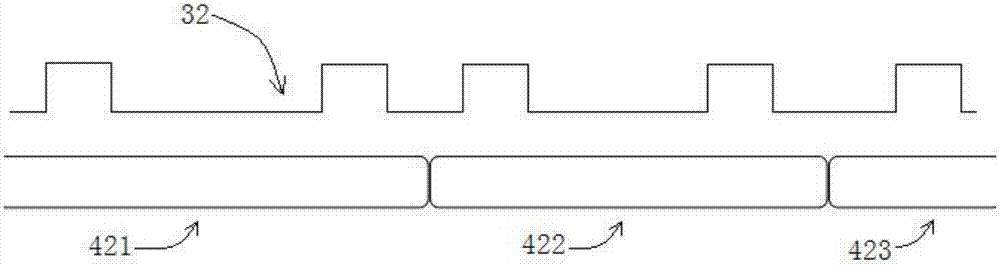

Air-conditioner fault self-examining method, tool and device

ActiveCN106016582AImplement self-testAccurately determineMechanical apparatusSpace heating and ventilation safety systemsData controlMonitoring data

The invention discloses an air-conditioner fault self-examining method, tool and device. The method comprises the steps that the self-examining tool and an external unit and an internal unit of an air-conditioner are connected; after the air-conditioner is started, the external unit is actively in communication with the internal unit, and the self-examining tool enters in a monitoring mode to monitor the data transmitted between the external unit and the internal unit; the self-examining tool controls the external unit and the internal unit to enter in a self-examining mode according to the monitored data; the external unit and the internal unit enter the self-examining mode and output self-examining data; and if the self-examining tool monitors fault data, the self-examining tool displays fault information according to the fault data. According to the air-conditioner fault self-examining method, tool and device, the self-examining tool is used for conducting troubleshooting guide on faults, achieves air-conditioner fault self-examining, and can quickly and accurately determine the position and causes of the faults through monitoring data; and during air-conditioner after-sale maintenance, the tool can be connected easily, and the overcoming speed and quality of after-sale faults are improved.

Owner:GREE ELECTRIC APPLIANCES INC

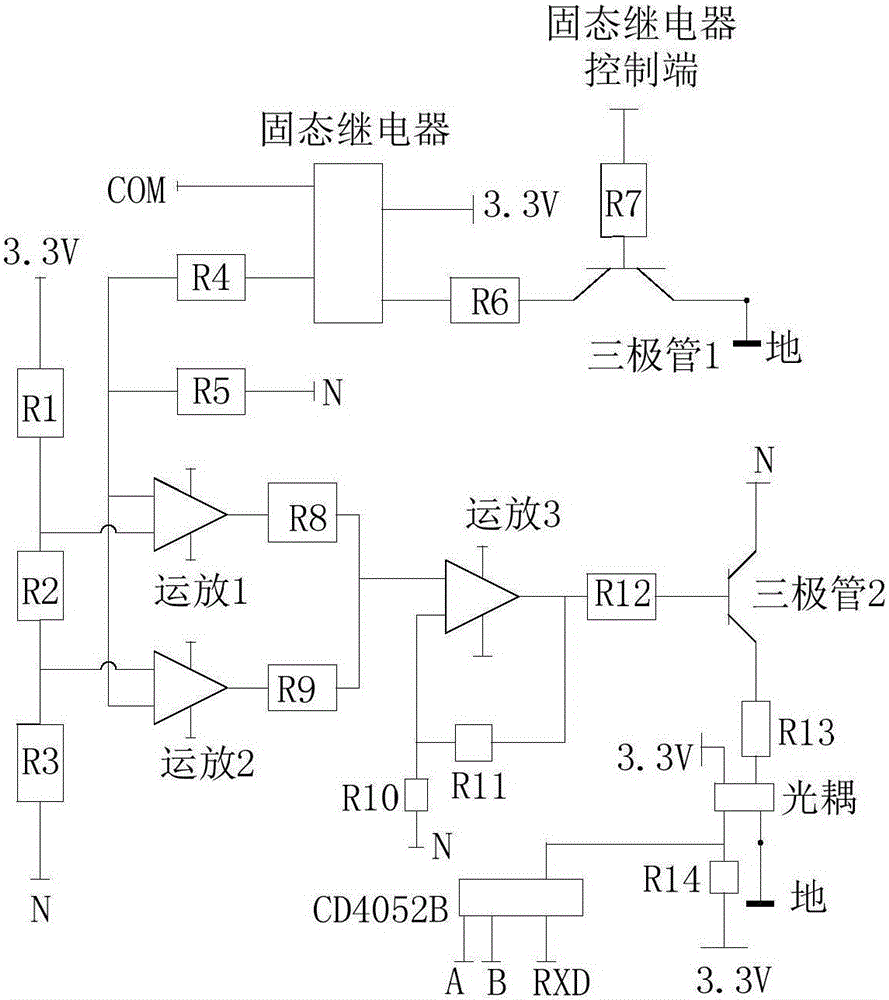

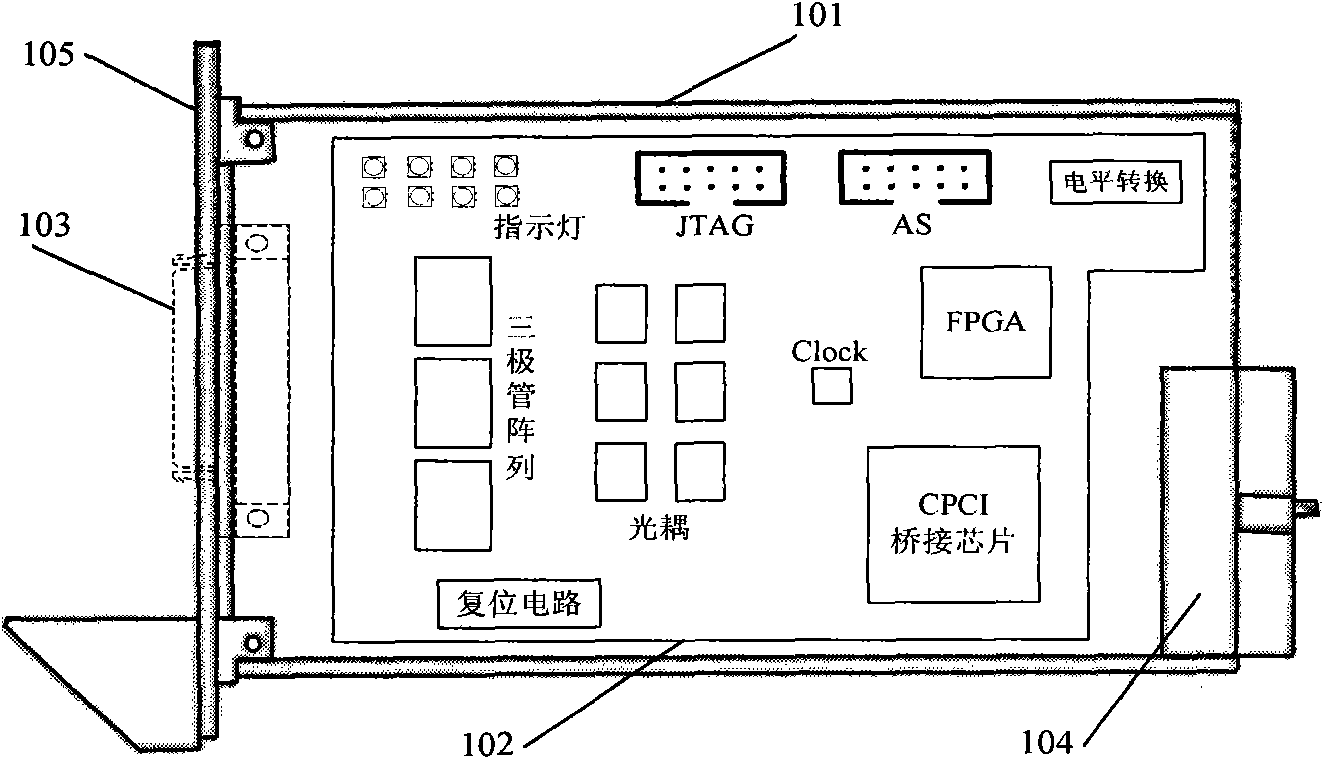

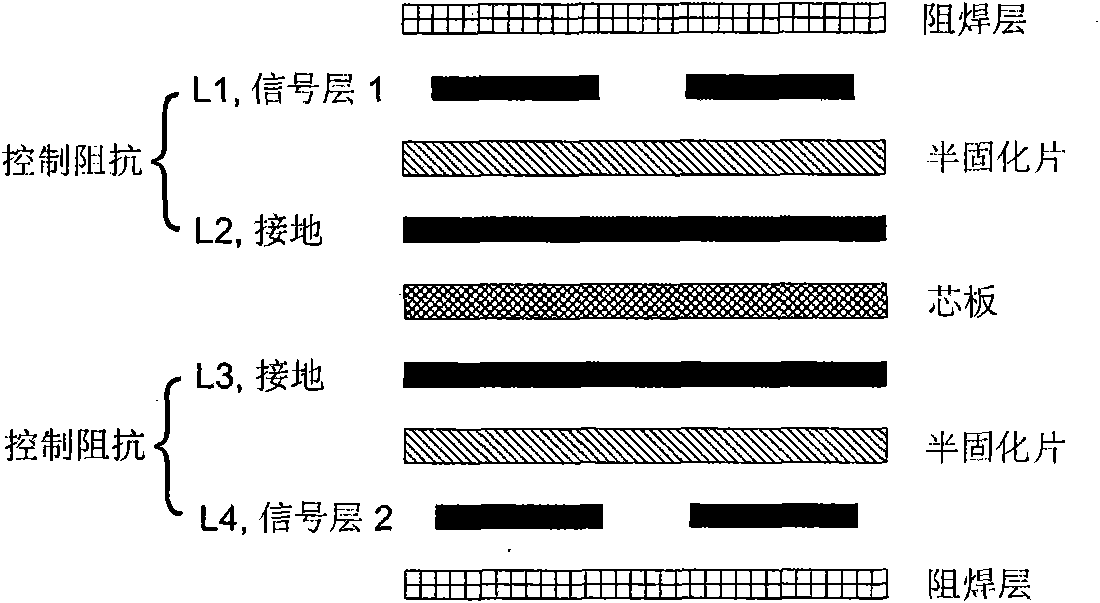

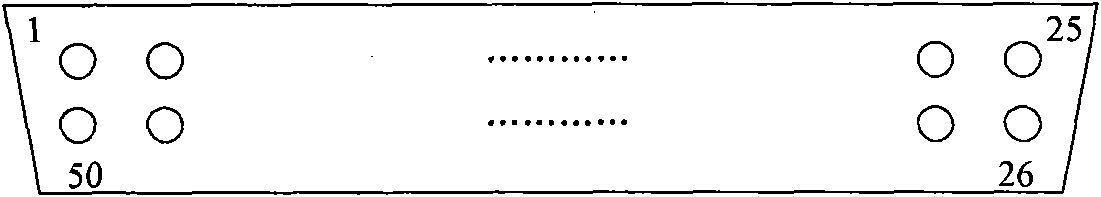

BMCH protocol data transceiver module based on CPCI bus

InactiveCN101963948AAchieve receptionRealize sendingElectric digital data processingTransceiverComputer module

The invention relates to a BMCH protocol data transceiver module based on a CPCI bus, comprising a hardware module and an FPGA program, wherein the hardware module comprises an impedance control circuit board, an electronic component, an SCSI50 signal gang socket, a standard CPCI bus connector and a standard 3U Eurocard board card front panel; the impedance control circuit board and the electronic component are the core functional carriers of the invention and are divided into five functional units, i.e. an FPGA unit, a CPCI bus unit, a BMCH protocol transmitting and conditioning unit, a BMCH protocol receiving and conditioning unit and an assistant unit; and the FPGA program comprises a BMCH protocol data receiver module, a BMCH protocol data transmitter module and a self-checking functional module and is programmed and developed by Verilog HDL. The invention has stable performance and high reliability and can carry out continuous transmission of the BMCH protocol data of large data volume for a long term; CPCI bus data transmission has a DMA function, practical bus transmission rate can reach 80MB / s, and no frames are lost by high-speed continuous transmission; and the BMCH bus signal has strong driving capability and long transmission distance. The invention has simple structure, low cost and convenient use.

Owner:BEIHANG UNIV

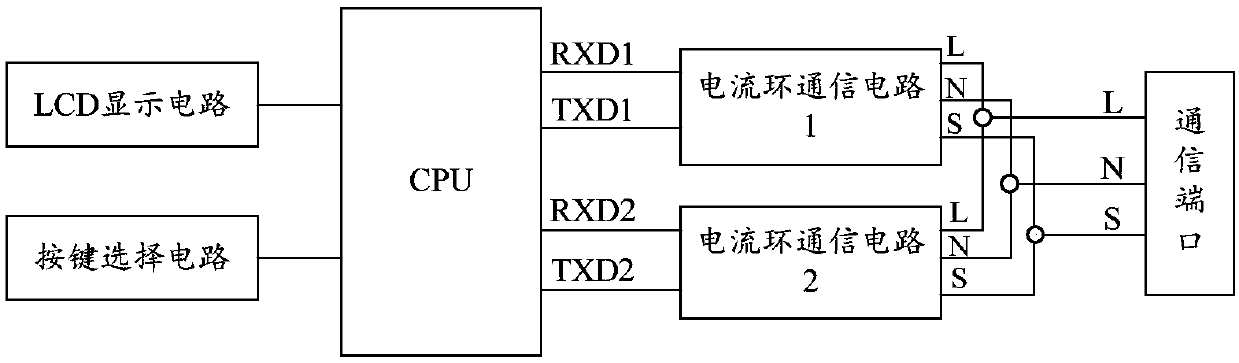

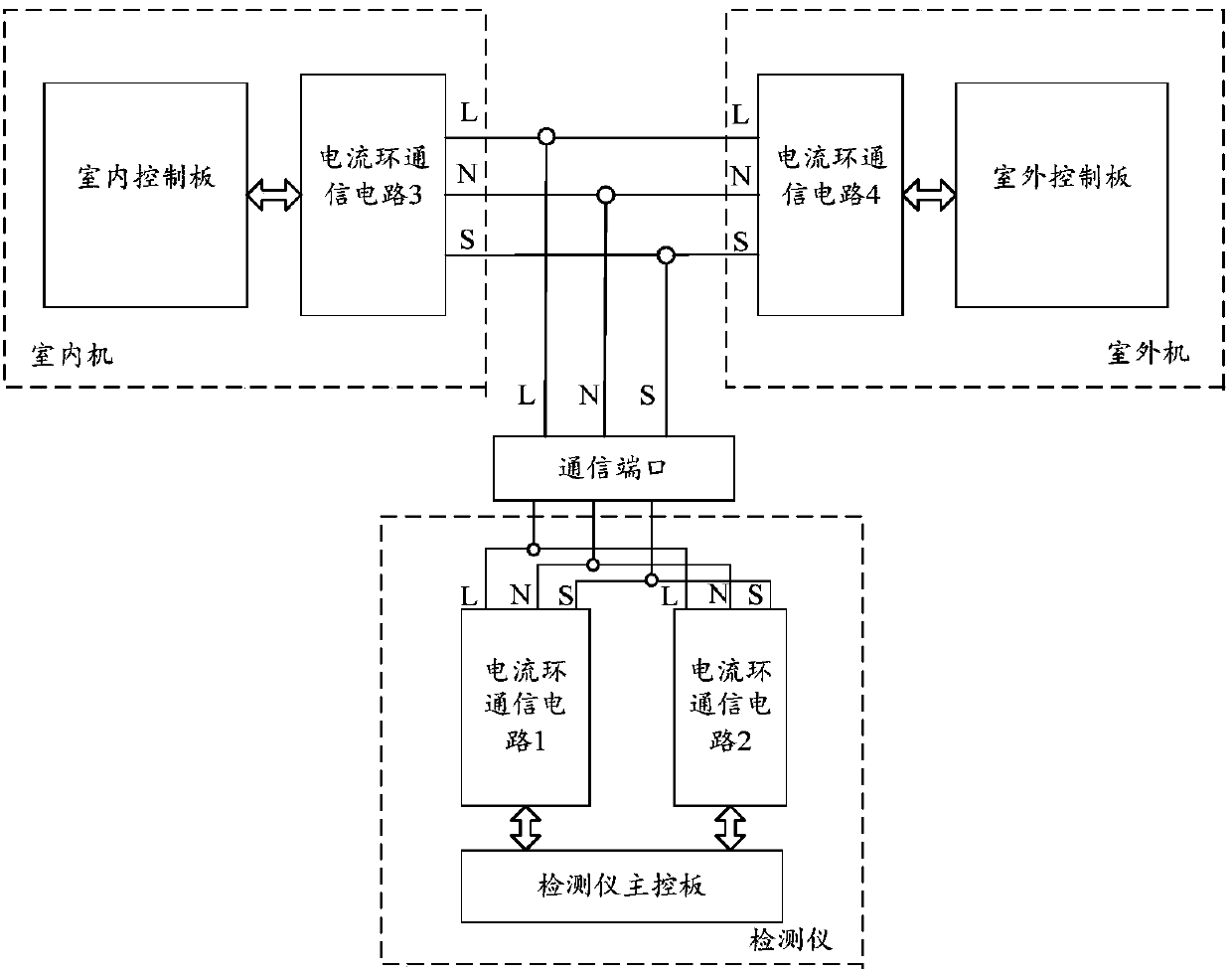

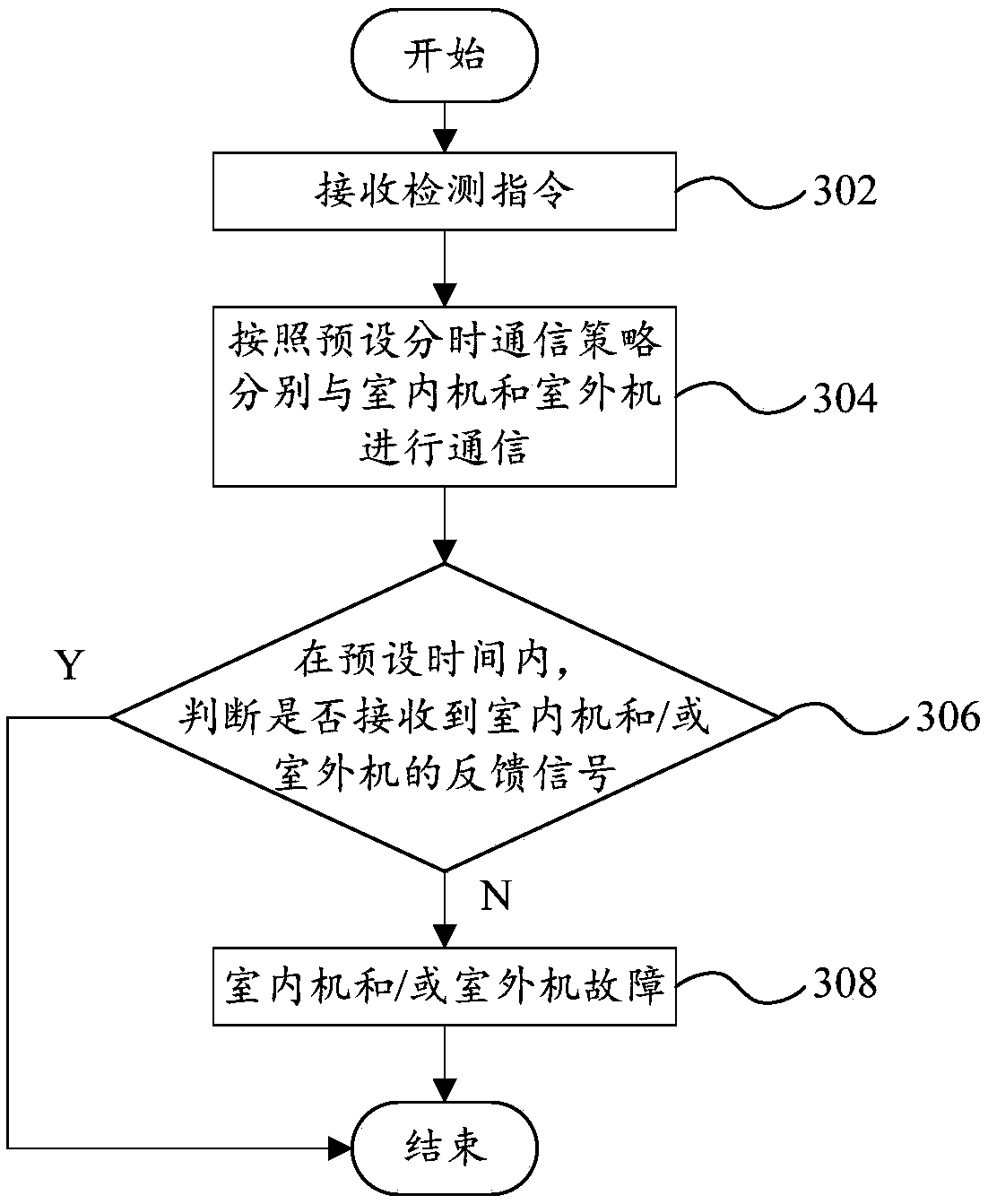

Detecting device and method

ActiveCN107741078AAvoid replacementImprove after-sales maintenance efficiencySpace heating and ventilation safety systemsLighting and heating apparatusElectricityPower flow

The invention provides a detecting device and method. The detecting device is used for air conditioners and each air conditioner comprises an indoor unit and an outdoor unit; the detecting device comprises a processor, communication ports and at least two sets of current-loop communication circuits connected with the processor, and the at least two sets of current-loop communication circuits are output to the communication ports and connected with current-loop communication circuits in the indoor units and the outdoor units through the communication ports. The detecting device has the functionof power-on automatic detecting communication failure, can detect the communication failure of the indoor units and the communication failure of the outdoor units and is simple and easy to use, the research and development debugging efficiency and the air conditioner after-sale maintenance efficiency can be greatly improved, and the after-sale cost is reduced.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD

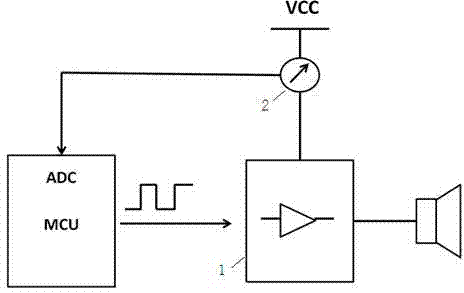

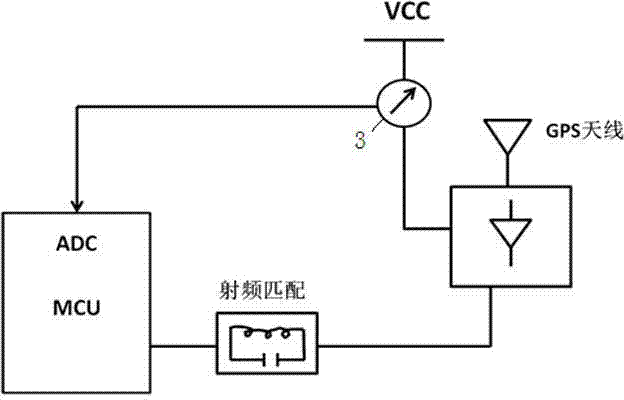

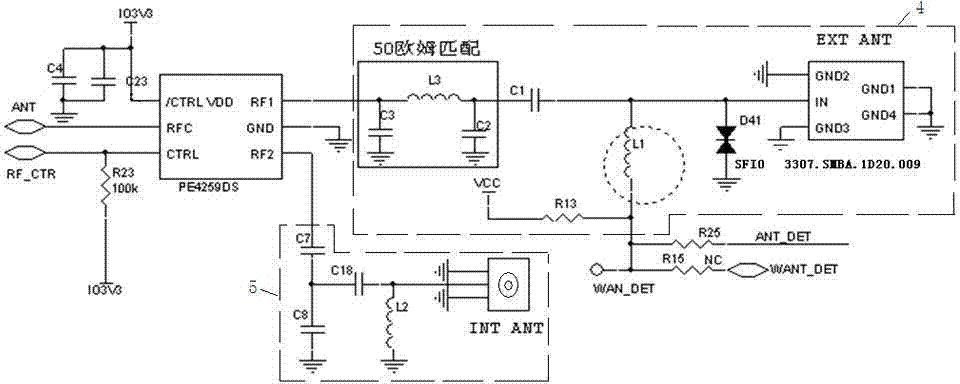

Self checking implementation method of vehicle-mounted remote monitoring terminal

ActiveCN102929268AImplement self-test and recoveryGuaranteed uptimeElectric testing/monitoringAirbag deploymentSelf checking

The invention relates to a self checking implementation method of a vehicle-mounted remote monitoring terminal. The method is characterized by comprising GPS (Global Position System) self checking, speaker self checking, power supply self checking, airbag signal self checking, FSK (Frequency Shift Keying) self checking, CAN (Controller Area Network) self checking and internal memory self checking of the terminal, wherein the GPS self checking comprises reading the working voltage and current of a GPS antenna through an ADC (Analog To Digital Converter) of an MCU (Micro Controller Unit) of the terminal, and determining whether the antenna is in a certain state of normal, broke off and short circuit states according to the voltage and the current; the speaker self checking comprises sending a signal from the MCU of the terminal, the ADC of the MCU reading the working current of a power amplifier of the speaker, and determining the state of the speaker according the current; and the internal memory self checking comprises reading and writing several specific regions in the memory every time when the terminal is initialized, and if an error arises, the memory reporting an error interrupt, and the MCU determining whether a bad block exists in the memory depending on the interrupt. By adopting the self checking implementation method provided by the invention, self checking of the vehicle-mounted remote monitoring terminal can be realized, the normal operation of the terminal is ensured, and the stability of the system is improved.

Owner:慧翰微电子股份有限公司

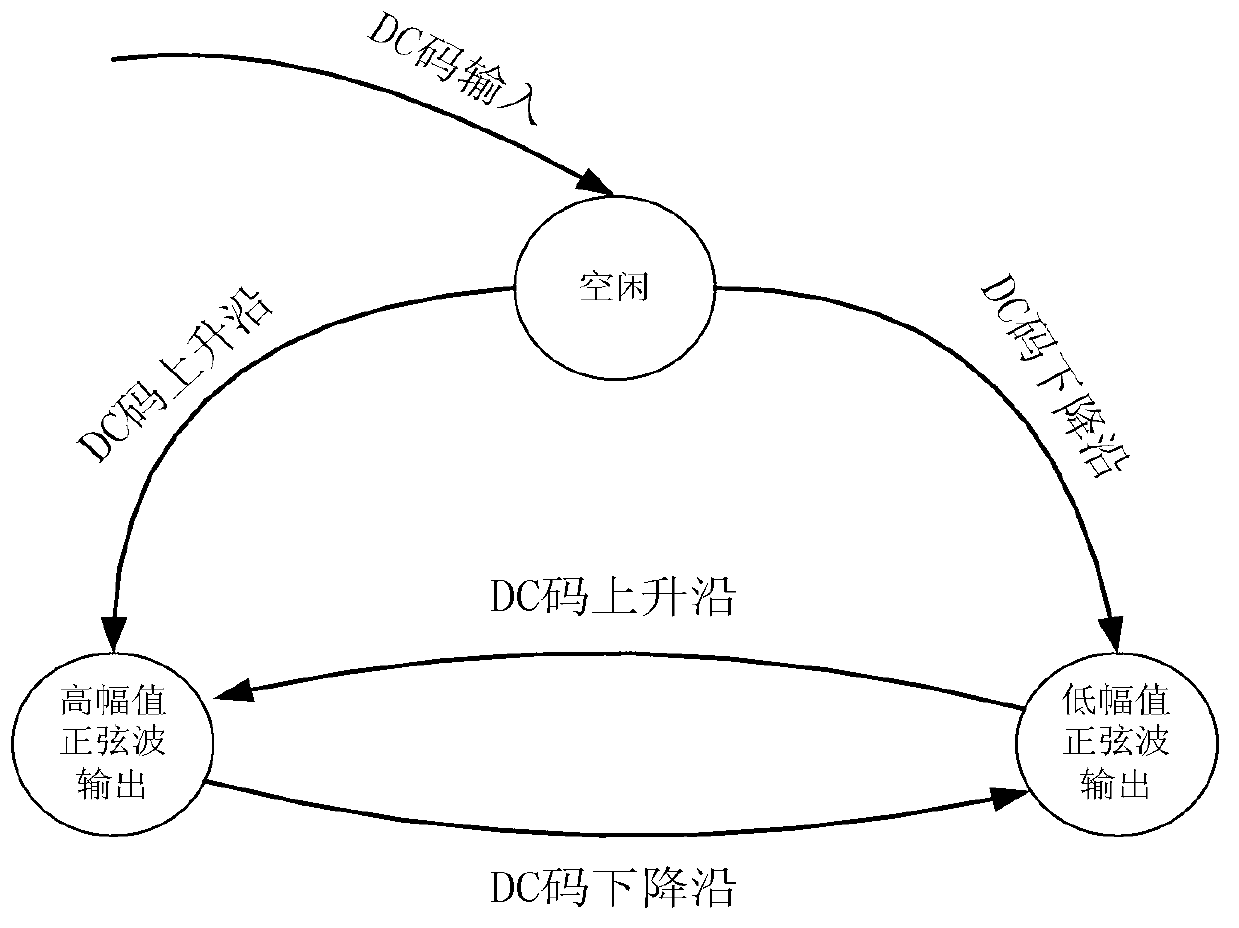

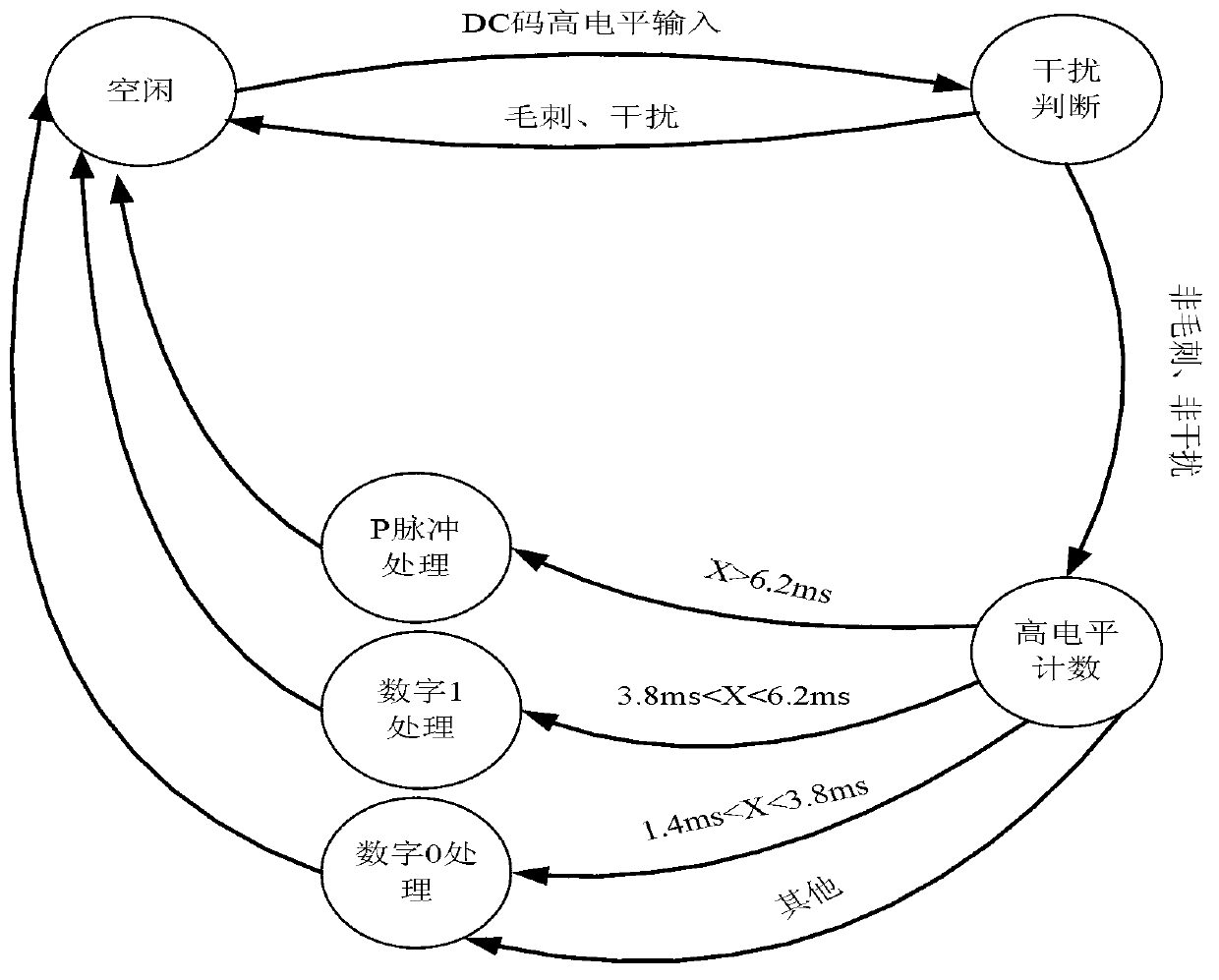

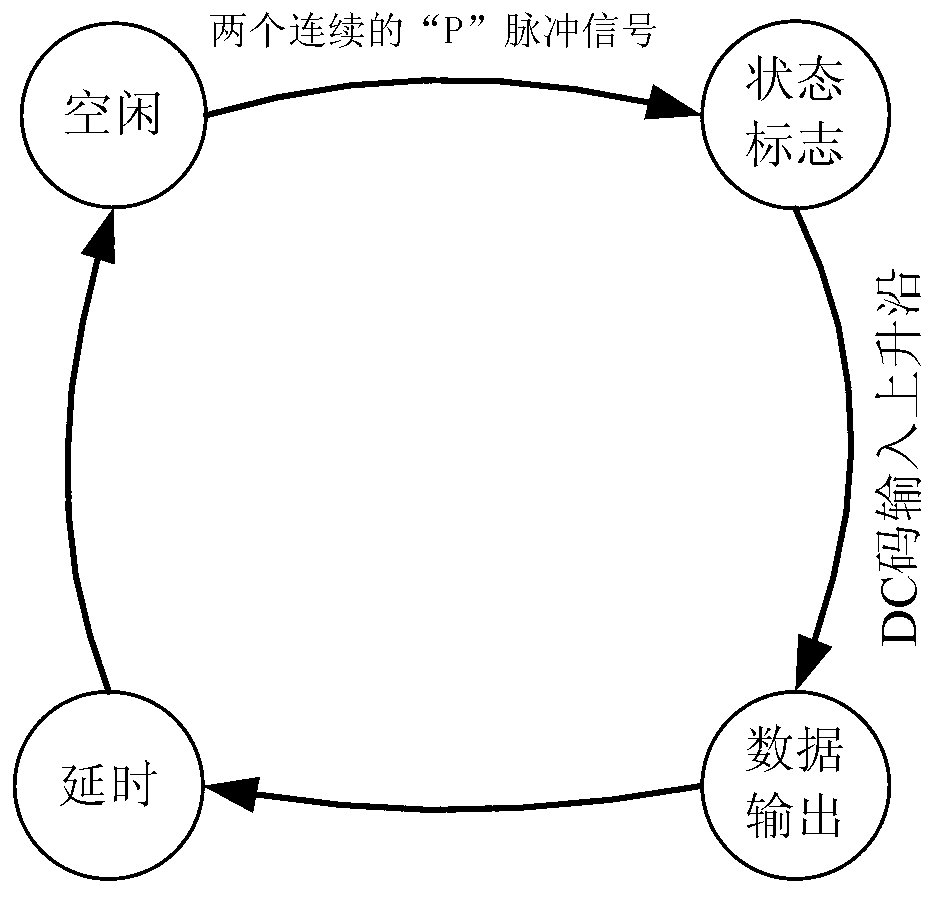

IRIG-B (Inter Range Instrumentation Group) encoding and decoding system and method based on FPGA (Field Programmable Gate Array)

ActiveCN103346804ATo achieve encoded outputImplement input decodingError correction/detection using multiple parity bitsTime informationComputer module

The invention discloses an IRIG-B (Inter Range Instrumentation Group) encoding and decoding system and method based on an FPGA (Field Programmable Gate Array), belonging to the technical field of communication. The system and the method solve the problems that a conventional IRIG-B code processing system needs an external signal source of IRIG-B codes to accomplish self-inspection on a decoding system, and that the accuracy of a decoding function cannot be verified. The IRIG-B encoding and decoding system based on the FPGA comprises a GPS (Global Positioning System) / beidou double-system module, the FPGA, a singlechip, a DAC (Digital-to-Analog Converter) chip, a comparer chip, a host computer and a PCI (Peripheral Component Interconnect) adapting card, wherein the GPS / beidou double-system module, the FPGA, the singlechip, the DAC chip and the comparer are integrated on a board card, and the board card is connected with the host computer through the PCI adapting card. The method comprises the following steps that: the singlechip decodes received time information and subsequently inputs the received time information into a DC (Direct Current) encoding control logic module and an AC (Alternative Current) encoding control logic module of the FPGA so as to encode a DC code and an AC code; after the encoding is accomplished, the DC code and the AC code are respectively input into the FPGA through an external loopback and are subsequently decoded; the decoding result is uploaded to the host computer. The technical scheme provided by the invention is applicable to IRIG-B encoding and decoding systems.

Owner:HARBIN INST OF TECH

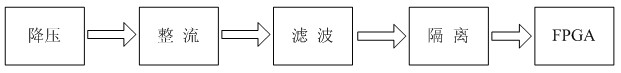

Switching value control method for high-voltage frequency converter and control plug-in thereof

ActiveCN102122142AImprove anti-interference abilityIsolation of high voltage interferenceProgramme control in sequence/logic controllersVIT signalsSelf checking

The invention relates to a switching value control method for a high-voltage frequency converter and a controller thereof; a switching value input measurement circuit of the high-voltage frequency converter is arranged at the input end of the high-voltage frequency converter to collect an input switch value signal of the high-voltage frequency converter, and the input switch value signal of the high-voltage frequency converter is accessed to a logical controller through signal amplitude decreasing, rectifying, filtering and isolating treatment; and the logic controller emits a control instruction after operation processing to control switch-on and switch-off of an external signal after being processed through the switching value input measurement circuit about potential conversion, isolating, filtering and relay isolation. In the switching value control method for the high-voltage frequency converter, an output switching value self-checking part is arranged; the output switching valueself-checking part performs amplitude decreasing and isolation to the output control switching value signal to feed in a logic processor to output the switching value state to feedback the output state to the logic processor through a feedback circuit, so as to realize switching value self-checking; moreover, the logic processor is communicated with a master controller of the high-voltage frequency converter through an optical fiber.

Owner:ZHUZHOU NAT ENG RES CENT OF CONVERTERS

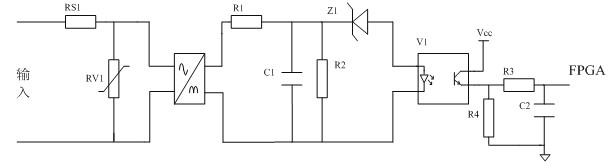

Solenoid valve control circuit and solenoid valve switch-in self-checking method thereof

ActiveCN102777665AImplement self-testAdd voltage sampling circuitOperating means/releasing devices for valvesElectrical resistance and conductanceCurrent limiting

The invention discloses a solenoid valve control circuit and a solenoid valve switch-in self-checking method thereof. The solenoid valve control circuit comprises a solenoid valve circuit and a voltage dividing and sampling circuit. The solenoid valve circuit comprises a microprocessor circuit, a solenoid valve DC, an audion Q1, a polar capacitor C1, a current limiting resistor R1 and a current limiting resistor R4, and the voltage dividing and sampling circuit comprises a divider resistor R2 and a sampling resistor R3. The analog-to-digital conversion input end of the microprocessor circuit is connected with one end of the sampling resistor R3. The solenoid valve switch-in self-checking method includes the following steps that a microprocessor U1 controls the audion Q1 to be disconnected, and the sampling voltage V1 of the sampling resistor R3 is collected; then the audion Q1 is controlled to be conducted and delayed, wherein the delay time is T1, and the sampling voltage V2 of the sampling resistor R3 is collected; and after that, the sampling voltage V1 is compared with the sampling voltage V2; if V1 is equal to V2, the solenoid valve is not switched in, otherwise, the solenoid valve is switched in. The solenoid valve control circuit has the advantages of scientific design and high safety, and the method occupies fewer resources of the system, is easy to realize, low in cost, simple and practical.

Owner:HENAN HANWEI ELECTRONICS

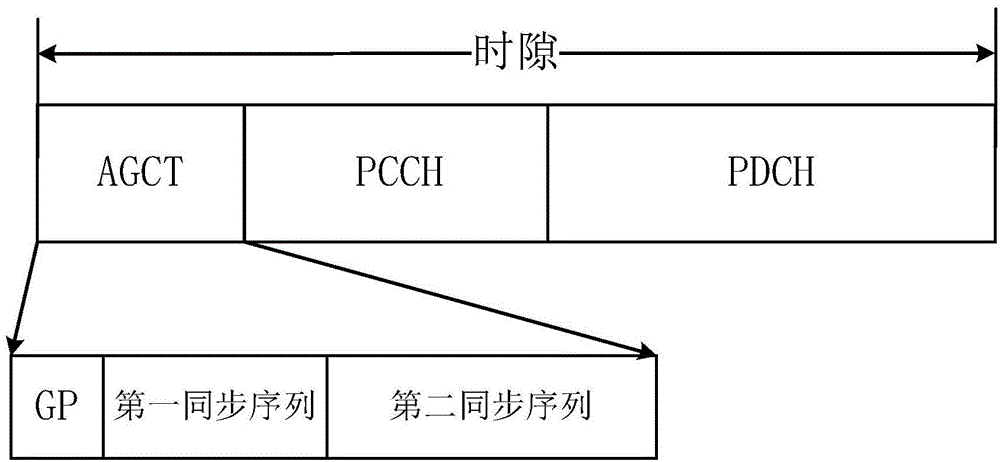

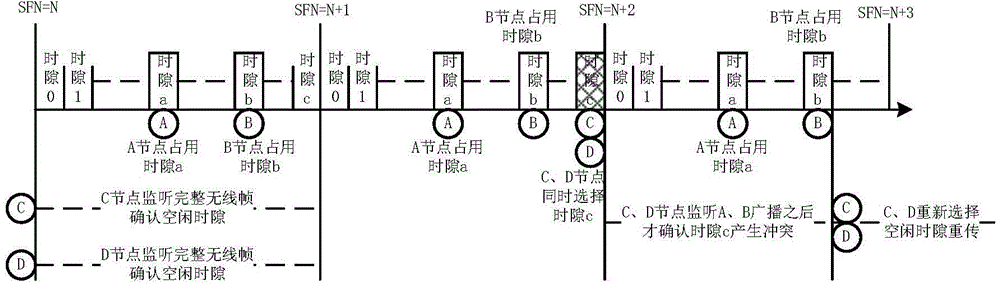

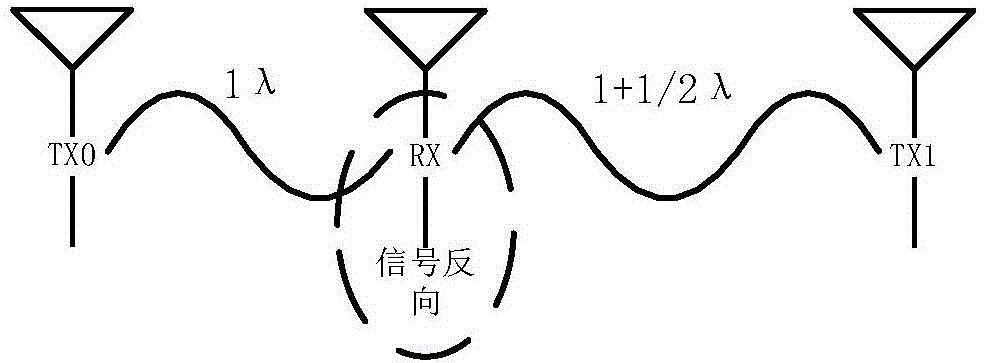

Adhoc network data transmission method and device

ActiveCN105451362AImplement self-testImprove performanceWireless communicationTime delaysNetwork data

The invention discloses an adhoc network data transmission method and an adhoc network data transmission device. The adhoc network data transmission method comprises the steps that: a node sends a first synchronous sequence in a full-duplex manner at a predetermined time slot, and a receiving channel of the node is detected at the same time, wherein the first synchronous sequence is used for completing gain adjustment and coarse frequency offset estimation; and the node determines the conflict situation of the predetermined time slot by adopting a method based on radio frequency interference cancellation. The adhoc network data transmission method and the adhoc network data transmission device detect the receiving channel of the node when the node sends the first synchronous sequence, determine whether conflict occurs at the time slot used by the node according to the detection result, achieve self-detection of conflict situation at the time slot used by the node, increase conflict detection accuracy, greatly reduce retransmission time delay of node information, and increase network performance.

Owner:DATANG MOBILE COMM EQUIP CO LTD

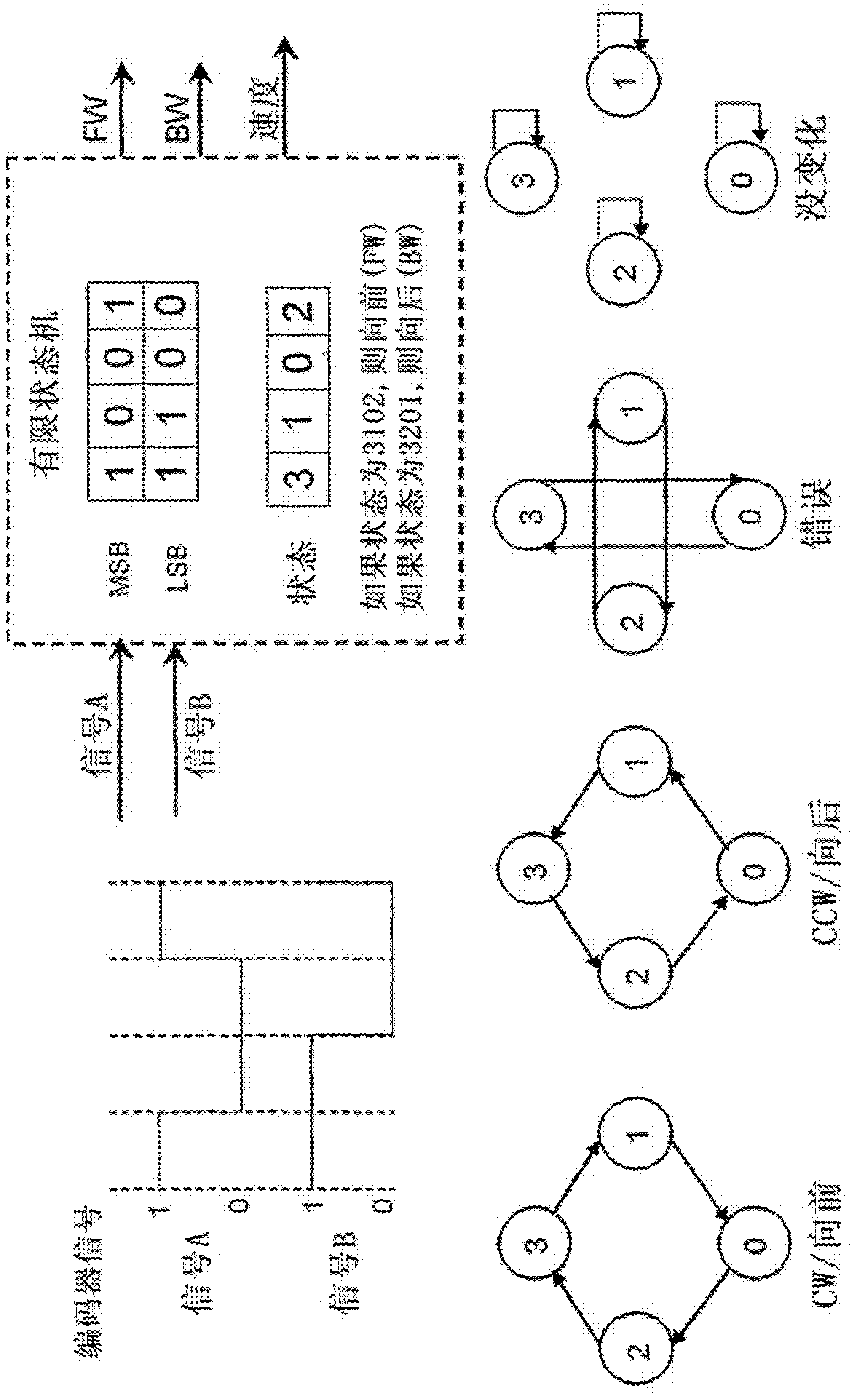

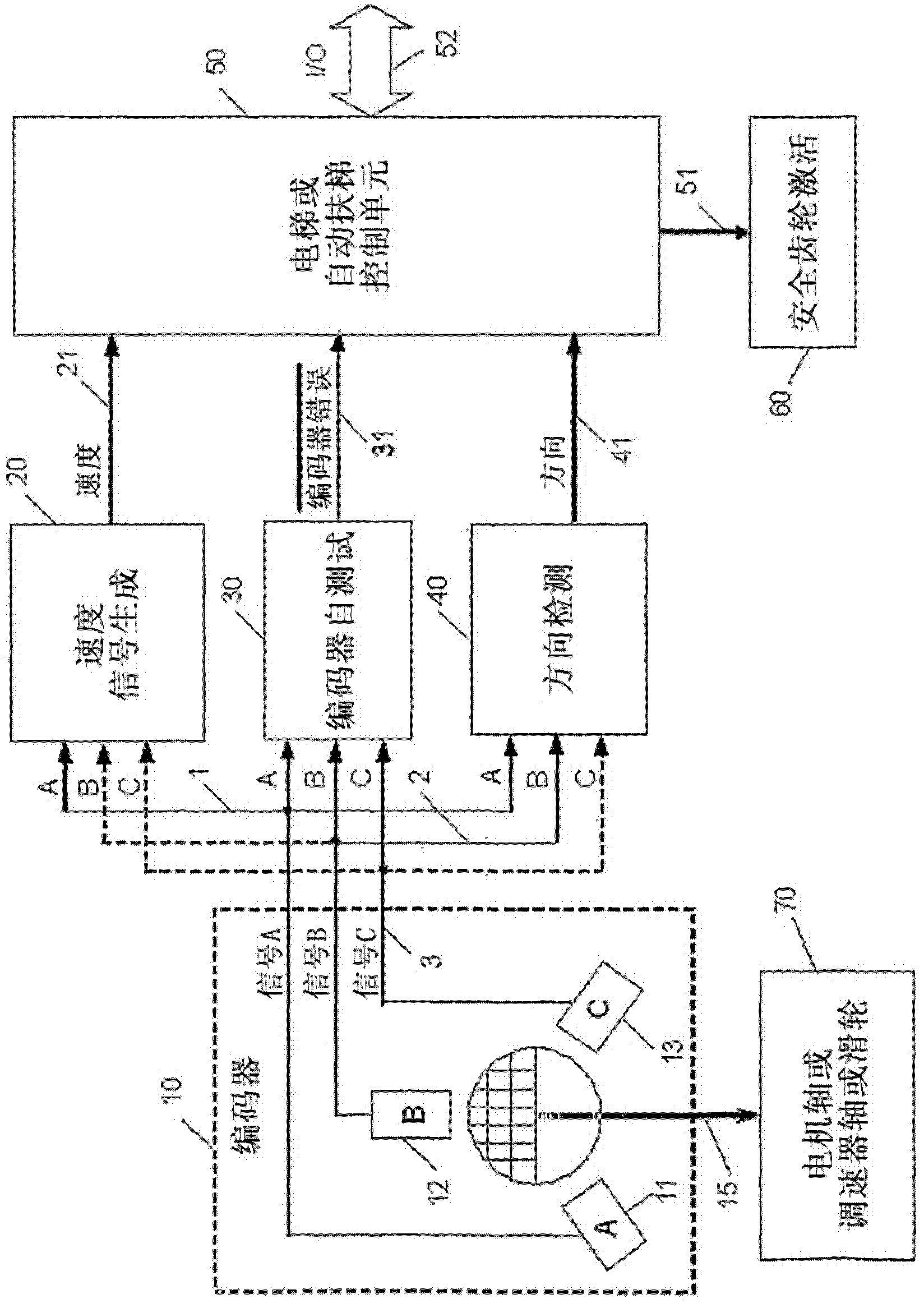

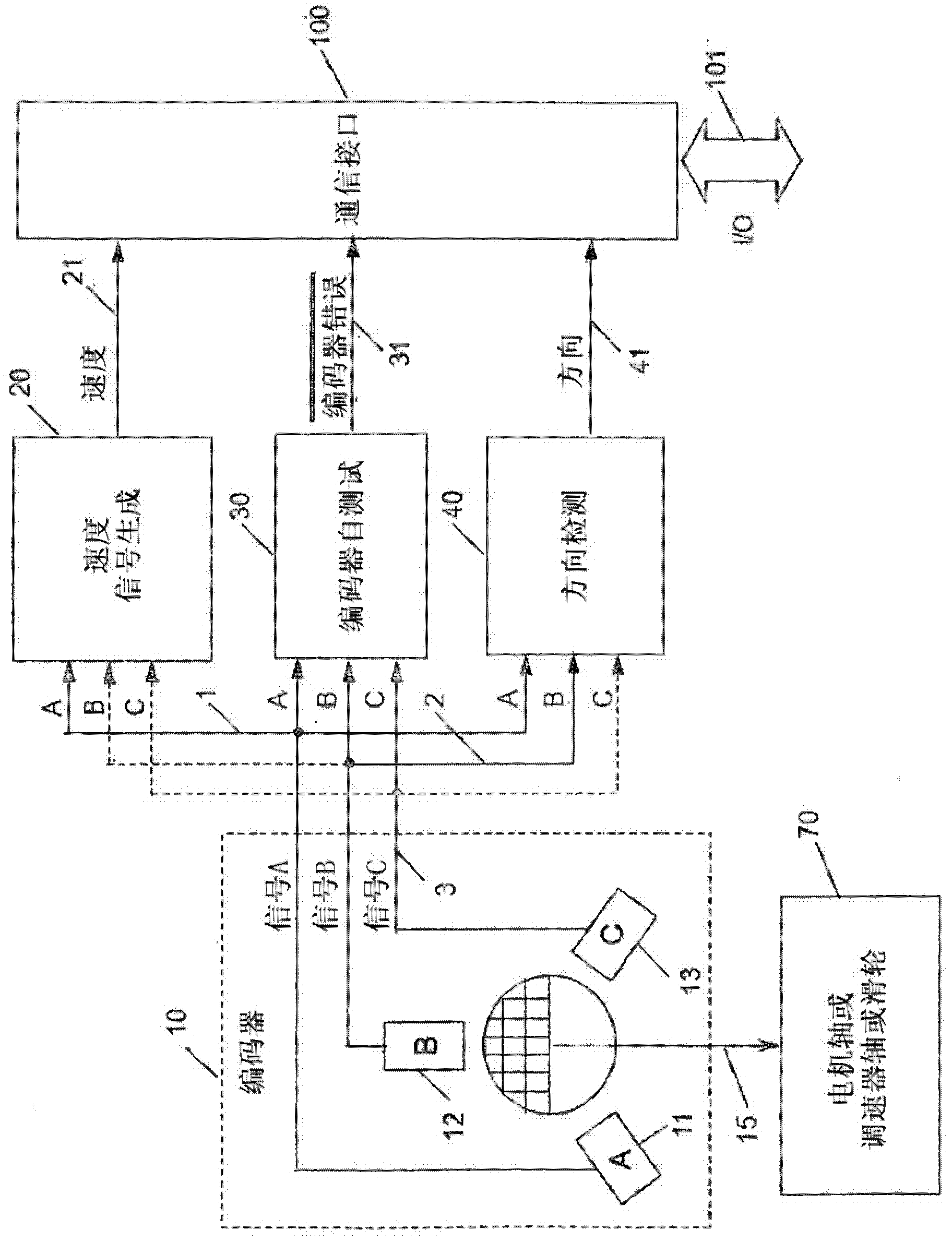

Sensing device

InactiveCN102472769AImplement self-testSpeed efficientRecording apparatusMeasurement arrangements for variableElectricityControl system

The present invention discloses a speed and movement direction sensing device. The sensing device includes an incremental encoder, which generates three pulses shifted by about 120 (electrical) degrees. A speed signal generation section receives the encoder signals and generates a pulse signal, which frequency is proportional with the frequency of the input signal. The encoder self-test section monitors the encoder states and detects encoder error based on the encoder signals and a direction detection section generates a direction signal based on the encoder pulses. The sensing device allows encoder self-test even in case of zero speed. The fault-tolerant speed and movement direction sensing device offers a higher reliability than the prior art and can be applied in motion control systems where high safety and integrity level is required.

Owner:MITSUBISHI ELECTRIC CORP

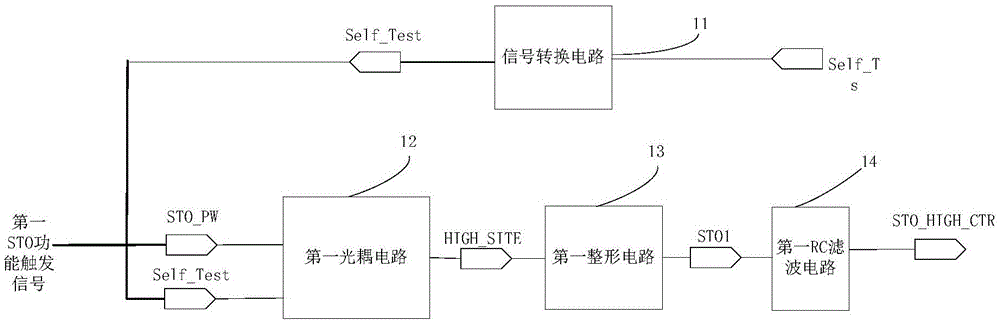

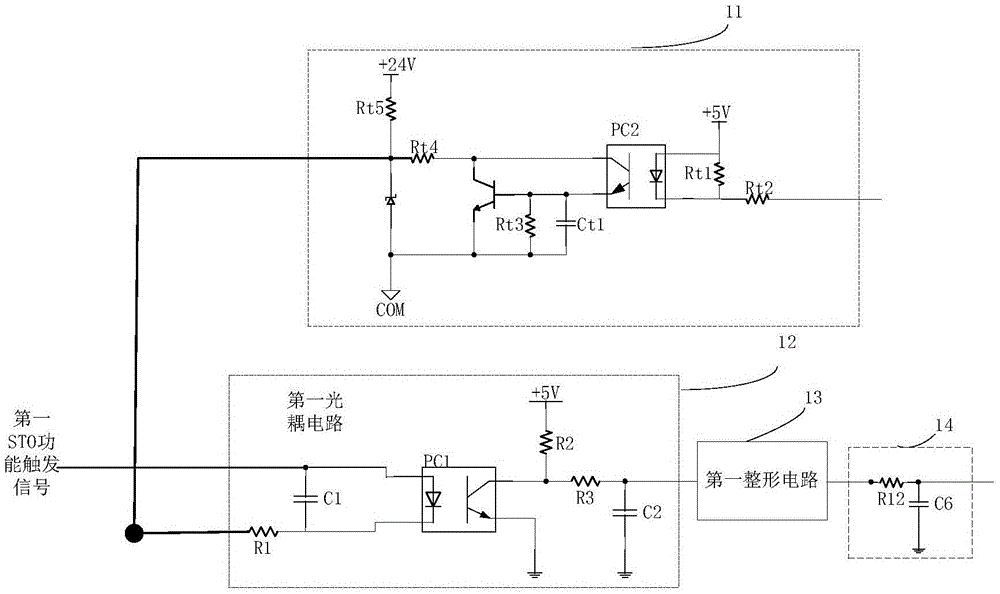

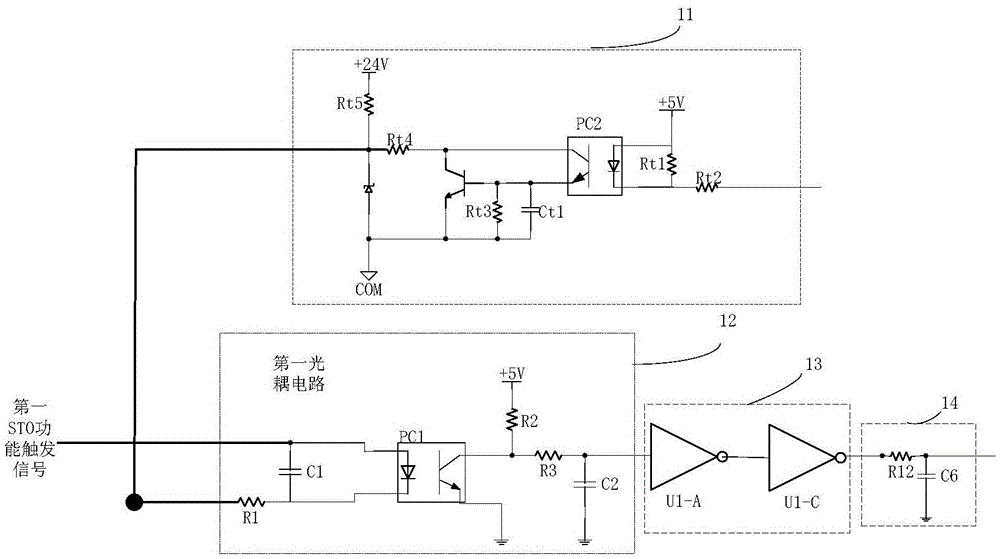

Safe torque off (STO) control circuit and system

ActiveCN105576952ANormal work does not affectImplement self-testPower conversion systemsControl circuitEmbedded system

The application provides a safe torque off (STO) control circuit and system. The STO control circuit comprises a signal conversion circuit, a first photocoupling circuit, a second photocoupling circuit, a first NOT gate, a second NOT gate, a third NOT gate, a fourth NOT gate, a first RC filter circuit and a second RC filter circuit, wherein the first photocoupling circuit comprises a first resistor, a second resistor, a third resistor, a first capacitor, a second capacitor, a first diode, a second diode, a third diode, a fourth diode, a first voltage stabilization diode and a first isolation photocoupler, and the second photocoupling circuit comprises a fourth resistor, a fifth resistor, a sixth resistor, a third capacitor, a fourth capacitor, a fifth diode, a sixth diode, a seventh diode, an eighth diode, a second voltage stabilization diode and a second isolation photocoupler. In the application, the STO control circuit provided by the invention is used for achieving an STO function and circuit self-detection.

Owner:INVT POWER ELECTRONICS SUZHOU CO LTD

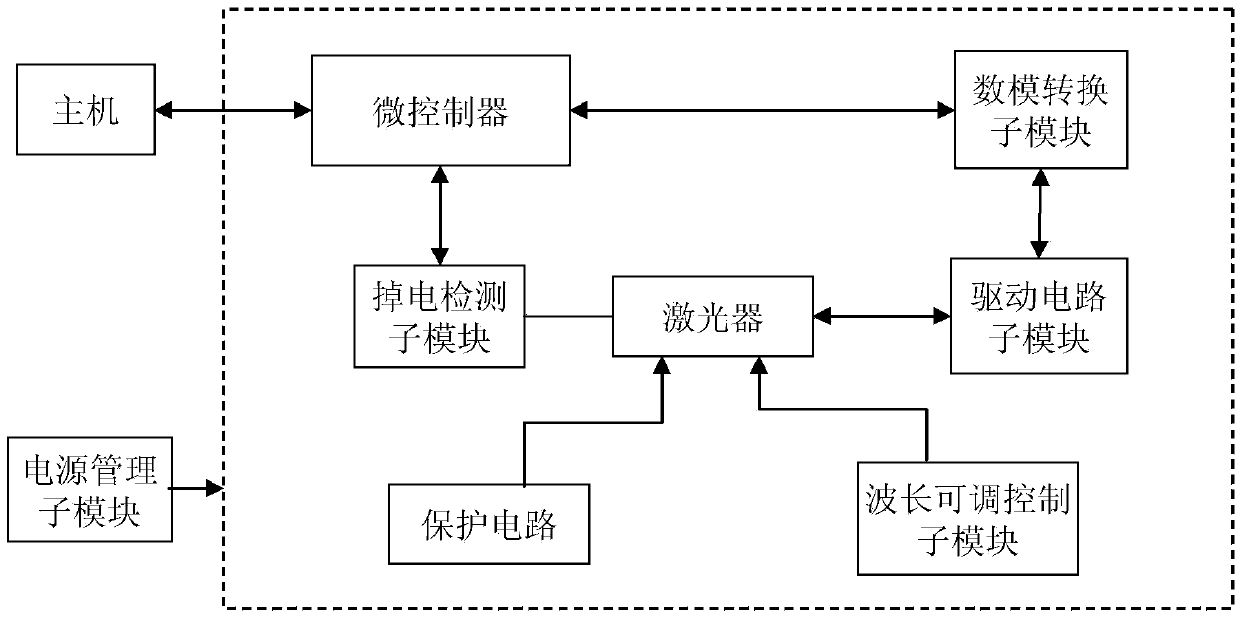

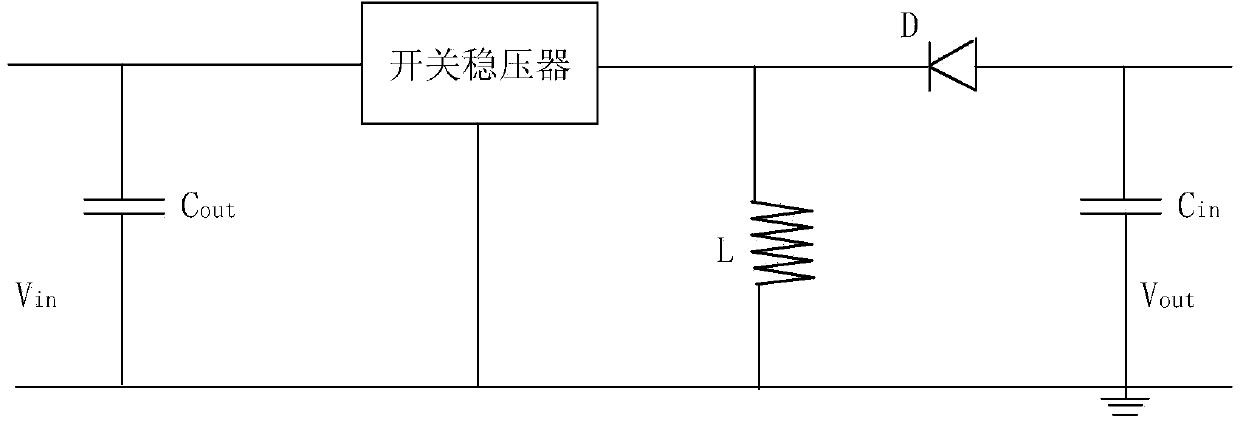

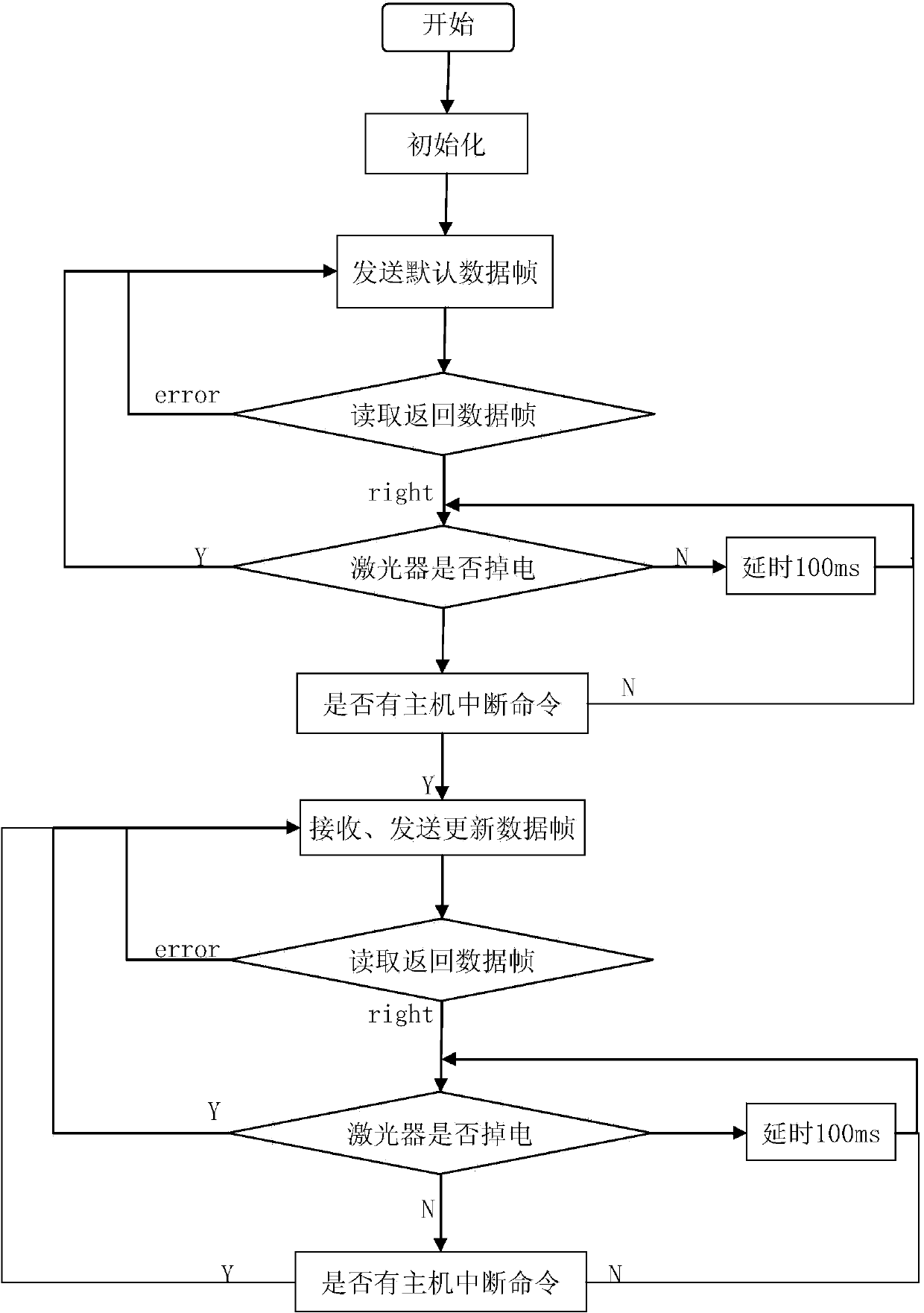

Narrow-linewidth tunable laser system and operation method thereof

ActiveCN103441423ARun without interruptionImprove robustnessLaser detailsSemiconductor lasersMicrocontrollerLine width

The invention provides a narrow-linewidth tunable laser system and an operation method thereof. A tunable laser module of the system comprises a semiconductor laser, a driving circuit and a wavelength-tunable control submodule, wherein the driving circuit and the wavelength-tunable control submodule are connected with the semiconductor laser. A switch voltage stabilizer, connected with an inductor and a diode, of a power management submodule enables positive voltage to be converted into negative voltage so as to supply electricity to the system. A microcontroller connected with a host is connected with the driving circuit through digital-to-analog conversion to transmit instructions of the host and states of the laser. The microcontroller and a power failure detection submodule are used for detecting circuit voltage of the laser at regular time, and power is recovered in time when power failure is found out. The operation method of the narrow-linewidth tunable laser system includes the steps that after being initialized, the microcontroller transmits preset default data frames to the laser, the data frames returned by the laser are read, the situation that the data frames have no error is determined, whether power failure occurs or not is detected at regular time, updated instructions of the host are received and transmitted to the laser, and the current working state information of the laser is transmitted to the host. The system only needs to be powered up by a single power supply and can be used easily in an embedded mode. A tuning control interface of the host is simple and visual, and reliable operation is guaranteed through power failure self-detection.

Owner:NO 34 RES INST OF CHINA ELECTRONICS TECH GRP

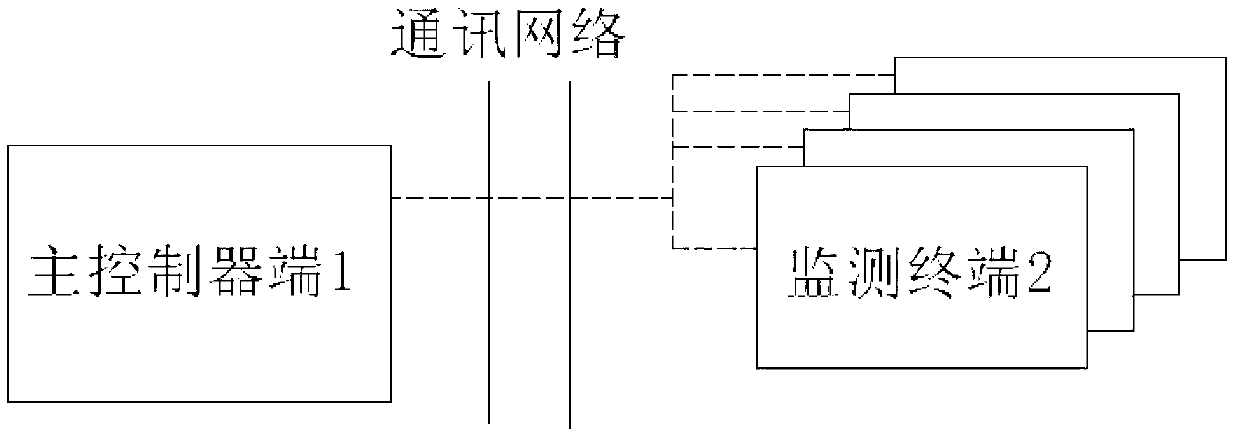

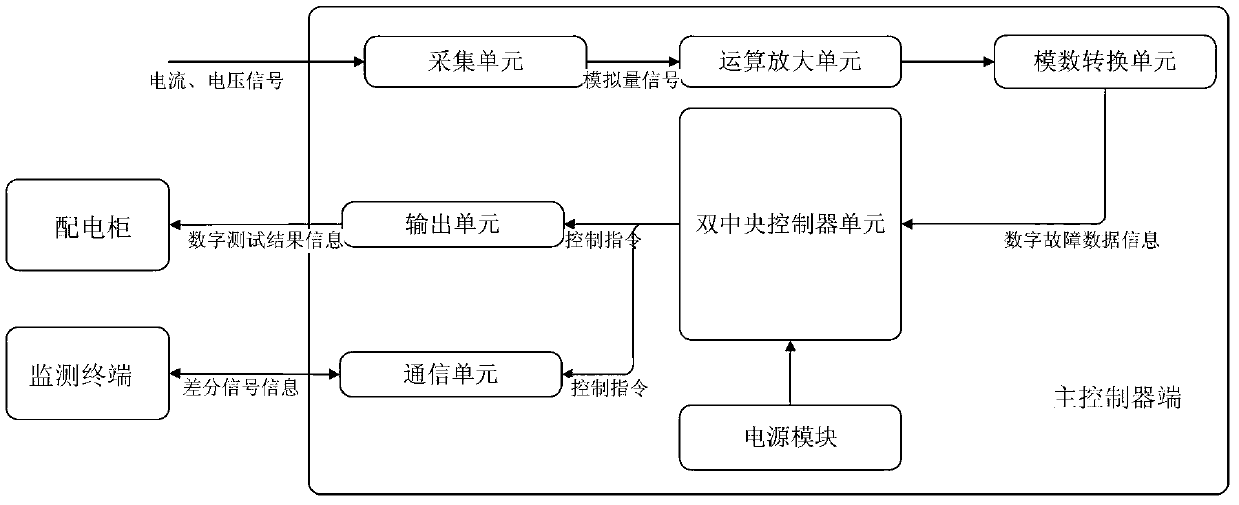

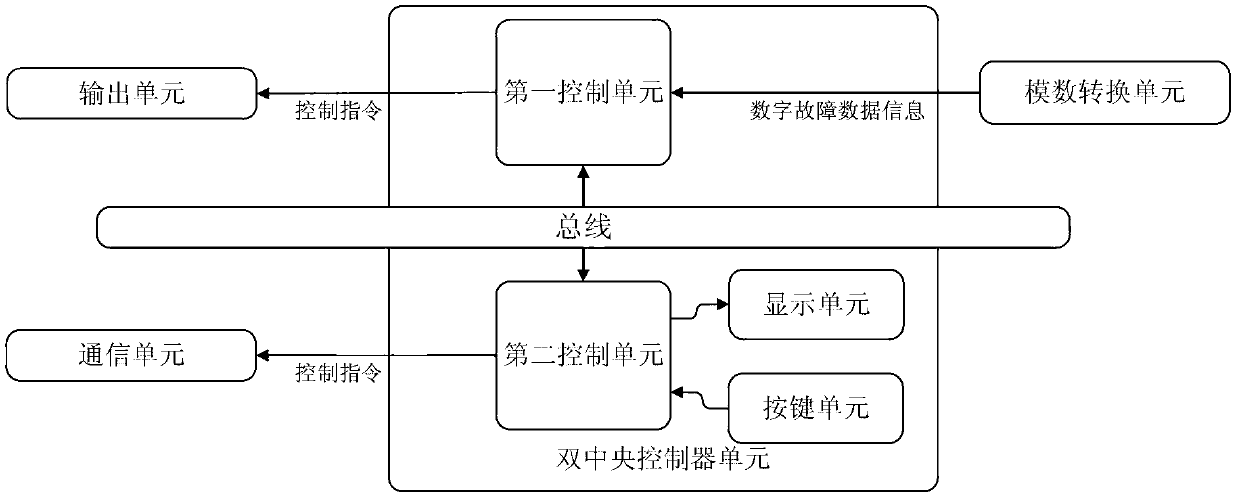

Mine protection power monitoring system

InactiveCN103107602AImplement self-testConvenient manual setting adjustmentCircuit arrangementsOvervoltageCurrent transducer

The invention discloses a mine protection power monitoring system. The mine protection power monitoring system comprises a main controller terminal and a plurality of monitoring terminals, wherein the main controller terminal and the plurality of monitoring terminals are connected through a communication network. The monitoring terminals output differential signal information to the main controller terminal and receive differential signal information of the main controller terminal. The mine protection power monitoring system can be used for a mine high-voltage distribution switch and a high-voltage magnetic starter, and contains 6kV and 10kV voltage classes and 5-630A rated operational currents. Because a double-central-controller unit is used for controlling, the power monitoring system is higher in precision, more accurate, more stable in performance and faster in processing speed, and can set and calibrate in a full digitalization mode. The power monitoring system is provided with protection functions such as undervoltage, overvoltage, overload, short circuit, phase equilibrium, earth leakage protection (grounding protection) and insulation monitoring, remote metering-remote signaling-remote controlling-remote regulating functions in a form of RS485 or a controller area network (CAN) bus, a calendar clock, and a fault memorizing and searching function. A current transformer or a hollow current transformer can be selected for use without replacing current transducers for different rated current classes.

Owner:上海久创电气自动化设备有限公司

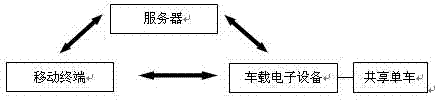

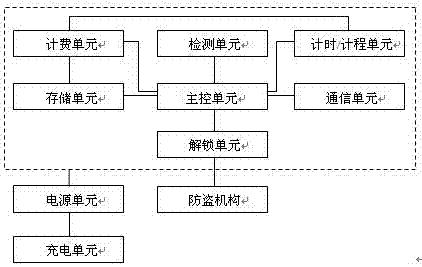

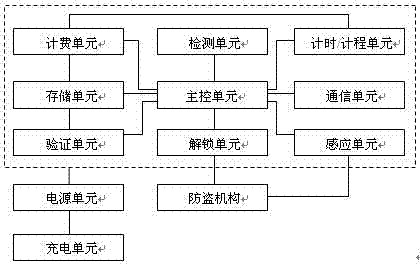

Shared bicycle control system

PendingCN107516384AReduce manual inspection costsLow costApparatus for meter-controlled dispensingTransmissionTelecommunicationsControl system

The invention discloses a shared bicycle control system which comprises a mobile terminal. A bicycle-mounted electronic device sends a bicycle using establishment request, and the bicycle-mounted electronic device sends user identity information carried in a connection establishment request to a server to be verified; according to a verification result, whether connection is established between the bicycle-mounted electronic device and the mobile terminal or not is controlled; whether an anti-theft mechanism is started or not is controlled according to the verification result; user account information carried in the bicycle using establishment request is stored when verification is successful, and charging is started; a bicycle using reservation request of the mobile terminal is received, the bicycle using right of the mobile terminal on a bicycle is reserved, and bicycle using requests of other users for the bicycle are filtered; a bicycle returning request of the mobile terminal is received, charging stops, the user account information is charged, and a bill is generated. According to the scheme, the function of reserving the bicycle for the users can be provided, different charging modes can be achieved, charging and other work of the original server are shared, and the system is simple and reasonable in structure.

Owner:CHENGDU UNI LINK ENERGY

Built-in self-test circuit, built-in self-test system and built-in self-test method for flash memory

The invention provides a built-in self-test circuit, a built-in self-test system and a built-in self-test method for a flash memory. The built-in self-test circuit comprises a self-reading test module, a self-erasing test module, a self-programming test module and a command conversion module, wherein the self-reading test module is used for testing reading operation of the flash memory and sending a reading test result to the command conversion module, the self-erasing test module is used for testing erasing operation of the flash memory and sending an erasing test result to the command conversion module, the self-programming test module is used for testing programming operation of the flash memory and sending a programming test result to the command conversion module, and the command conversion module is used for sending test commands inputted by a test machine to the self-reading test module, the self-erasing test module and the self-programming test module, and sending the reading test result, the erasing test result and the programming test result to the test machine.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

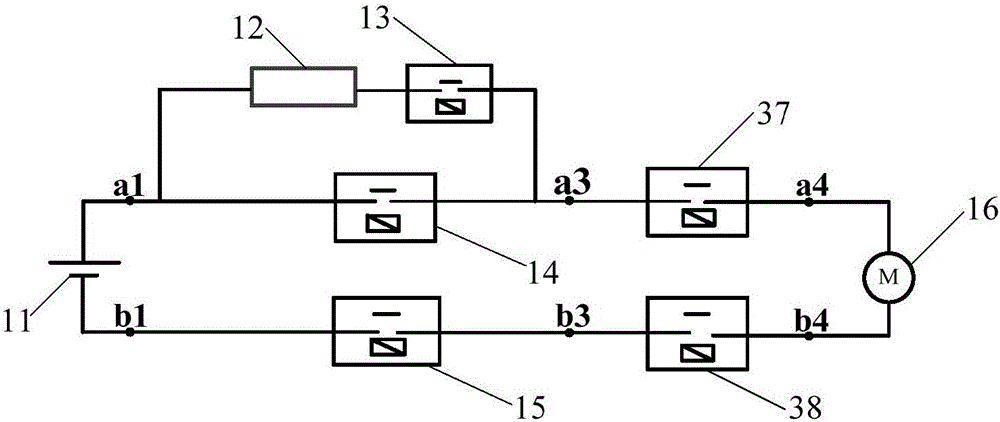

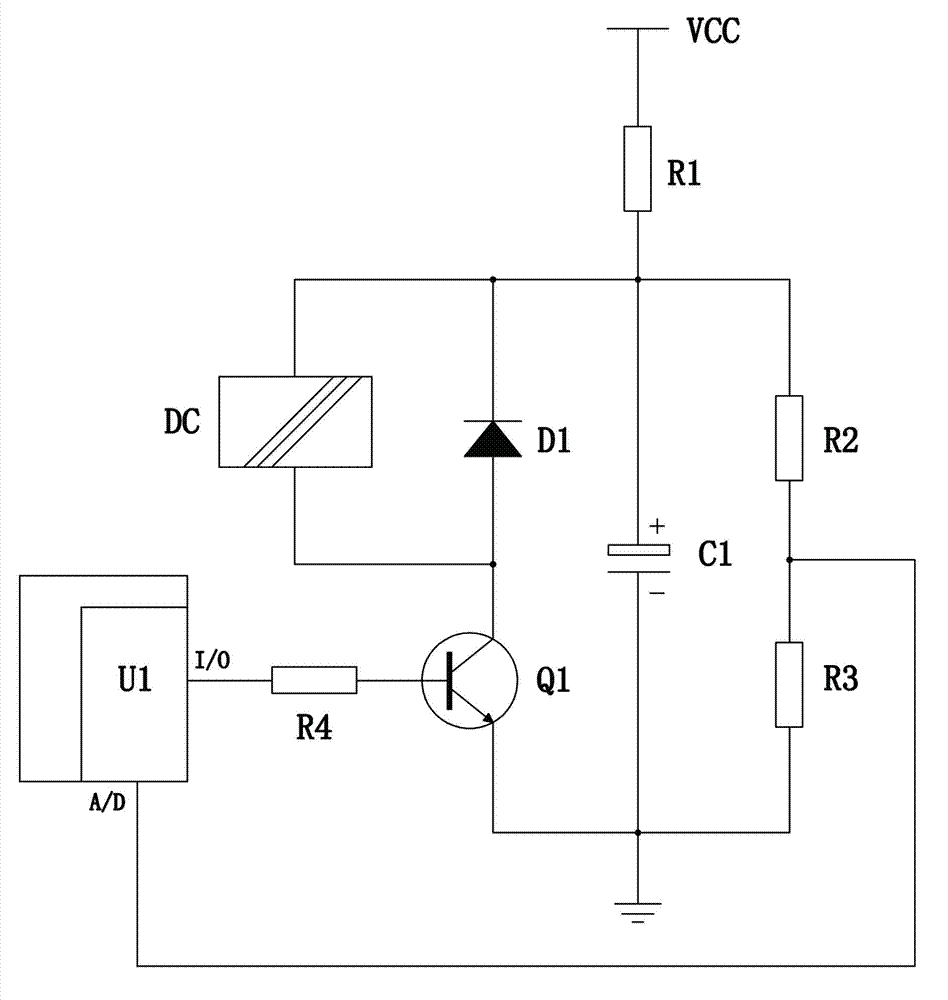

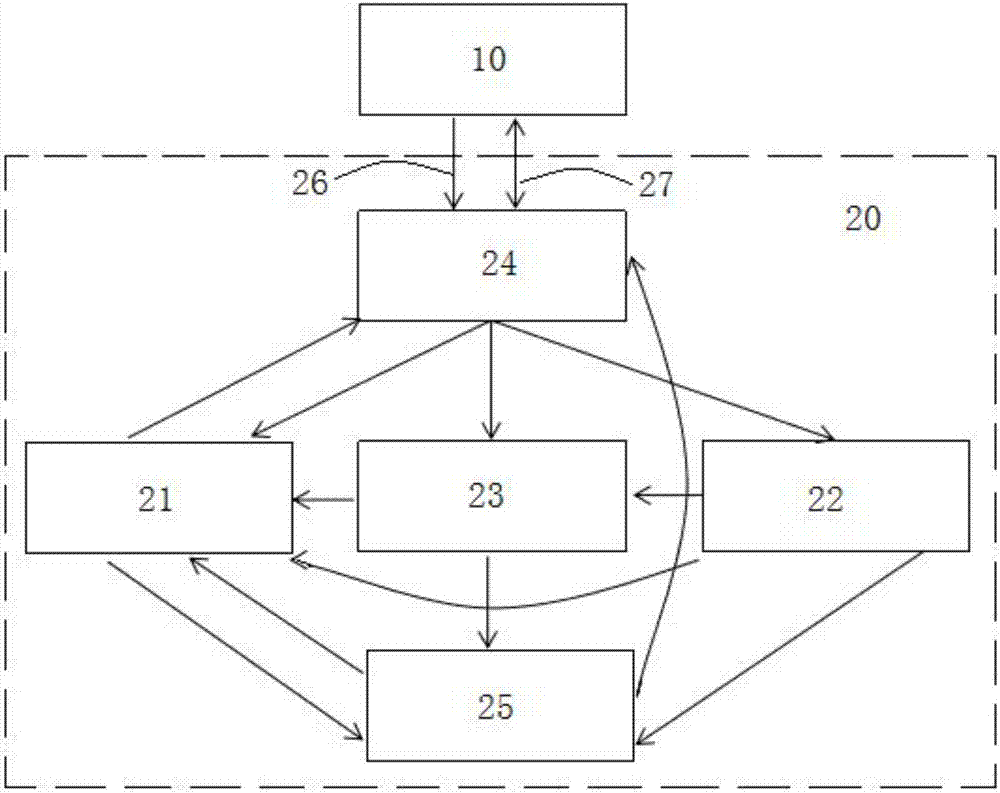

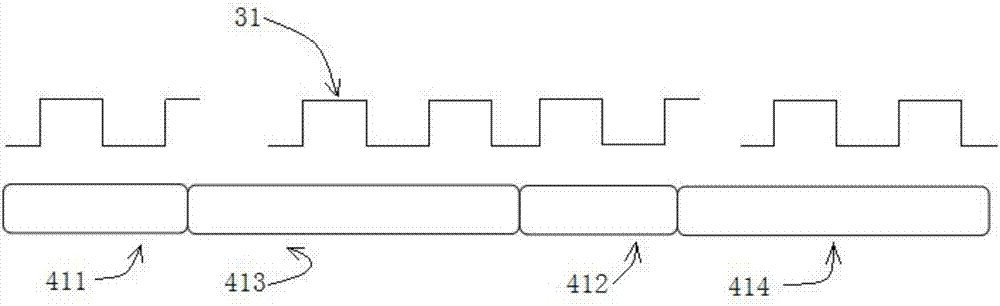

A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g]

PendingCN108957278AAchieve protectionImplement fault diagnosisBipolar transistor testingElectricityAnalog signal

The invention provides a large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g]. The method comprises the steps of collecting a gate current signal of an IGBT;performing integrating and resetting operation the collected IGBT gate current signal to obtain a gate charge analog signal Q[g] of the IGBT in different switching intervals; converting the obtainedgate charge analog signal Q[g] into a digital signal; performing real-time monitoring of the gate charges of the IGBT in the different switching intervals and comparing the monitored gate charges withthe gate charges in corresponding switching intervals in the normal switching states; and the specific fault type is judged according to the comparison result, and the fault type information is output; according to the fault type information, the IGBT is directly turned off, or the fault information is transmitted to an upper computer which will turn off the IGBT, thereby realizing rapid system protection and safe shutdown. Through the utilization of the method and apparatus of the invention, IGBT self-check and on-line real-time monitoring before power-on can be realized, thereby substantially reducing the risk of IGBT damages.

Owner:CHINA UNIV OF MINING & TECH

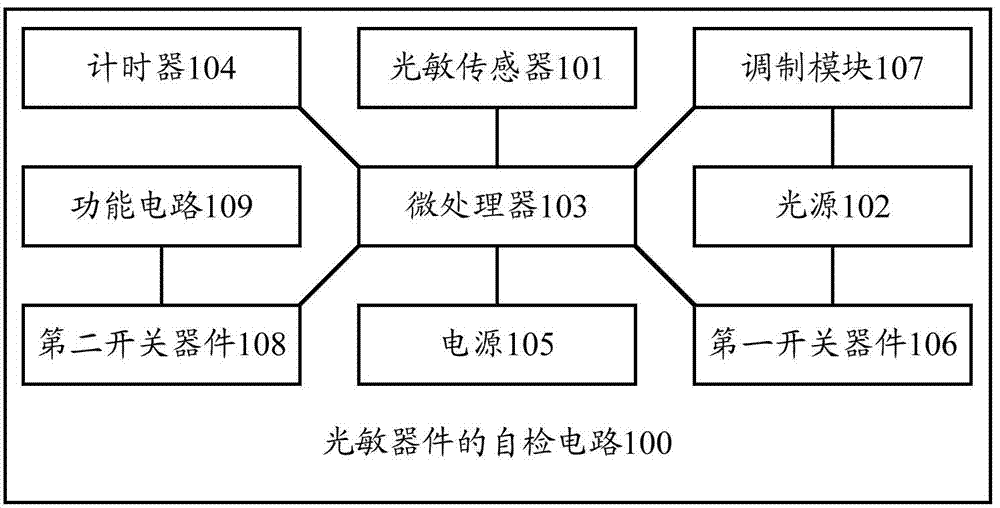

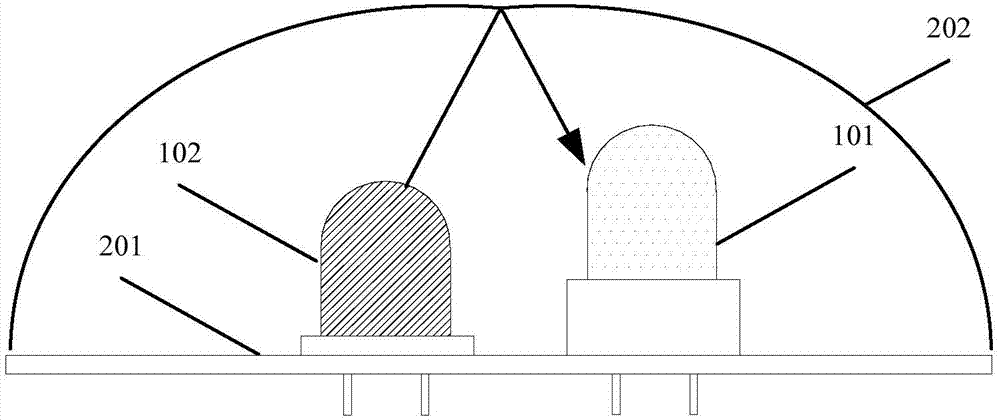

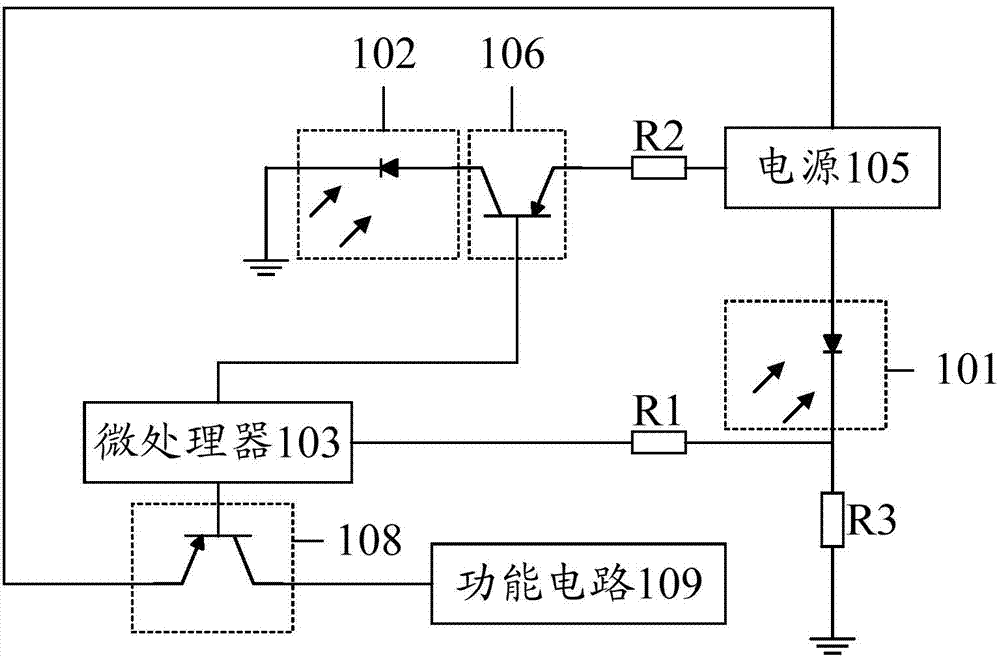

Self-checking circuit, self-checking method and self-checking system for photosensitive element as well as air conditioner

InactiveCN104501851AImplement self-testJudgment reliabilitySpace heating and ventilation safety systemsLighting and heating apparatusEngineeringSelf checking

The invention provides a self-checking circuit for a photosensitive element. The self-checking circuit comprises a photosensitive sensor, a light source and a micro processor, wherein the light source is arranged within a photosensitive range of the photosensitive sensor and used for providing a detecting light source for the photosensitive sensor in a self-checking process of the photosensitive sensor; the micro processor is connected to the light source and used for controlling the light source to switch on for realizing the self-checking process of the photosensitive element. The invention further provides a self-checking method and a self-checking system for a photosensitive element as well as an air conditioner. According to the technical scheme adopted by the invention, the self-checking process of the photosensitive element is realized so as to conveniently judge whether the photosensitive element effectively works or not; besides, the reliability of the photosensitive element is timely judged, so that the micro processor can be used for accurately obtaining a test signal of the photosensitive element and accurately controlling a functional module.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD

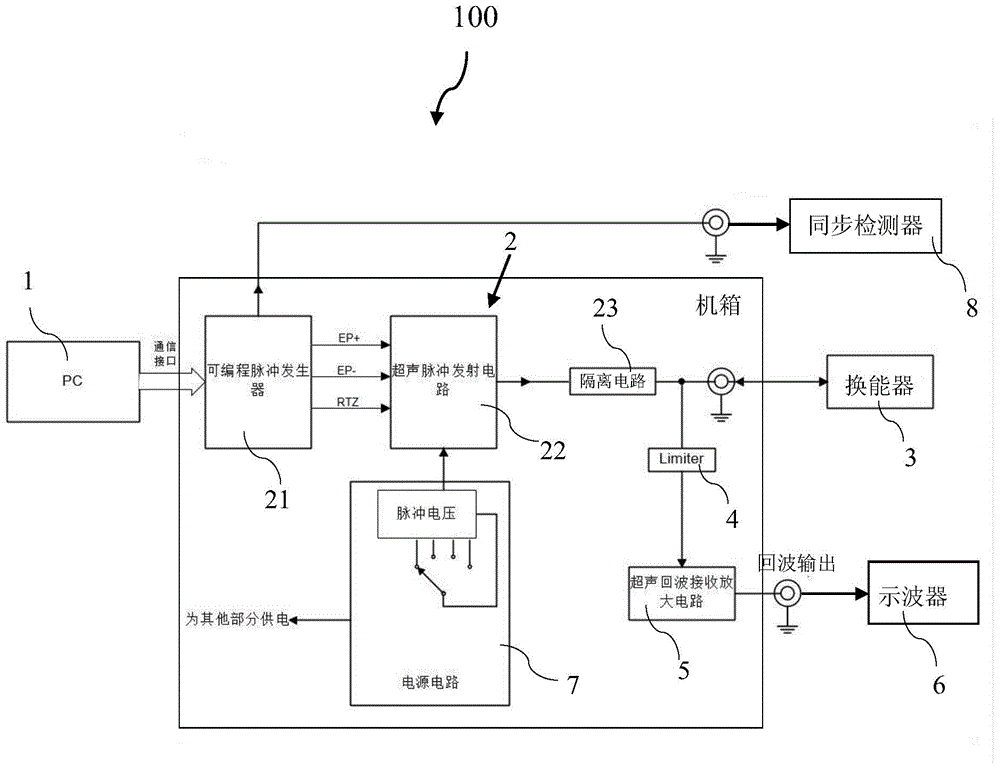

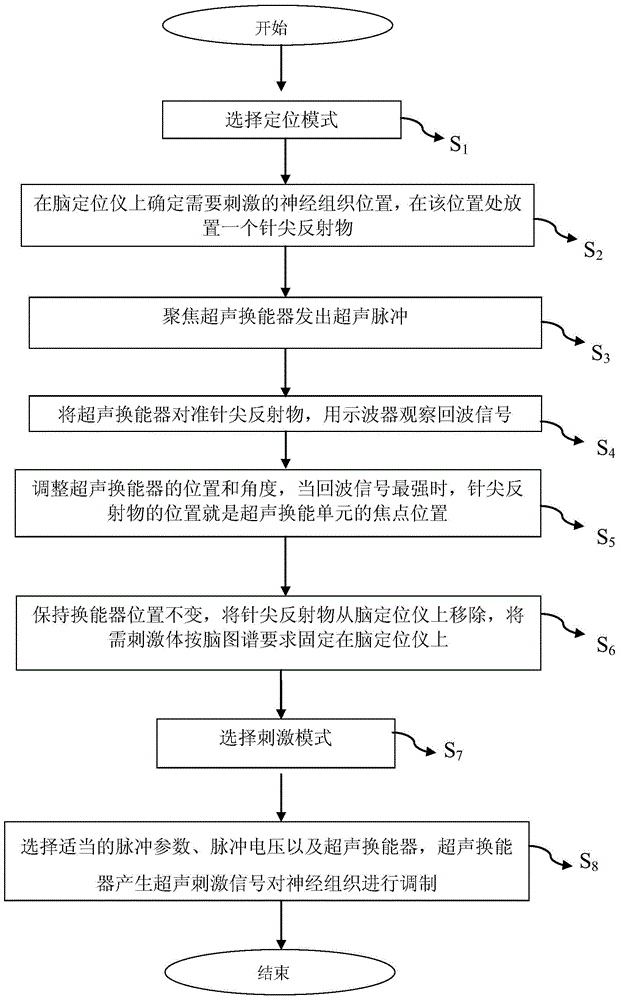

Transcranial ultrasonic stimulation device and stimulation method

InactiveCN104548392AReduce volumeHigh spatial positioning resolutionUltrasound therapySpatial OrientationsSonification

The invention provides a transcranial ultrasonic stimulation device and a stimulation method for carrying out nervous tissue orientation and neuromodulation through transcranial ultrasonic stimulation. The transcranial ultrasonic stimulation device comprises an upper computer unit, an ultrasonic pulse transmission unit, an ultrasonic transduction unit and a power circuit. The transcranial ultrasonic stimulation device adopts the integrated circuit mode and further comprises an echo amplification circuit. The focal distance of the ultrasonic transduction unit is 30 mm. The ultrasonic pulse transmission voltage is adjusted by adjusting the power supply voltage, and therefore the transcranial ultrasonic stimulation device is small in size and high in spatial orientation resolution ratio and can achieve system self-inspection. Meanwhile, because the ultrasonic intensity can be adjusted, a low ultrasonic intensity can be selected for carrying out nervous tissue orientation and neuromodulation, a high ultrasonic intensity can be selected for carrying out tissue damage, and the positional information of the stimulation part can be verified.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

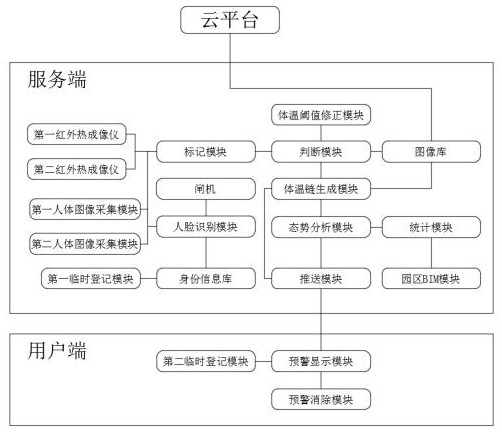

Smart park situation awareness system based on Internet of Things

ActiveCN111815841AImplement self-testRealize traceabilitySensing radiation from moving bodiesIndividual entry/exit registersInformation repositoryThe Internet

The invention discloses a smart park situation awareness system based on the Internet of Things, and relates to the technical field of smart parks. The system comprises a cloud platform, a server anda client. The server comprises an infrared thermal imager, a human body image acquisition module, a marking module, an identity information base, a face recognition module, a gate, a judgment module,a body temperature chain generation module, a picture library and a pushing module. By monitoring the body temperature of people entering the park, a body temperature chain of a sensitive person is constructed and pushed to the sensitive person. The client comprises an early warning display module and an early warning elimination module, displays the body temperature chain, and eliminates sensitive person marks by uploading too high body temperature explanation or doctor seeing records. The body temperature of people in the park is monitored in a centralized mode, and when centralized body temperature anomaly occurs, early warning is given out in time.

Owner:杭州绿城信息技术有限公司

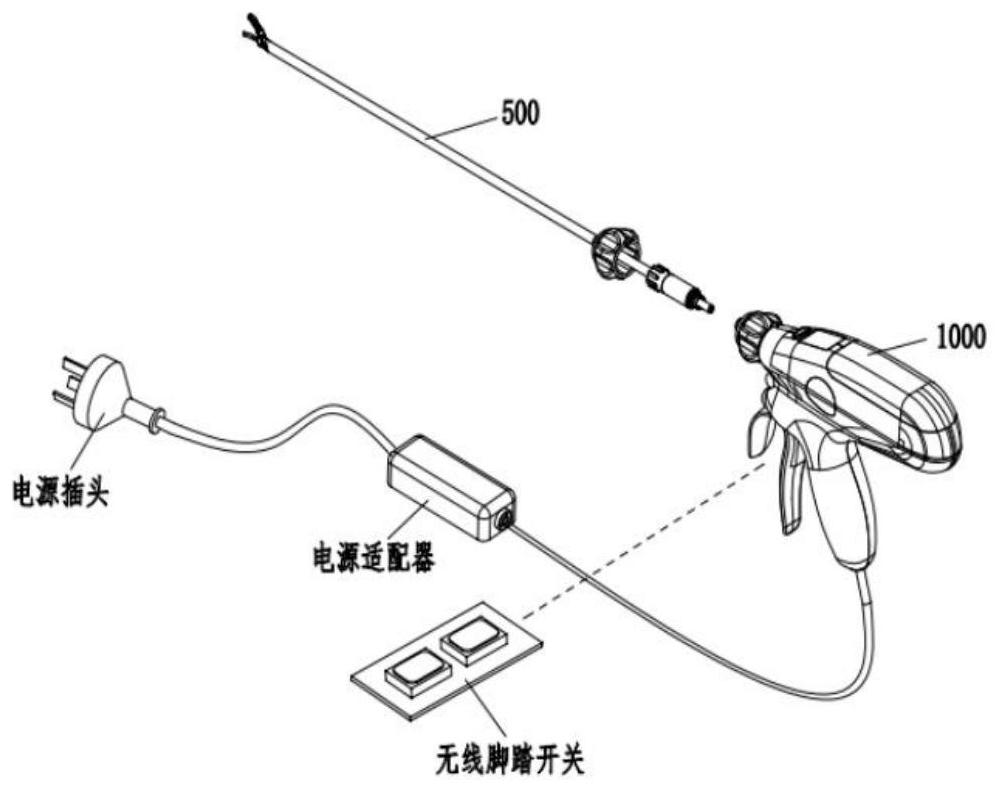

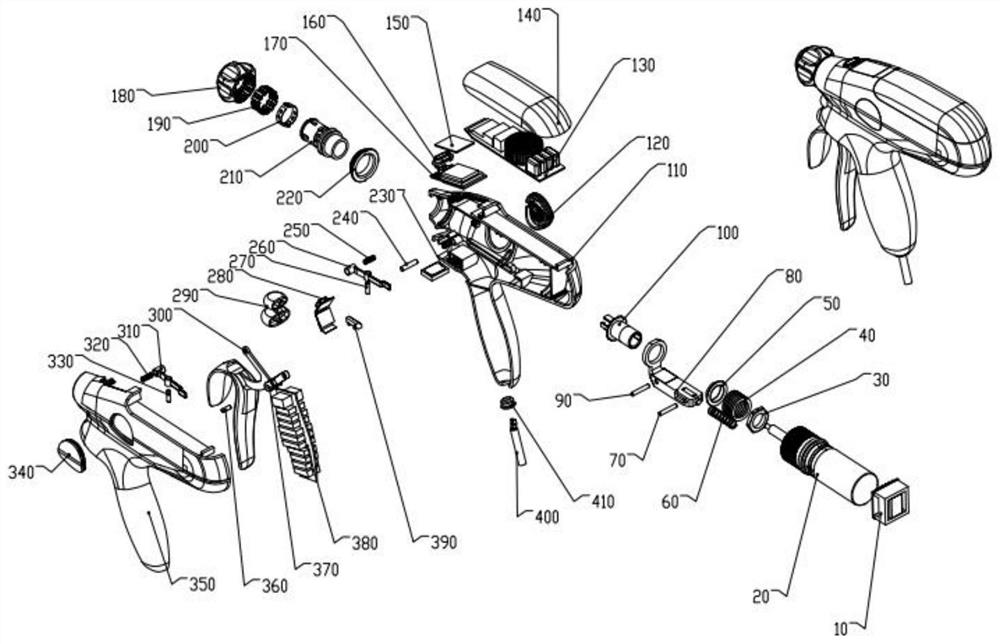

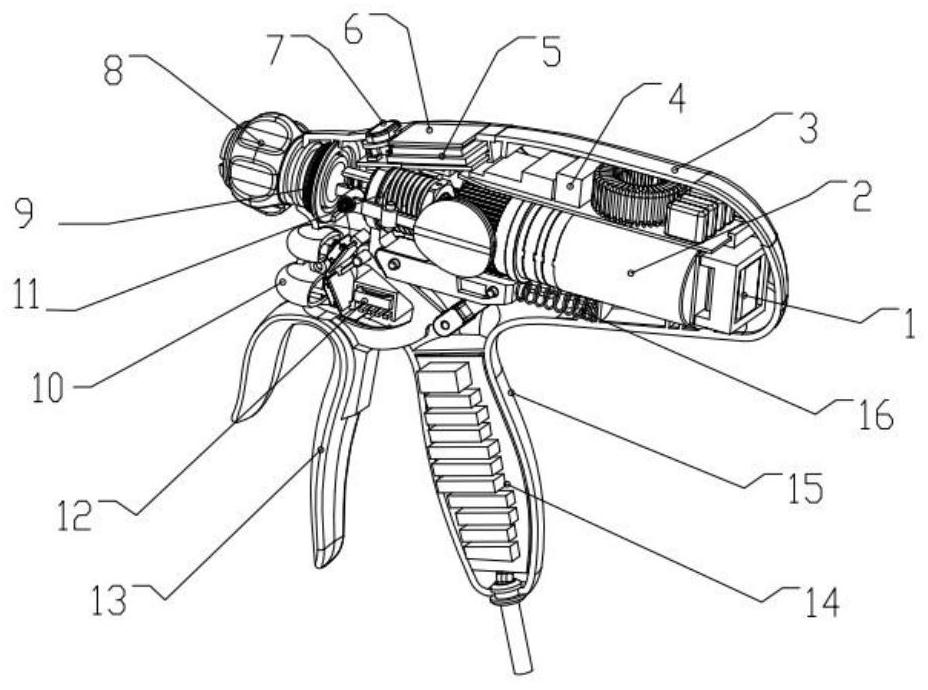

Ultrasonic scalpel handle with ultrasonic generator function, ultrasonic scalpel system and using method of ultrasonic scalpel system

InactiveCN112237465AReduce usageReduce volumeMagnetic/electric field screeningSurgeryEngineeringEnergy converter

The invention discloses an ultrasonic scalpel handle with an ultrasonic generator function. The ultrasonic scalpel handle comprises a handle outer shell, a handle connecting mechanism integrated witha torque wrench is arranged at the head of the handle outer shell, and the handle connecting mechanism is used for being connected with a cutter; a cavity is arranged in the handle outer shell, and atransformer, an energy converter, a first PCB plate, a second PCB plate, gear keys and a handle are arranged in the cavity; the PCB power plate is arranged at the top of the cavity; the transformer isarranged at the tail end of the cavity; the PCB control panel is arranged at the position of a handle of the cavity; the first PCB plate and the second PCB plate can be set to be control panels or power panels; the gear key is arranged at the front part of the handle outer shell and is used for switching high and low power gears; and the handle is arranged at the front part of the handle outer shell and is used for controlling the opening and closing of the cutter. The invention further discloses an ultrasonic scalpel system with the ultrasonic generator function.

Owner:ENSURGE MEDICAL (SUZHOU) CO LTD

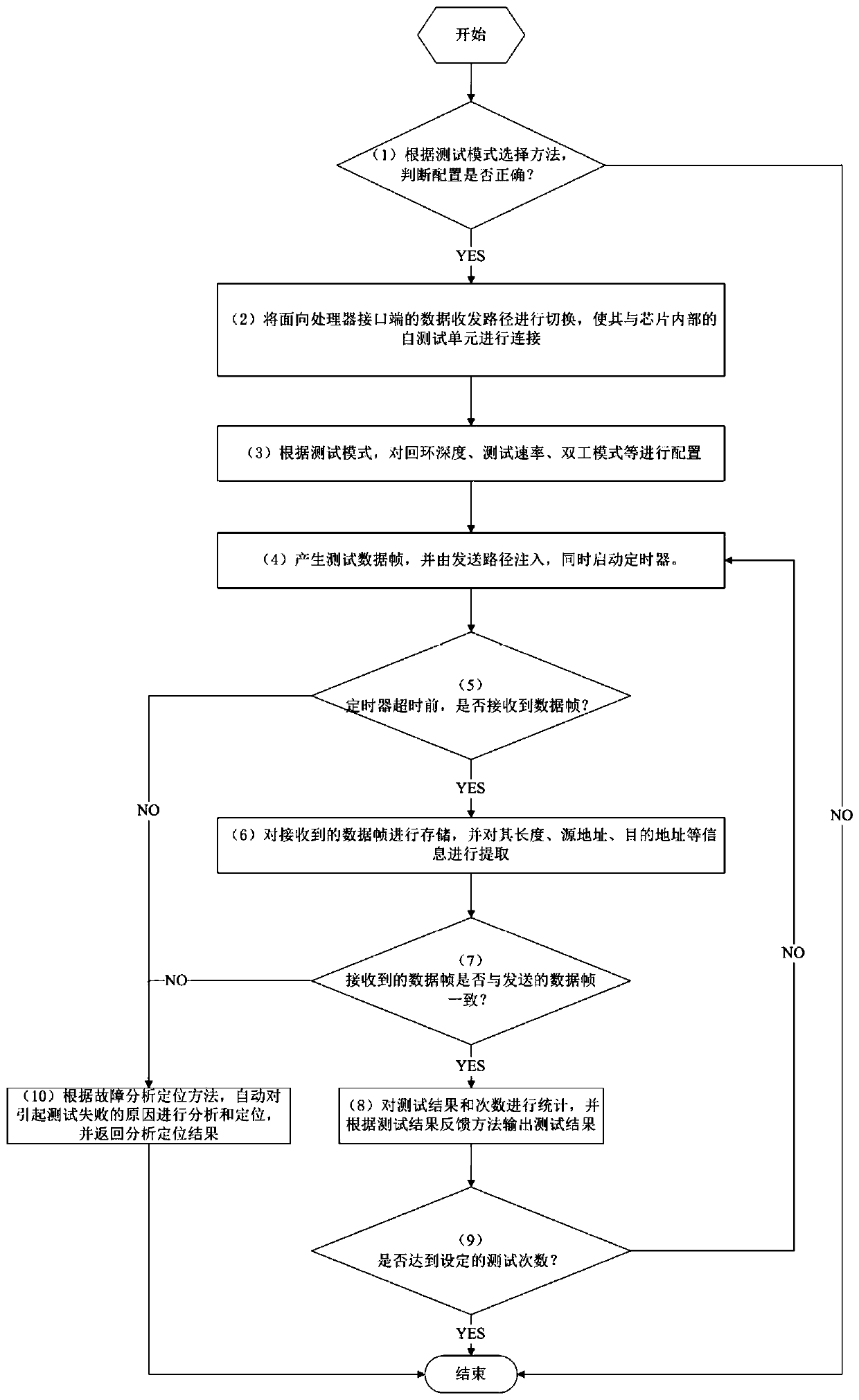

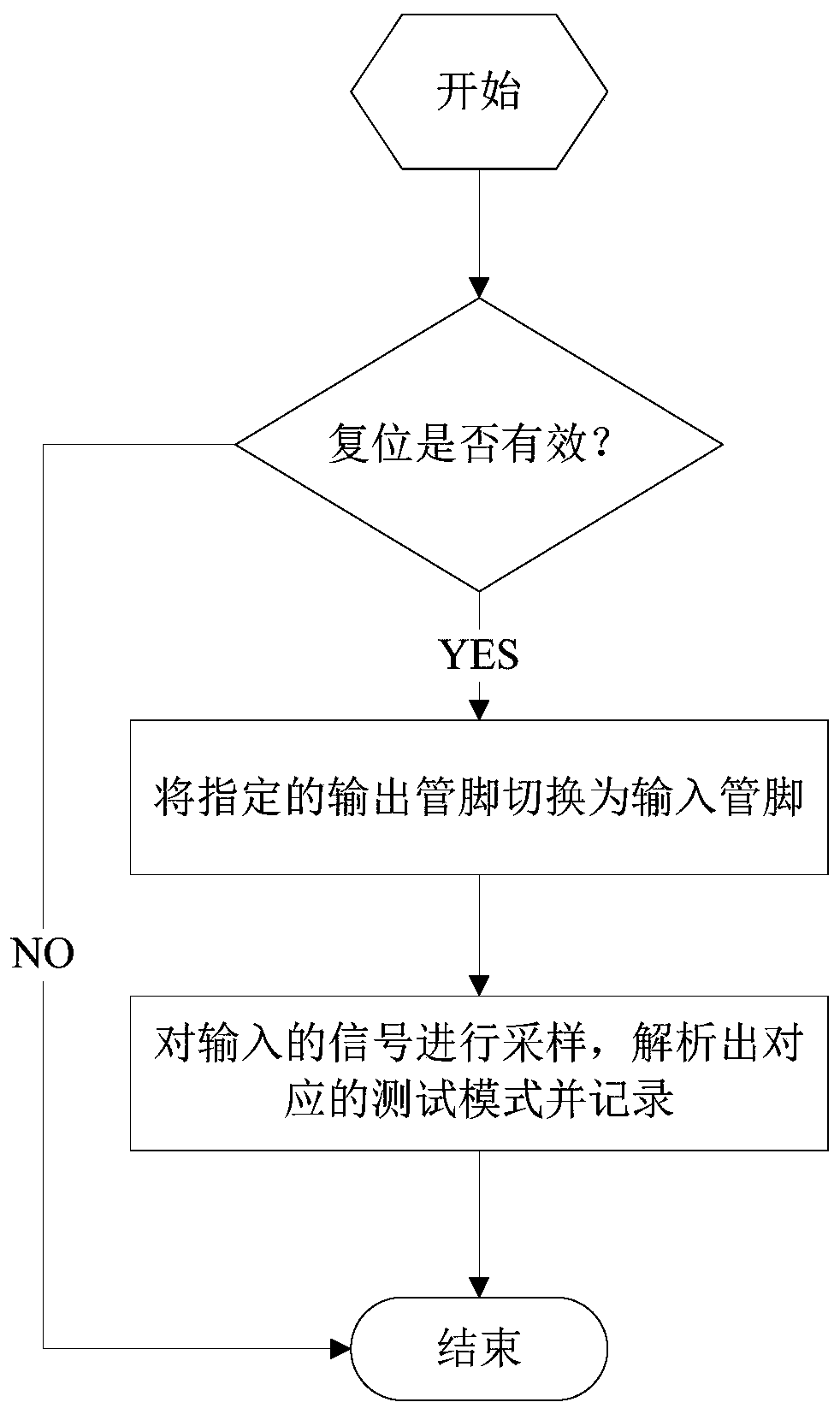

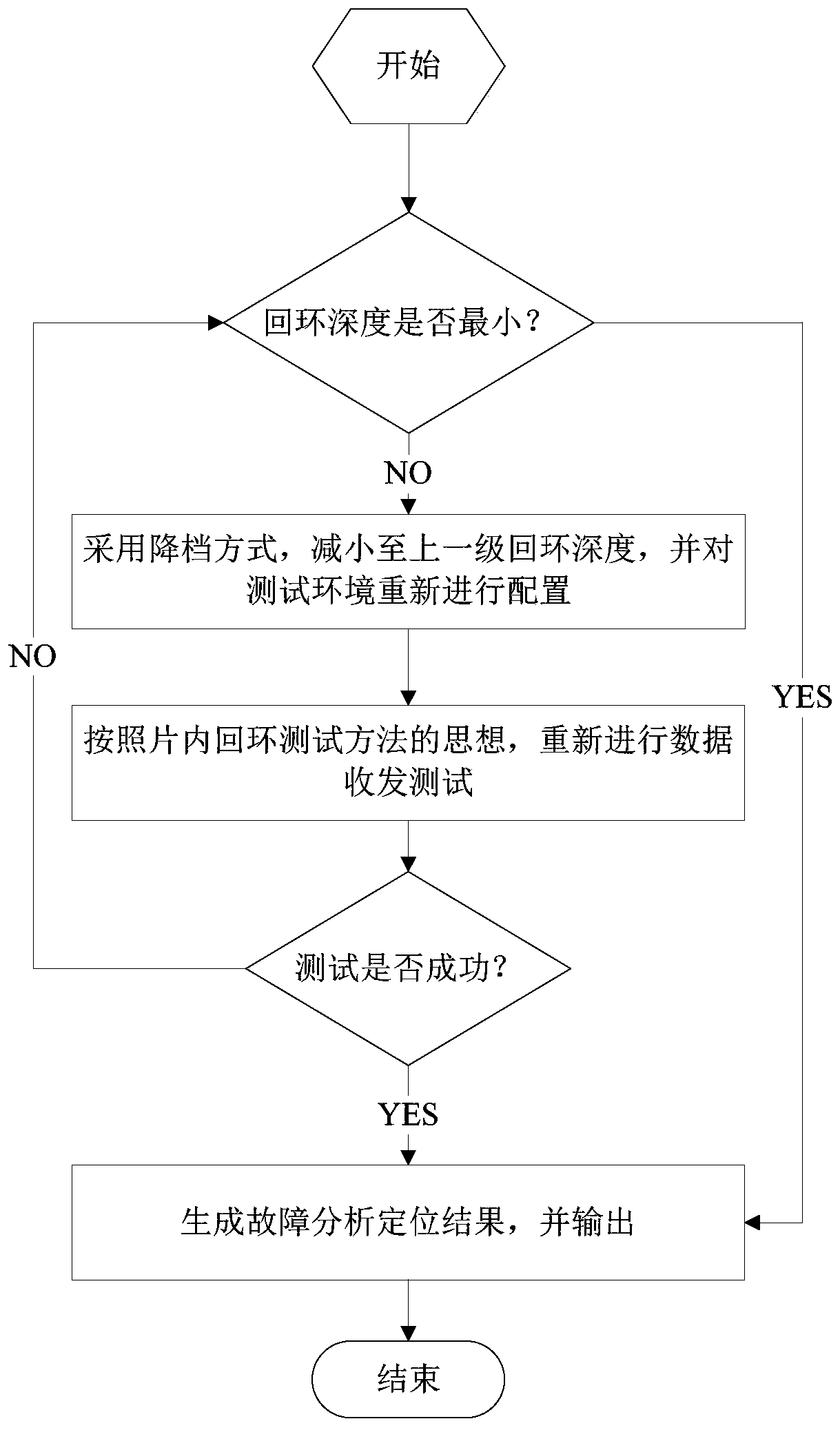

Built-in self-test method and system for Ethernet controller transceiving path

ActiveCN111221694ASpeed up the processImprove test efficiencyFaulty hardware testing methodsMultiplexingEthernet

The invention discloses a built-in self-test method and a built-in self-test system for an Ethernet controller transceiving path, and the method comprises the steps: adopting the concept of on-chip loopback to construct a path in which data is rewound from a transmitting path to a receiving path; generating a test excitation in a controller, comparing and analyzing the results, determining whetherthe core function of the controller and a transceiving access operate normally or not, and performing automatic positioning when a fault occurs; employing a pin multiplexing mode , so flexible configuration and output of a test mode and the test results are realized.

Owner:XIAN MICROELECTRONICS TECH INST

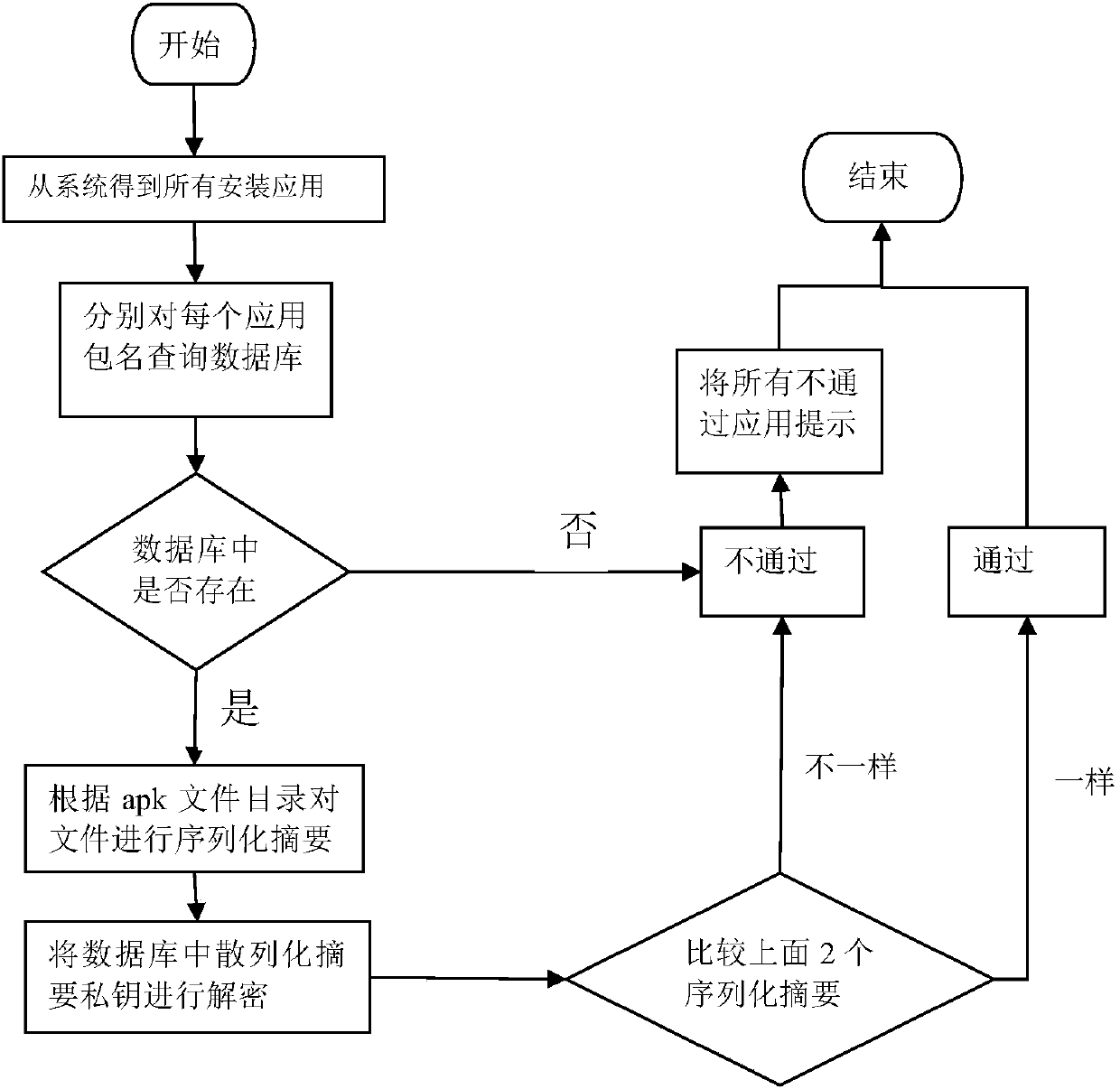

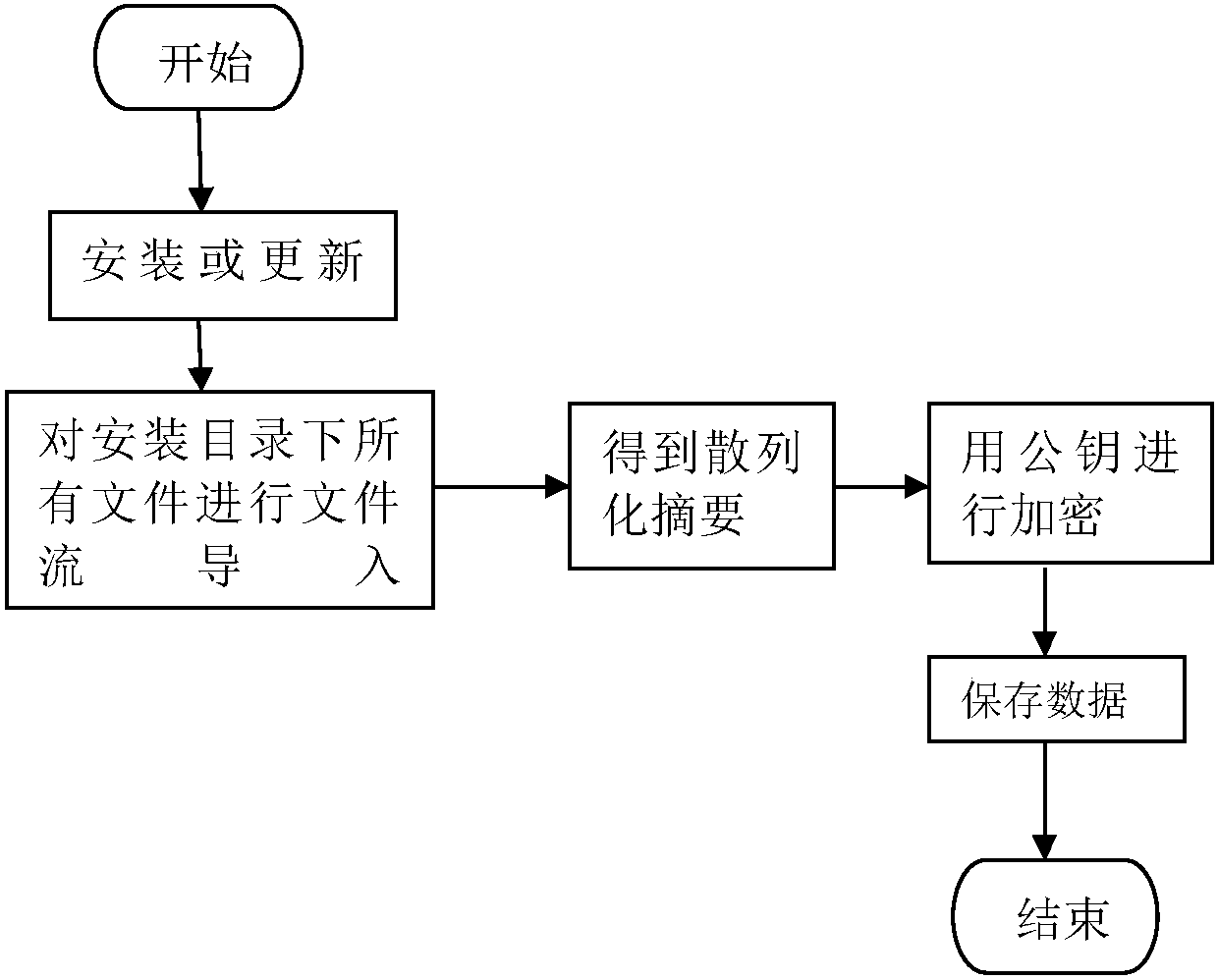

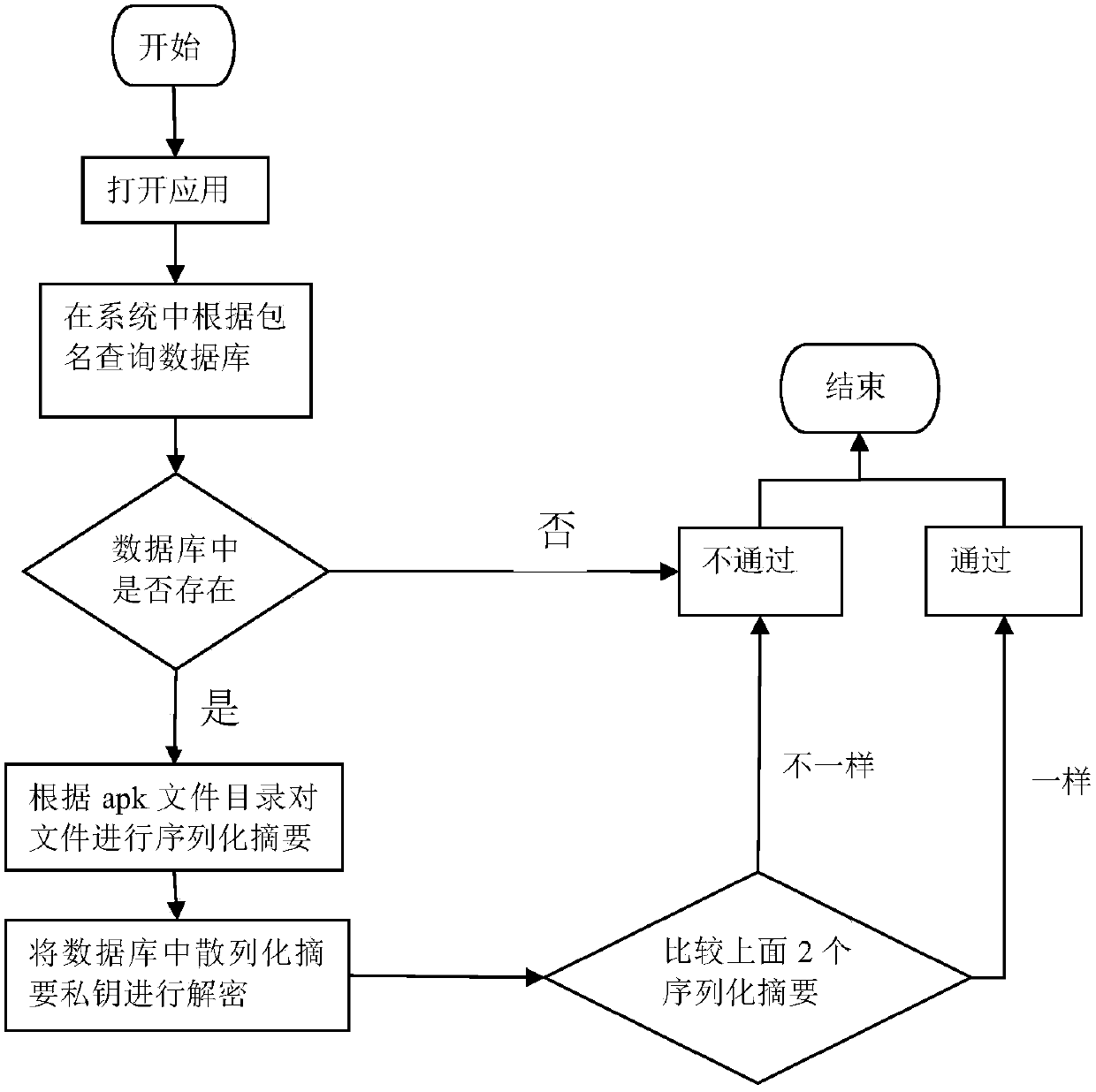

Self-checking method applied to Android intelligent-terminal

InactiveCN107908962AImplement self-testEasy to useEncryption apparatus with shift registers/memoriesPublic key for secure communicationApplication softwareComputer science

The invention discloses a self-checking method applied to an Android intelligent-terminal. The method is characterized in that the method includes the following steps: 101, after Android mobile-phoneapplication program installation or updating, encrypting and backing up all file data of mobile-phone application programs, and then sending data into a database; 102, firstly hashing all files of each program in a mobile phone to obtain hashing digests; 103, finding hashing data, which are encrypted through a public key, in the database, and carrying out decryption; and 104, carrying out decryption comparison with previous hashing results, if comparison is inconsistent, determining that the application programs are already modified, and not allowing the same to be opened in a system, and if comparison is consistent, not limiting user use. According to the method, application program self-checking can be realized in real time, cases where the programs are modified are avoided, use of the application programs is enabled to be safer and more reliable, and potential risks brought by use of applications of which data and files are modified are eliminated.

Owner:SHENZHEN TOPWISE COMM CO LTD

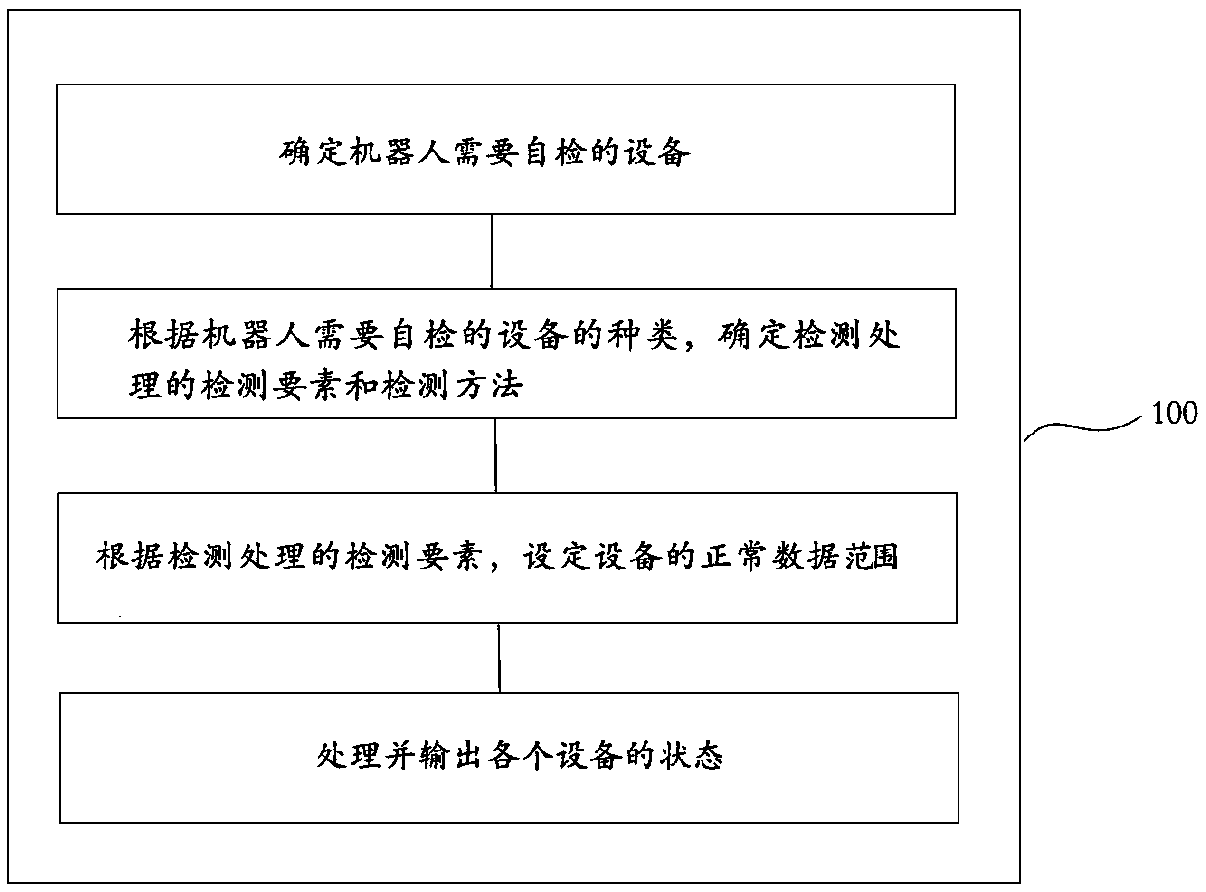

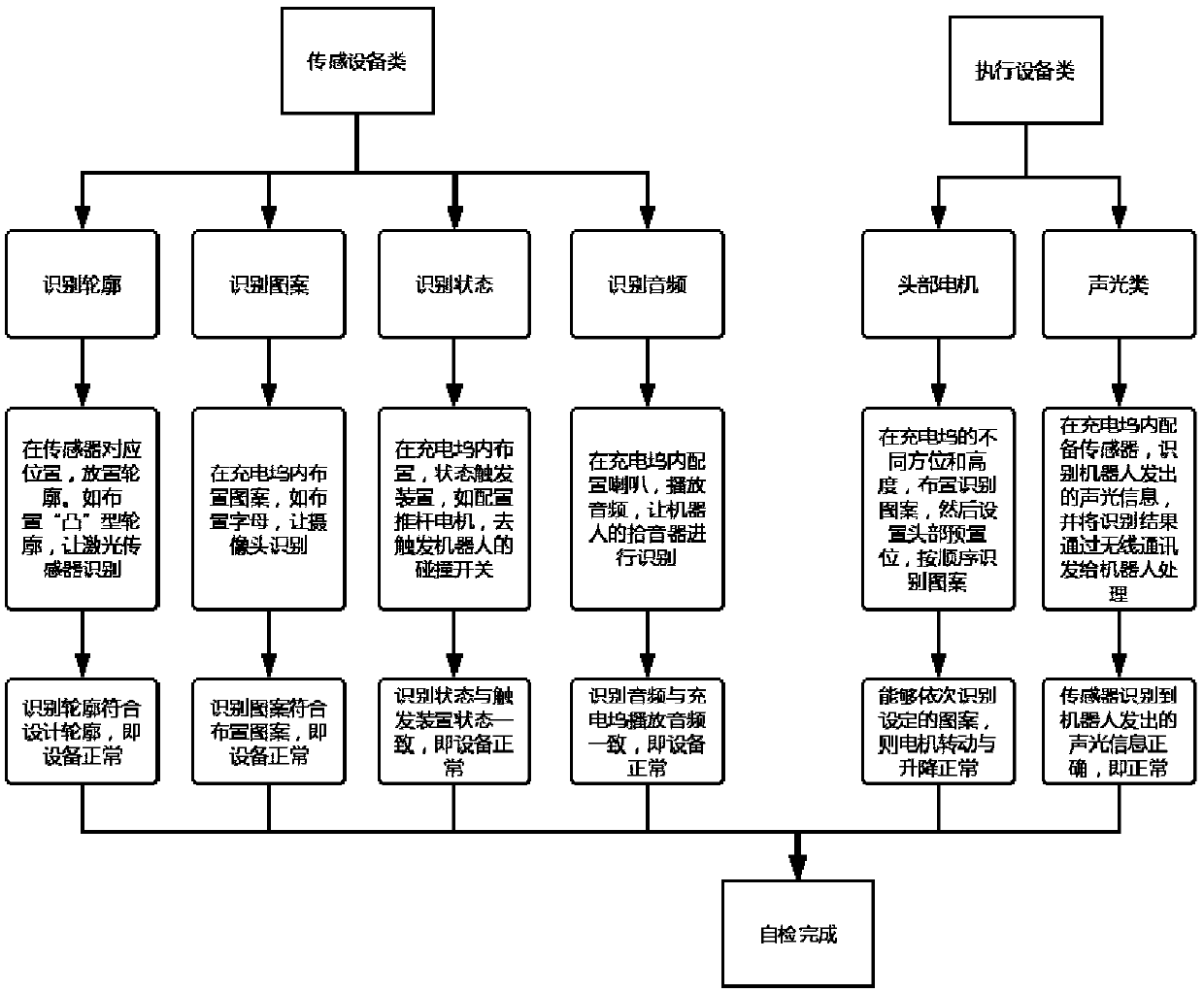

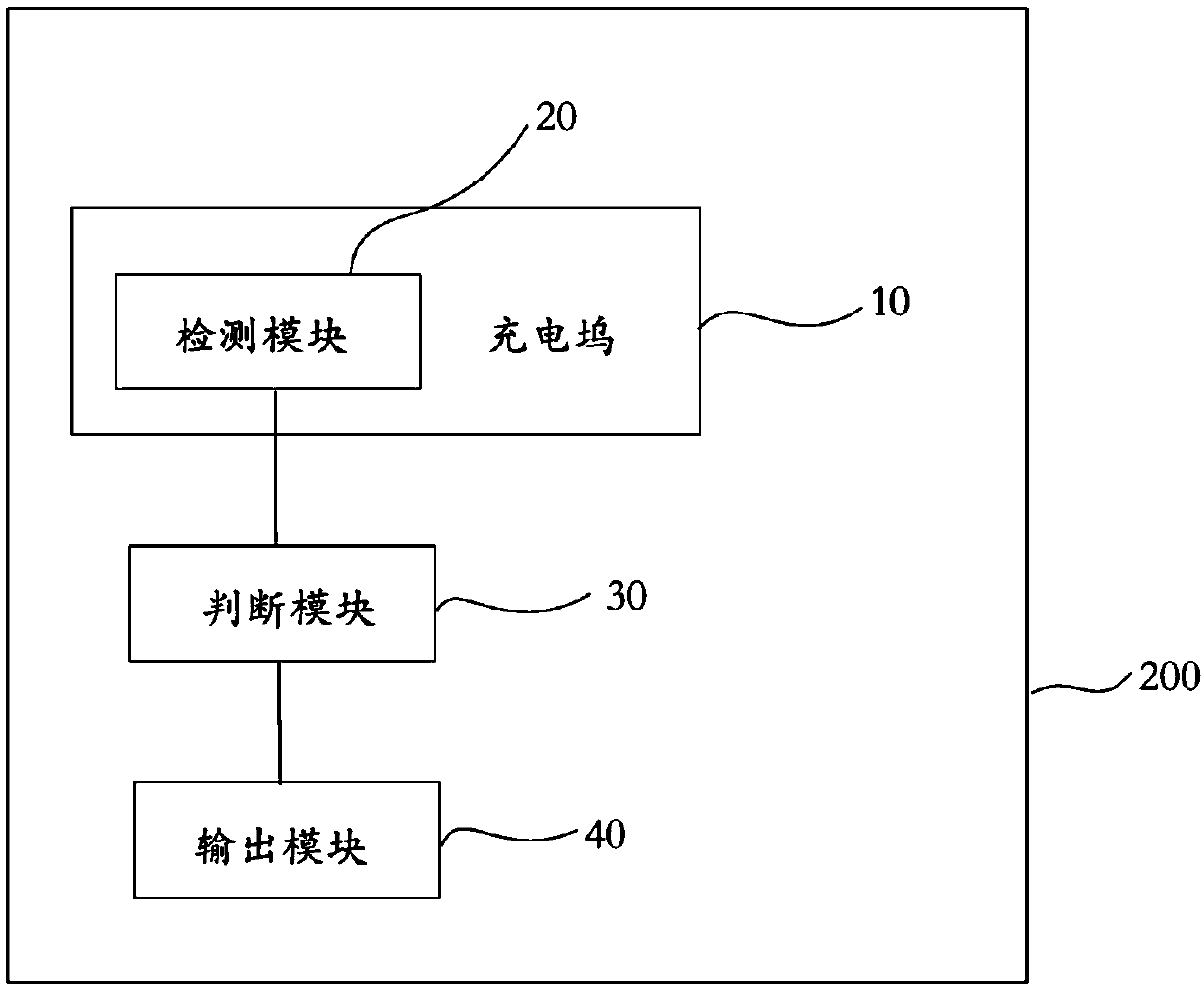

Self-inspecting method and self-inspecting system for robot and computer storage medium

The invention provides a self-inspecting method and a self-inspecting system for a robot and a computer storage medium. The self-inspecting method comprises the following steps: determining devices for self-inspecting the robot; determining inspecting elements and detecting methods for inspecting treatment according to the type of the devices for self-inspecting the robot; setting the normal datarange of the devices according to the inspecting element for inspecting treatment; and treating and outputting the states of all the devices. According to the self-inspecting method for the robot provided by the embodiment, the problem that in the self-inspecting process, a robot communication device is not in a closed-loop state is solved, inspecting of executing devices is increased, barriers are added for maintaining and operating the robot, and major accidents caused by device exception in the operation process is avoided; and meanwhile, since the overall process is finished automatically,a status report is generated in case of exception, and the labor cost is reduced.

Owner:广州高新兴机器人有限公司

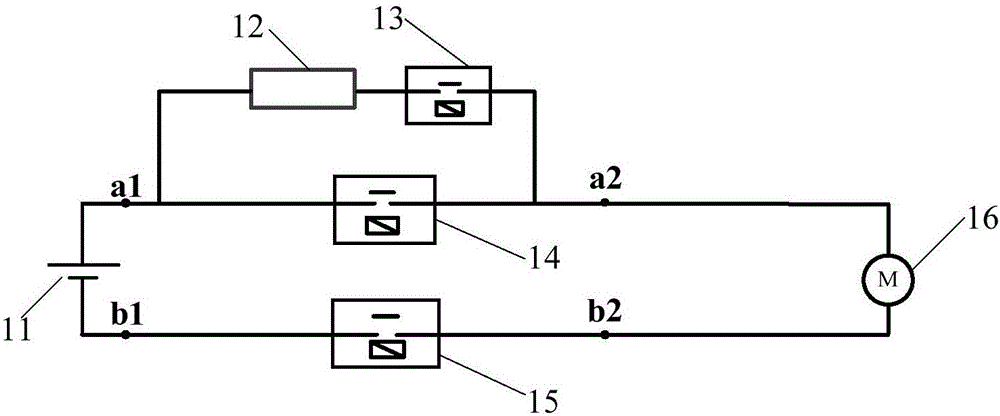

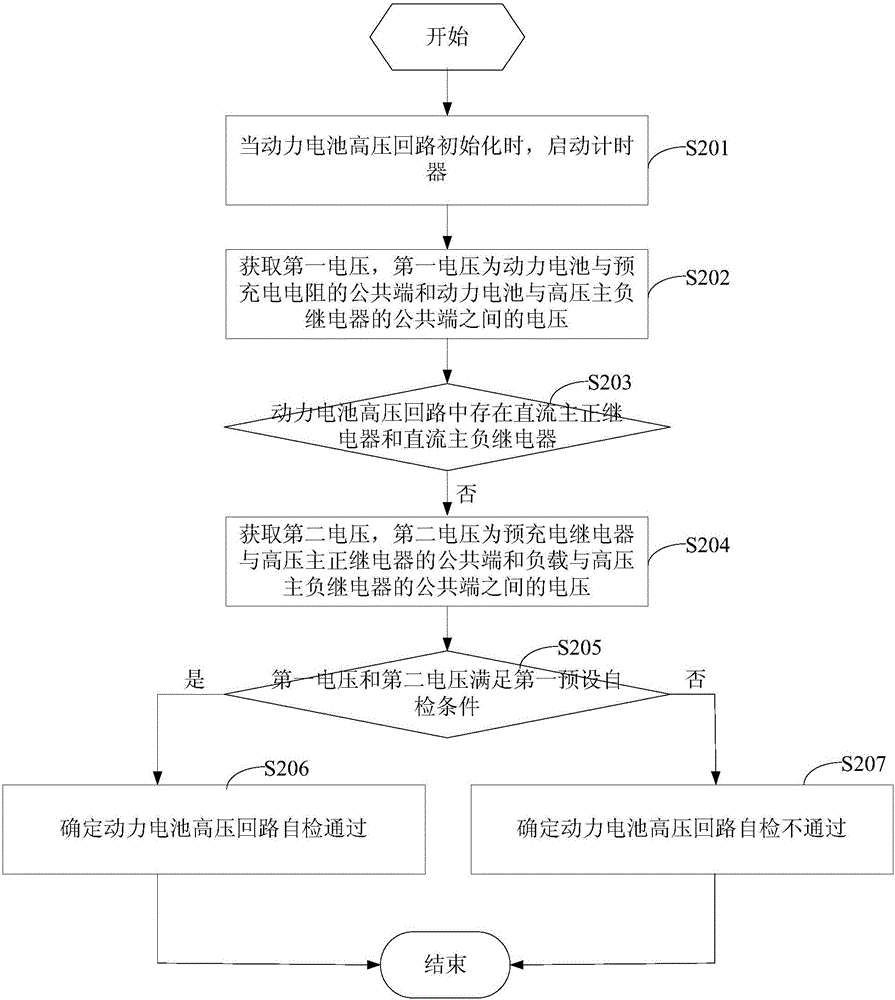

Self-check method, device and system of high-voltage loop of power battery

ActiveCN106019163AImplement self-testAvoid failureElectrical testingVehicular energy storagePower batteryElectrical battery

The invention provides a self-check method, device and method of a high-voltage loop of a power battery. When the high-voltage loop of the power battery is initialized, a timer is started; a first voltage, which is the voltage between the common end of the power battery and a pre-charged resistor and the common end of the power battery and a high-voltage main negative relay, is obtained; when a DC main positive relay and a DC main negative relay do not exist in the high-voltage loop of the power battery, a second voltage, which is the voltage between the common end of a pre-charged relay and a high-voltage main positive relay and the common end of a load and the high-voltage main negative relay, is obtained; whether the first voltage and the second voltage satisfy a first preset self-check condition is determined; if YES, it is determined that the high-voltage loop of the power battery passes self-check; and if NO, it is determined that the high-voltage loop of the power battery fails in self-check. Self-check for the high-voltage loop of the power battery is realized, faults after closing of the high-voltage loop of the power battery are prevented, and the safety of whole automobile is further ensured.

Owner:CHONGQING CHANGAN AUTOMOBILE CO LTD

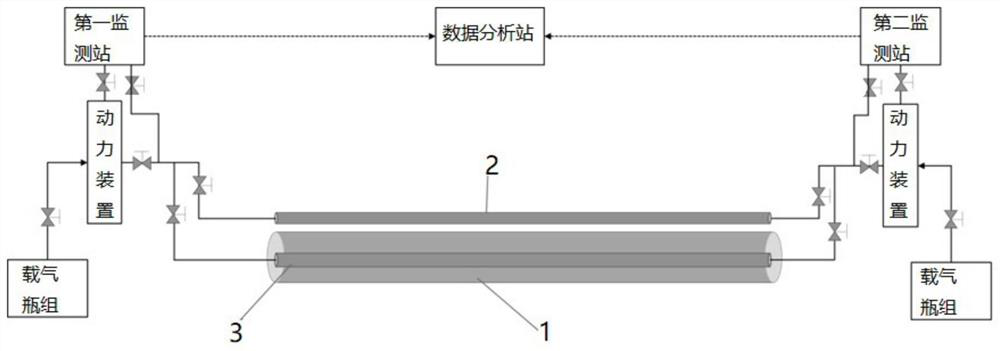

Hydrogen-containing natural gas pipeline leakage monitoring and positioning method and system

PendingCN113108244AHigh sensitivityAccurate positioningPipeline systemsProcess engineeringEngineering

The invention relates to a hydrogen-containing natural gas pipeline leakage monitoring and positioning method and system. The method comprises the following steps that at least two detection pipes are laid along a pipeline, and a leaked gas is entered to the detection pipes when the pipeline leaks; after a preset time interval, carrier gas is introduced into one of the detection pipes, leaked gas in the detection pipes enters a first monitoring station along with the carrier gas, the first monitoring station judges whether the concentration of the leaked gas exceeds a threshold value range or not, and a data analysis station calculates the leakage position in the pipeline; then, the carrier gas is introduced into the other detection pipe, the concentration of leaked gas in the carrier gas is judged through a second monitoring station, and the leakage position in the pipeline is calculated through the data analysis station; and the final leakage gas concentration and leakage position are obtained according to the leakage gas concentration and leakage position obtained for the first time and the second time. According to the hydrogen-containing natural gas pipeline leakage monitoring and positioning method, the problems in the prior art can be solved, and the requirements of high leakage monitoring sensitivity, high positioning accuracy, low missing report rate and low false alarm rate of the hydrogen-containing natural gas pipeline can be met.

Owner:CNOOC GAS & POWER GRP

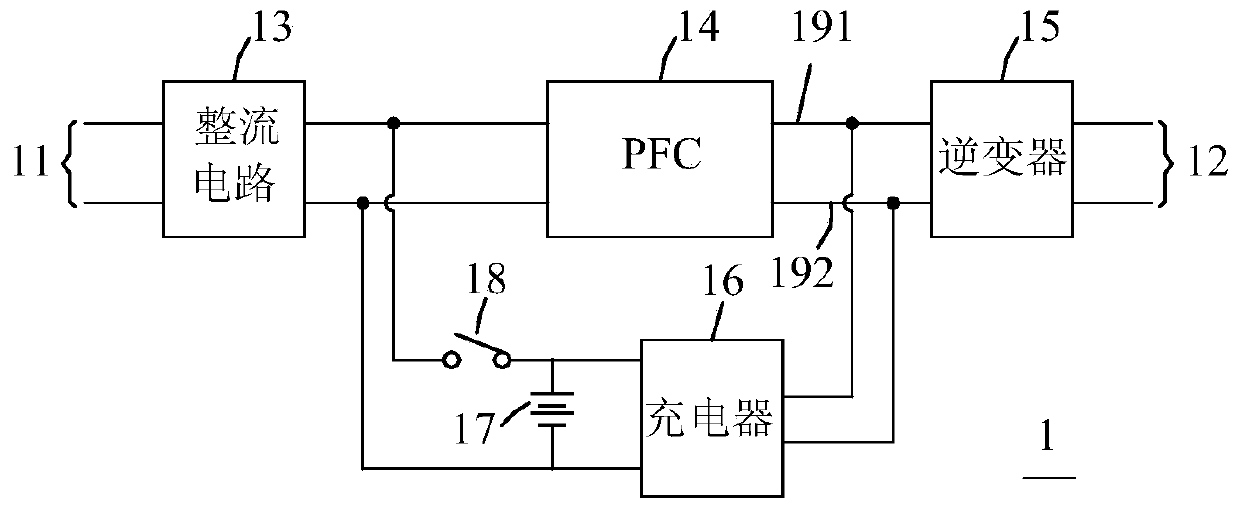

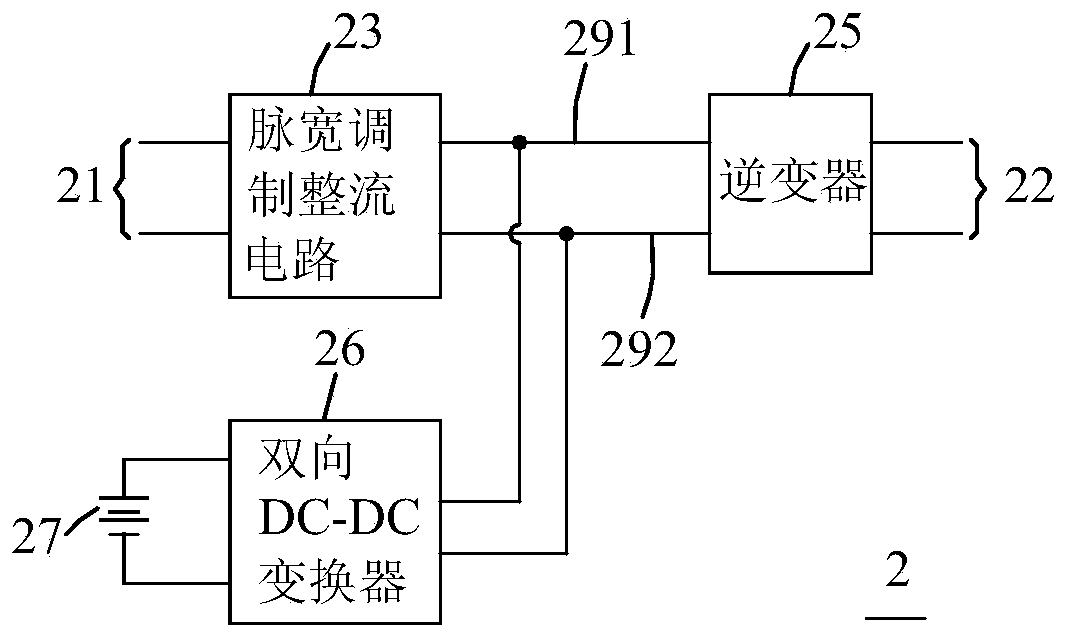

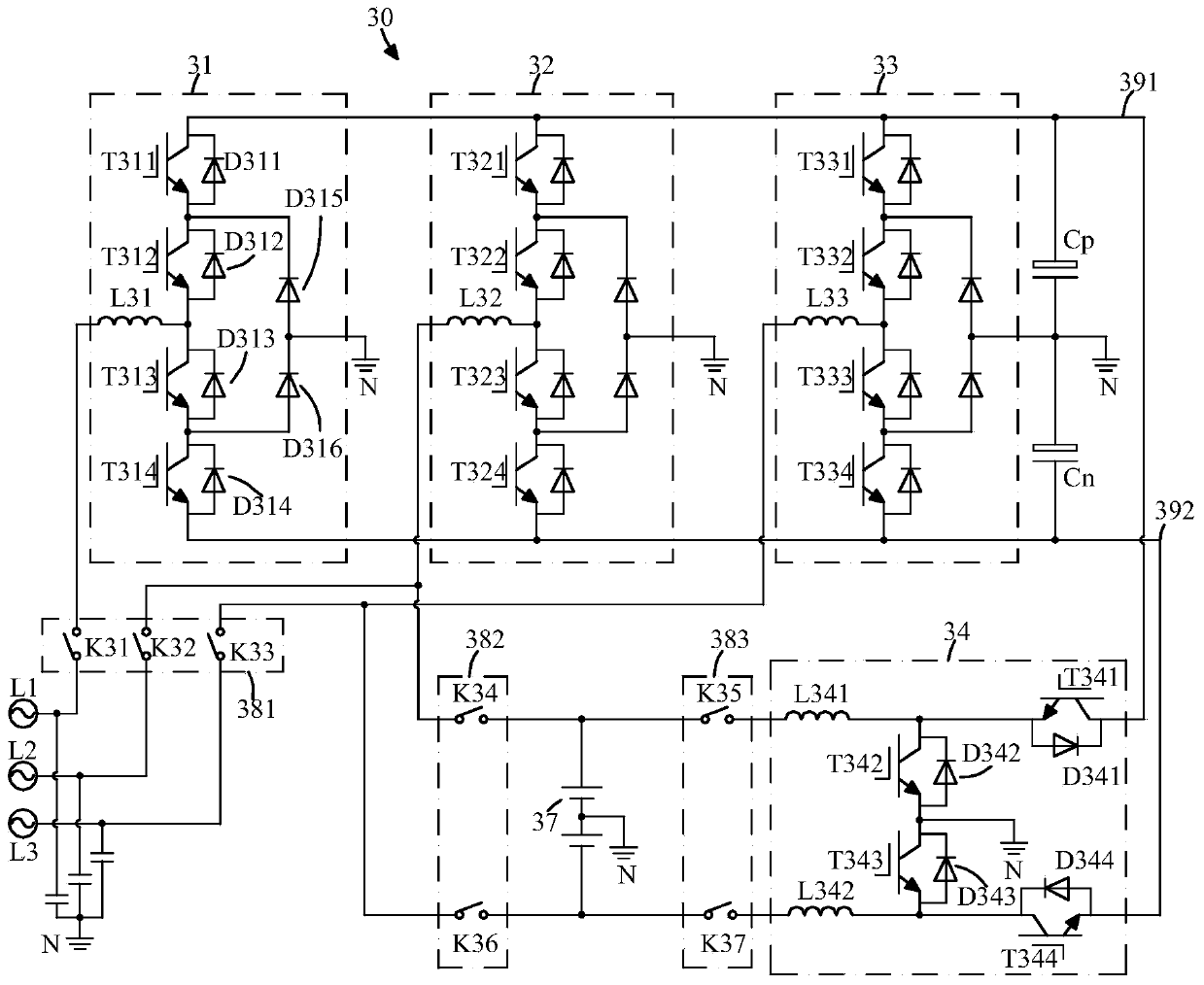

Multi-input power converter, control method thereof and uninterruptible power supply comprising multi-input power converter

ActiveCN111030458ALow costAchieving two-way flowBatteries circuit arrangementsAc-dc conversionCapacitanceControl engineering

The invention provides a multi-input power converter, a control method thereof and an uninterruptible power supply comprising the multi-input power converter. The multi-input power converter comprisesa first capacitor and a second capacitor which are connected in series between a positive direct current bus and a negative direct current bus, an I-type neutral-point clamping converter assembly, analternating current switch assembly and a first direct current switch assembly, wherein a node formed by connecting the first capacitor and the second capacitor is a neutral point; the I-type neutral-point clamping converter assembly comprises a first I-type neutral-point clamping converter and a second I-type neutral-point clamping converter which are connected in parallel between the positive direct current bus and the negative direct current bus; the alternating current switch assembly is connected between the input end of the I-type neutral-point clamping converter assembly and alternating current; and the first direct current switch assembly is used for switching on or switching off a rechargeable battery for selective power supply / charging and is connected between the input ends ofthe first I-type neutral-point clamping converter and the second I-type neutral-point clamping converter and the two ends of the rechargeable battery. According to the multi-input power converter, bidirectional flow of energy can be realized, power soft switching is realized, and the cost is low.

Owner:SANTAK ELECTRONICS SHENZHEN

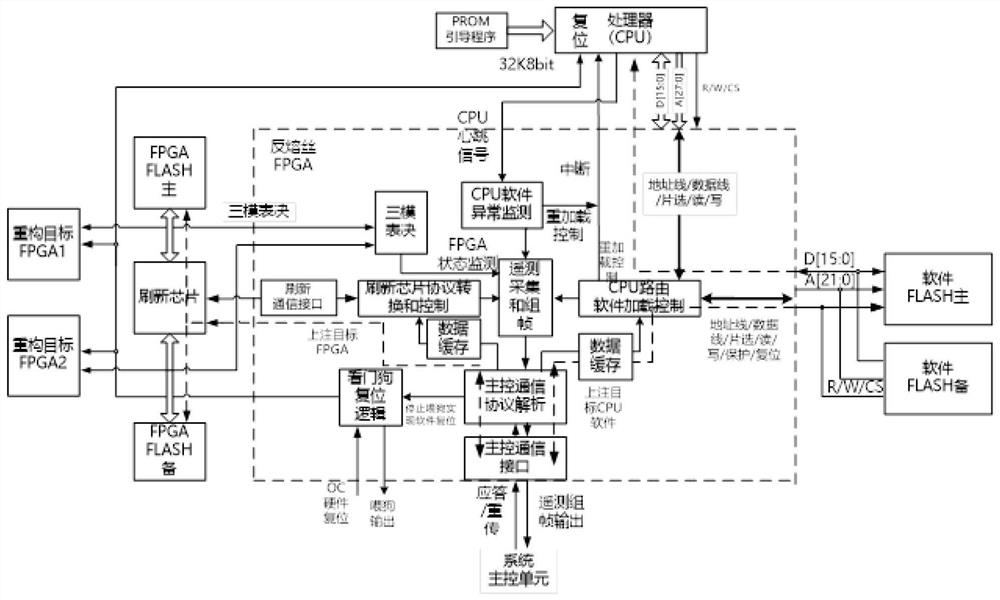

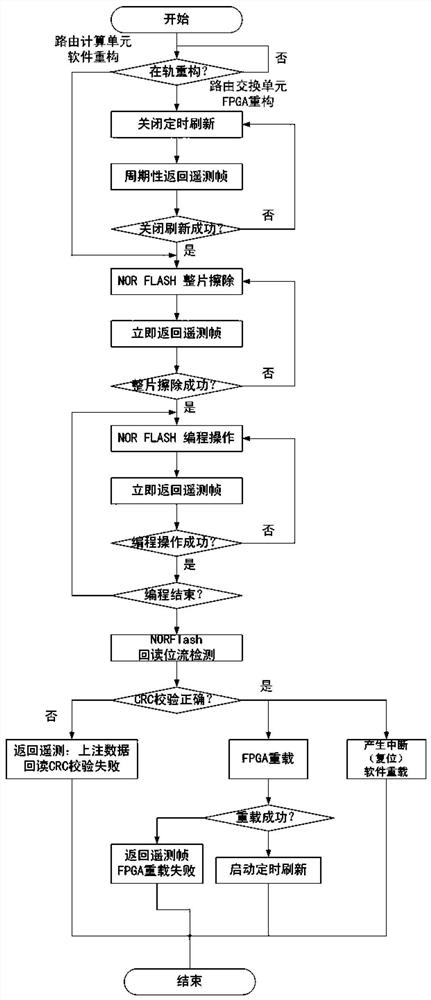

On-orbit reconstruction method and system for aerospace electronic system based on FPGA

PendingCN113312305AImprove autonomous health management and on-orbit maintenance capabilitiesImprove performance and reliabilityArchitecture with single central processing unitElectric digital data processingPhysicsSatellite

The invention discloses an on-orbit reconstruction method and system for an aerospace electronic system based on FPGA. The method is based on an FPGA technology and can realize software and FPGA on-orbit reconstruction functions of the aerospace electronic system. The method plays a key role in astronavigation electronic system on-orbit fault restoration, and relieving of the influence of the universe space single event effect (SEE) on astronavigation electronic equipment such as satellites. The autonomous health management and on-orbit maintenance capabilities of the aerospace electronic system are fundamentally improved. And on-orbit autonomous configuration, self-test, autonomous repair and maintenance can be realized. Therefore, the system performance and reliability are greatly improved.

Owner:XIAN MICROELECTRONICS TECH INST

![A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g] A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g]](https://images-eureka.patsnap.com/patent_img/dedeac0d-960d-4aa6-8e9e-8f3f64218890/HDA0001761676710000011.png)

![A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g] A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g]](https://images-eureka.patsnap.com/patent_img/dedeac0d-960d-4aa6-8e9e-8f3f64218890/HDA0001761676710000012.png)

![A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g] A large-power IGBT fault diagnosis and protection method and apparatus based on gate charges Q[g]](https://images-eureka.patsnap.com/patent_img/dedeac0d-960d-4aa6-8e9e-8f3f64218890/HDA0001761676710000021.png)