Design method of pulse compression linear limiter on basis of Field Programmable Gate Array (FPGA)

A design method and limiter technology, applied in the direction of limit amplitude change rate, electrical components, code conversion, etc., can solve the problems of destroying clutter phase, moving target processing, etc., achieve high practical value, and avoid the spread of signal spectrum Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

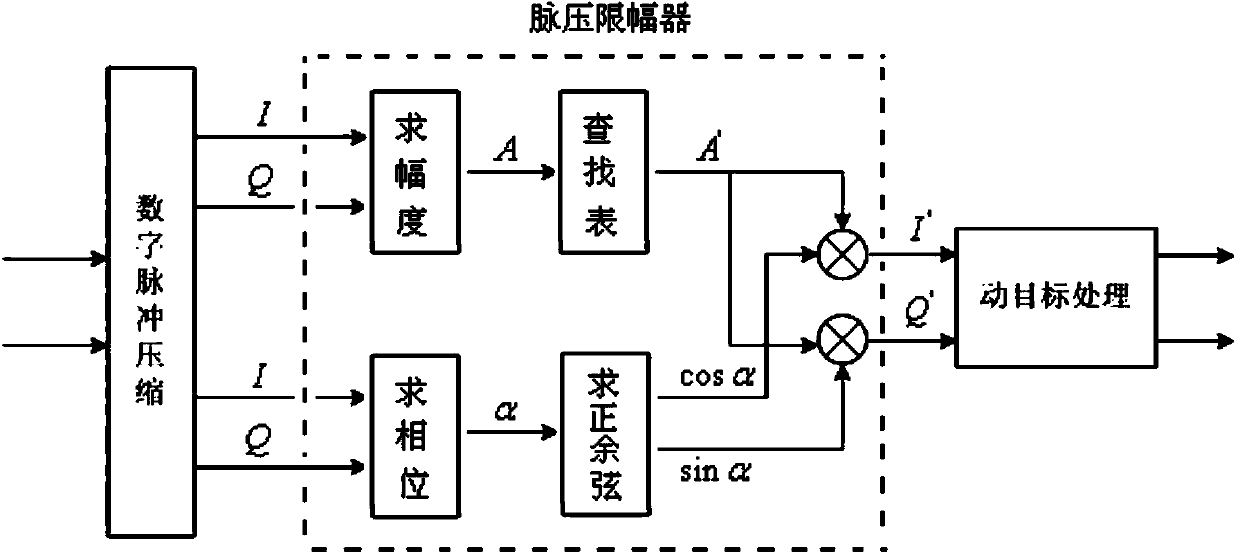

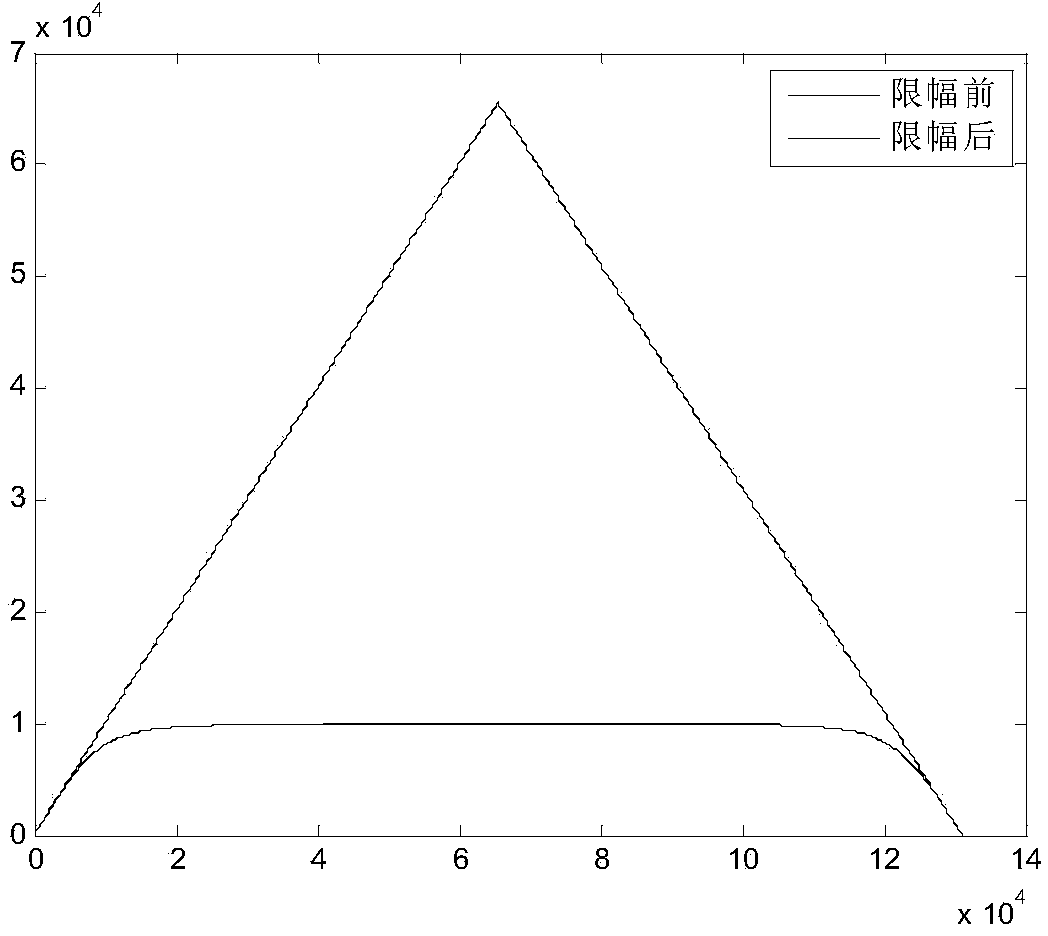

[0011] 1. After pulse compression I, Q Signal normalization processing. Normalization is done as follows:

[0012]

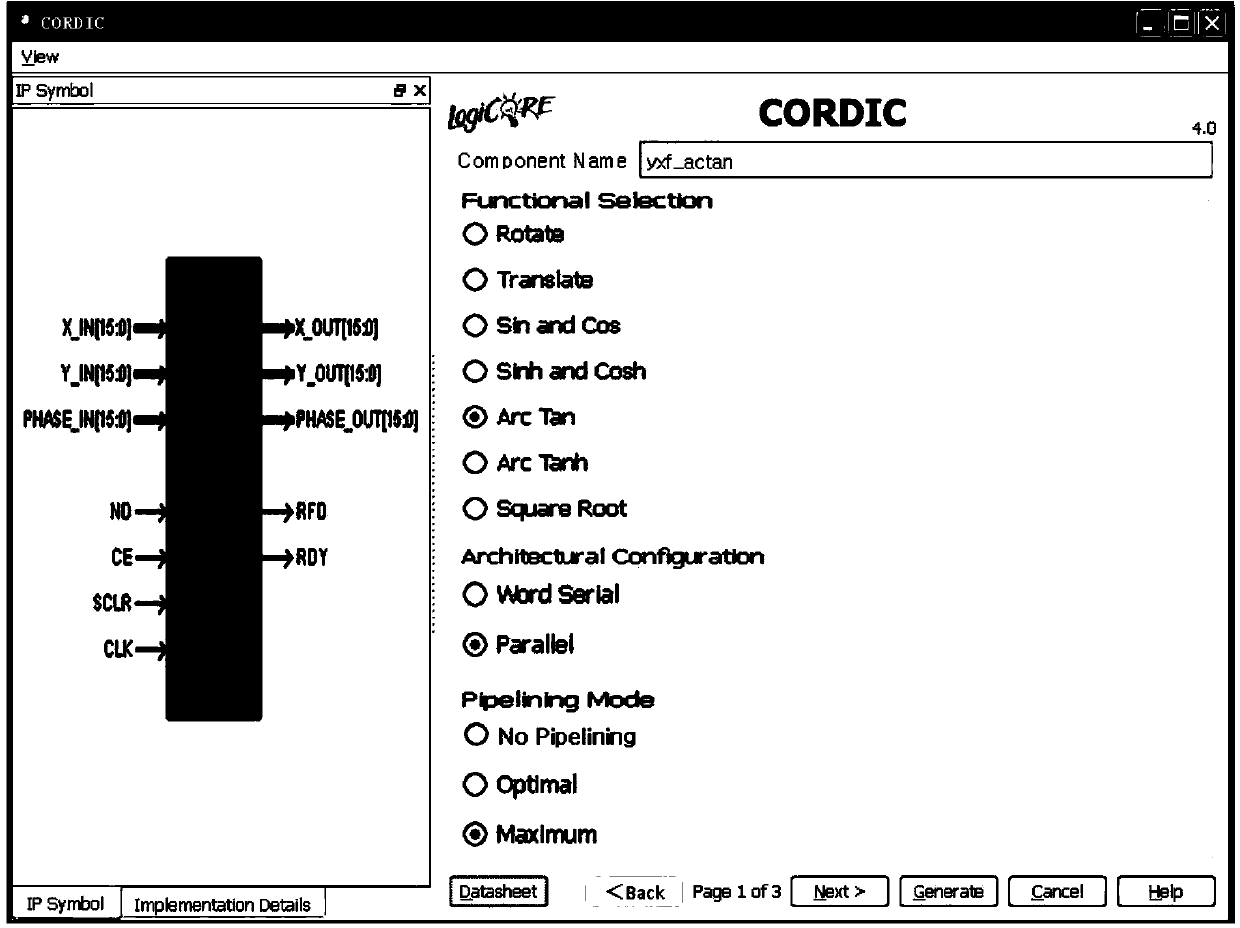

[0013] The normalization process in the FPGA is divided into two steps. The first step is to use the coordinate rotation digital calculation method (CORDIC) to obtain the phase of the pulse pressure signal. α . The CORDIC algorithm can recursively calculate commonly used function values through shifting and addition and subtraction operations, including the arctangent function tan -1 . The FPGA development platform ISE of XILINX provides a free CORDIC algorithm IP core, which can be set to find the arctangent function (such as figure 2 shown), and instantiated, the generated module realizes the I, Q A function of the signal phase. The second step is to obtain cos again through the CORDIC algorithm α and sin α , the CORDIC algorithm IP core can be set to calculate the sine function and cosine function at the same time, and the 90-degree phase differ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com