Schedule optimization method for communication energy consumption in on-chip network

An on-chip network and optimization method technology, applied in the field of on-chip network, can solve problems such as no optimization method, and achieve the effects of reducing communication distance, energy consumption, and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

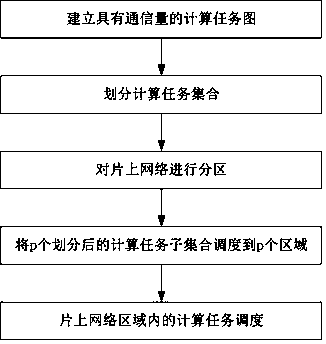

[0046] A scheduling optimization method for communication energy consumption in a network on chip. The steps of the scheduling optimization method are as follows figure 1 Shown:

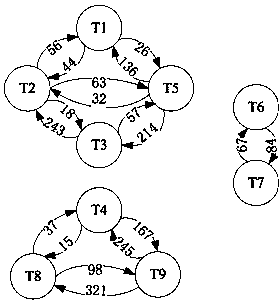

[0047] Step 1. Establish a computing task graph with communication traffic

[0048] Obtain the real-time traffic of the computing task when it is running, and establish a computing task graph with the traffic. When the computing task is running, the communication between multiple computing tasks can be obtained through the real-time software monitoring tool, and the specific communication volume can be recorded. According to the communication volume between computing tasks, a computing task graph is established. For example, for the nine computing tasks T1, T2, ..., T9, the traffic is shown in Table 1.

[0049] Table 1 Communication traffic of computing tasks

[0050] T1 T2 T3 T4 T5 T6 T7 T8 T9 T1 - 44 63 0 26 0 0 0 0 T2 56 - 18 0 0 0 0 0 0...

Embodiment 2

[0087]A scheduling optimization method for communication energy consumption in a network on chip. Except step 3 and step 5, all the other are the same as embodiment 1.

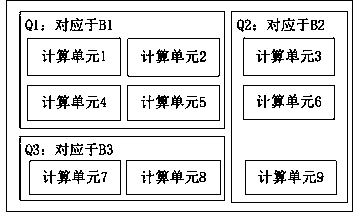

[0088] Step 3. Partition the network on chip

[0089] The specific steps of dividing the on-chip network into p areas according to the p divided computing task sets B:

[0090] Step 3.1. If the number of computing tasks M ≤ the number U of computing units of the network on chip, it should satisfy:

[0091] Area Qj corresponds to the divided computing task set Bj;

[0092] The number of computing units in the area Qj ≥ the number of computing tasks in the divided computing task set Bj;

[0093] Step 3.2. If the number of computing tasks M>the number of computing units U of the network on chip, the method of dividing the network on chip into p areas is as follows:

[0094] i) Select the divided computing task set Bj that contains the largest number of computing tasks from the p divided computing task sets B,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More