FPGA global clock detection technique for manned spacecraft

A manned spacecraft and global clock technology, applied in frequency measurement devices and other directions, can solve the problem of inability to detect the validity of the global clock, and achieve the effects of rapid fault response, accurate detection and simple circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

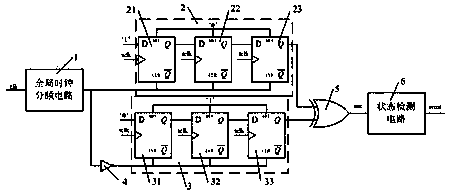

[0017] see figure 1 and figure 2 , the manned spacecraft FPGA global clock detection technology of the present invention is a detection circuit, and the detection circuit includes a global clock frequency division circuit 1, a first synchronization circuit 2, a second synchronization circuit 3, a NOT gate 4 and two input The XOR gate 5 at the end, wherein, the global clock frequency division circuit 1 divides the frequency of the global clock to generate a frequency-divided clock signal. In practical applications, the frequency of the global clock clk is much higher than the frequency of the detection clock tclk. The global clock frequency dividing circuit 1 can divide the global clock into the range of the detection clock tclk, and based on the concept of the present invention, the clock period of the frequency-divided clock signal is at least three times less than the clock period of the detection clock.

[0018] read on figure 1 , the input end of the first synchronizati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More