Wafer Alignment Method for Image Sensor Wafer-Level Test

An image sensor, wafer-level technology, used in semiconductor/solid-state device testing/measurement, electrical components, circuits, etc. Accuracy, difficulty in meeting the alignment accuracy requirements of CMOS image sensors, etc., to achieve the effect of improving accuracy and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, the present invention can be implemented in many other ways different from those described here, and those skilled in the art can make similar extensions without violating the connotation of the present invention, so the present invention is not limited by the specific embodiments disclosed below.

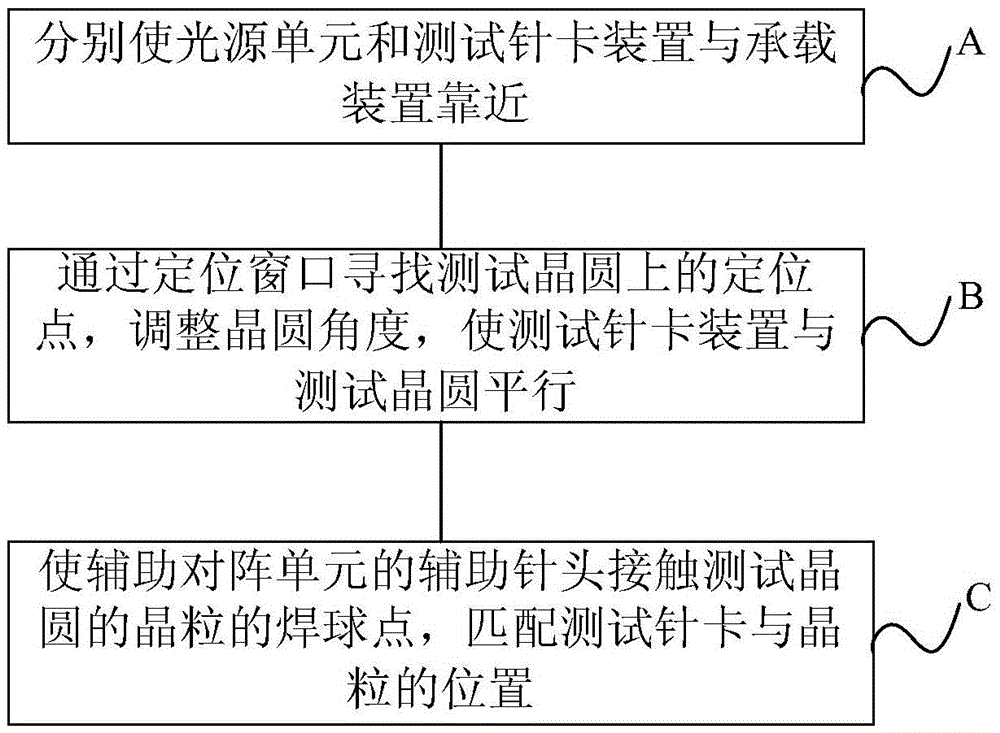

[0028] The invention provides a wafer alignment method suitable for wafer-level testing of an image sensor, which can provide higher alignment accuracy and has low implementation complexity.

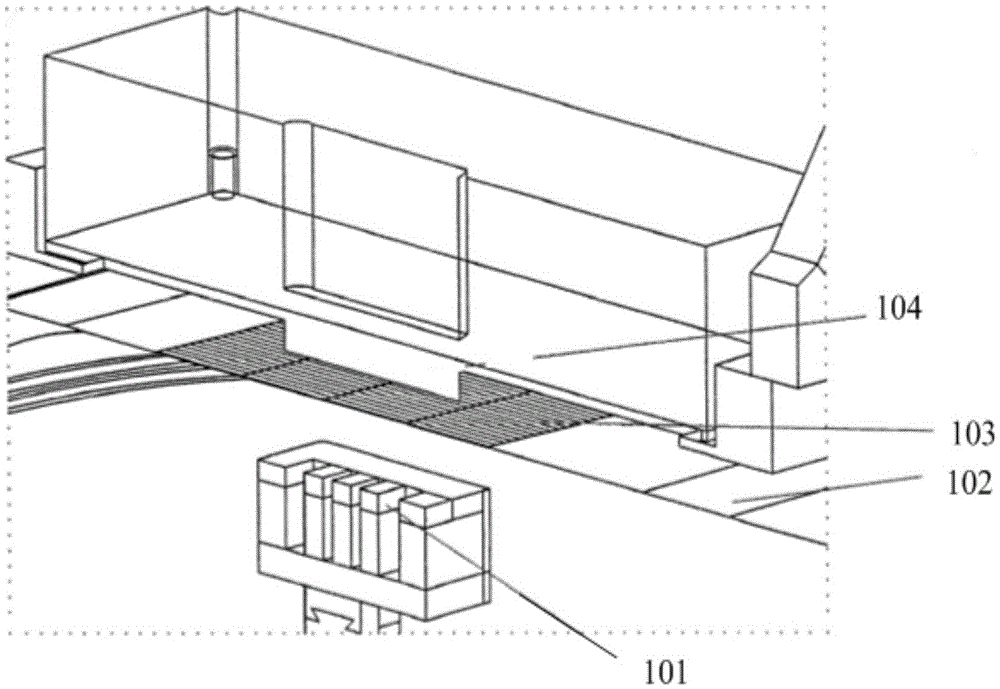

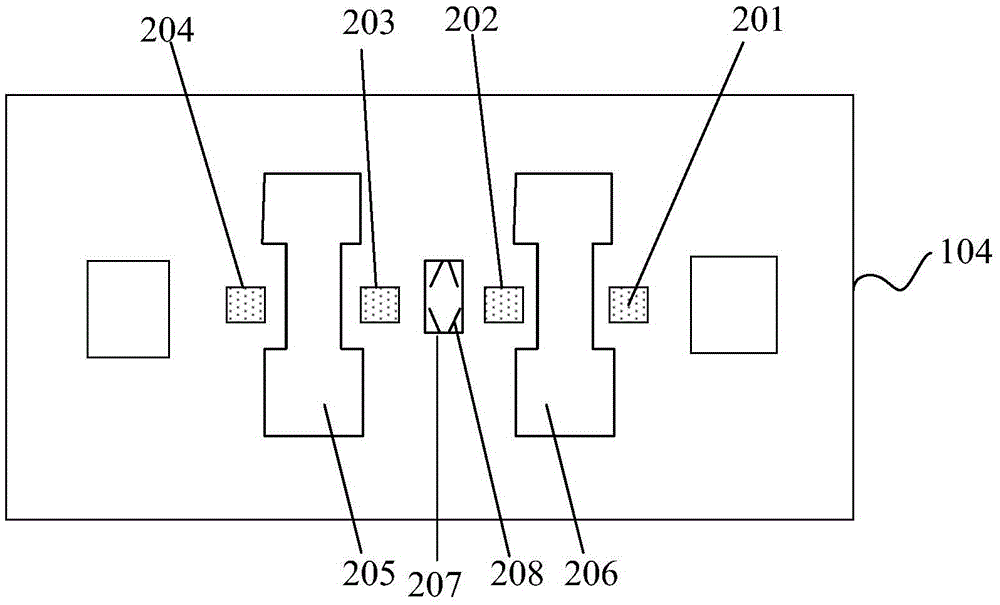

[0029] The alignment method first provides an image sensor wafer-level test device, the test device includes: a light source unit, a test needle card device located on the upper part of the light source unit, and a test wafer carried on a carrier device, the test The photosensitive surface of the wafer is arranged towards the carrying dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More