Transistor model capable of describing high temperature and low temperature mismatching characteristics and simulation method

A high and low temperature mismatch and transistor technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of different mismatch errors and the inability of common mismatch models to reflect mismatch characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

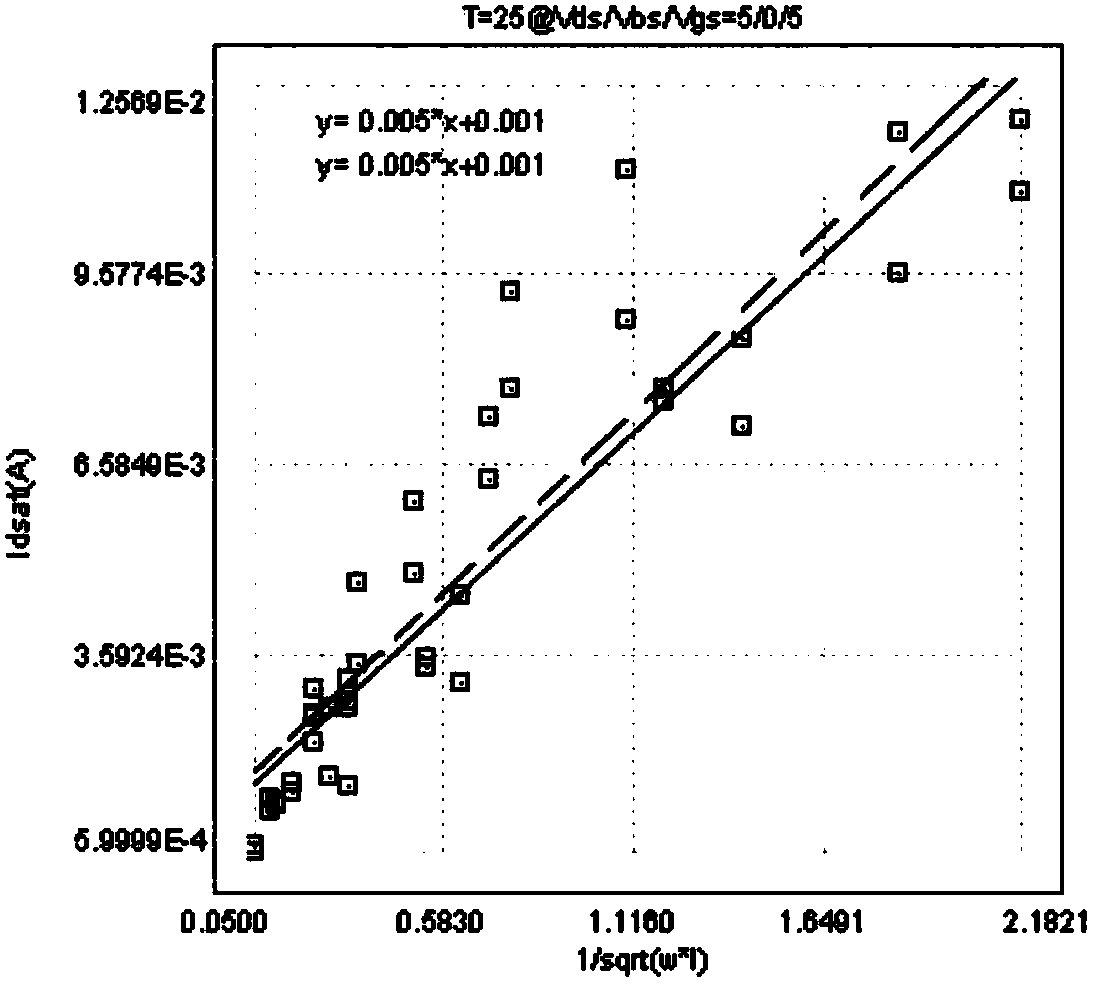

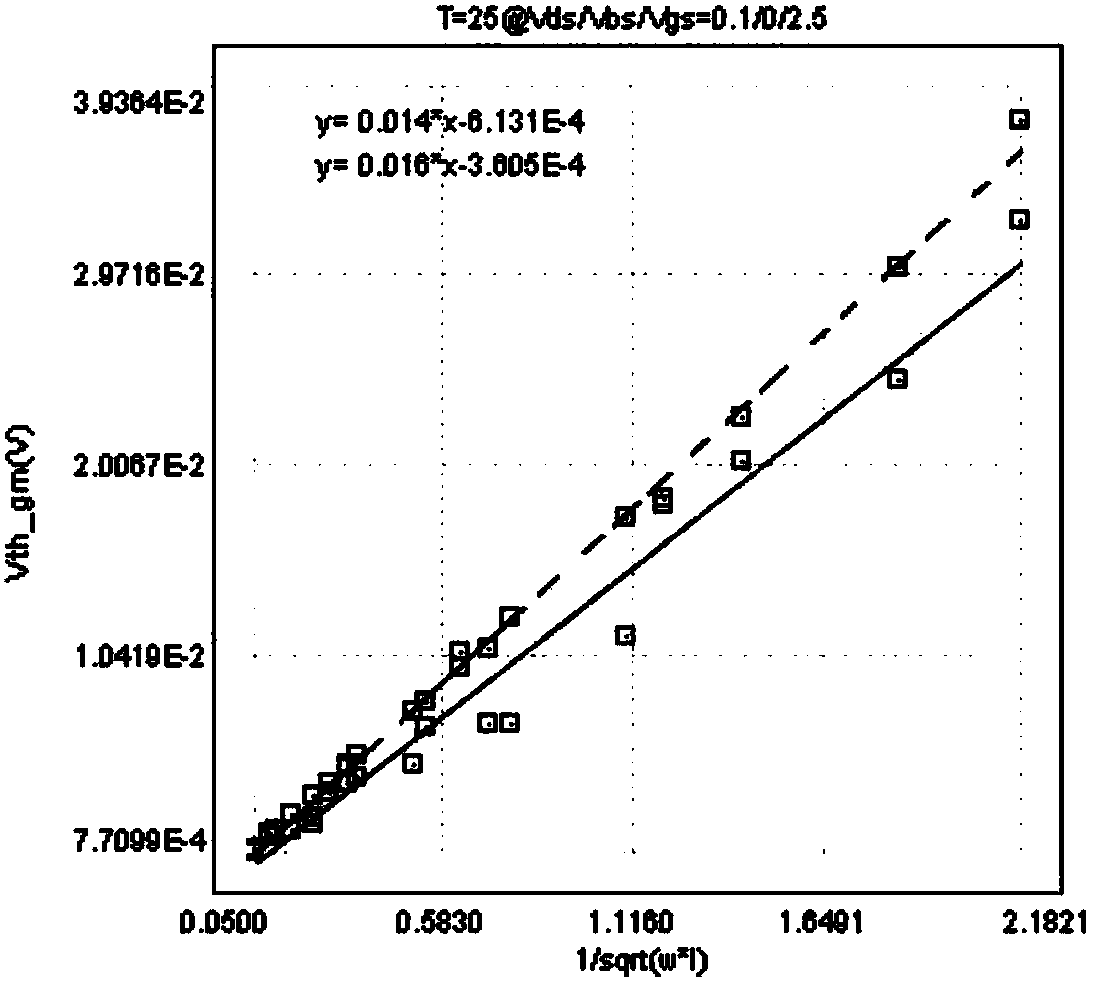

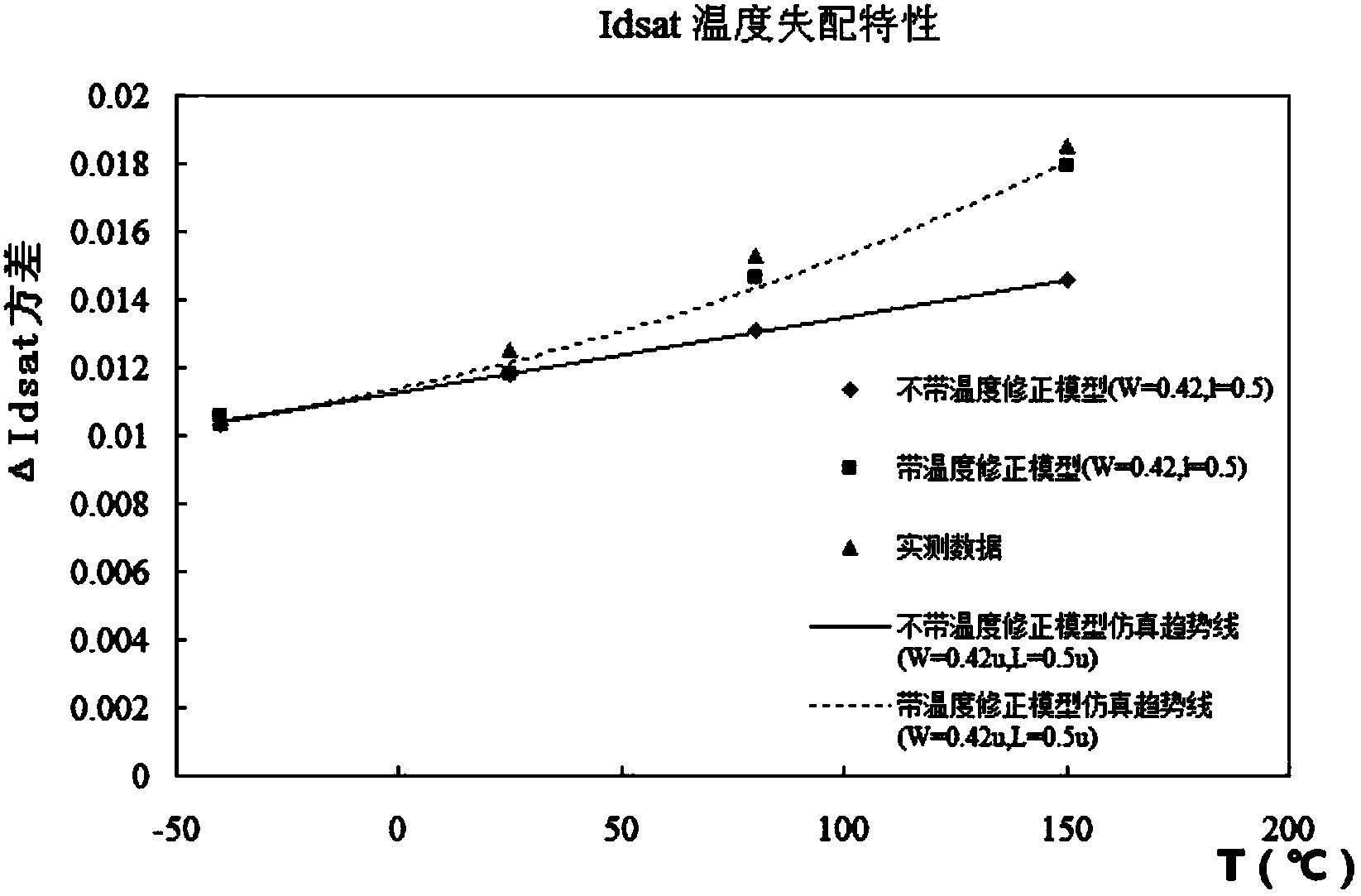

[0045] The transistor model described in the present invention that can describe the high and low temperature mismatch characteristics is to add the normal temperature mismatch correction formula to the two parameter values of Vth0 and u0 in the BSIM3 model parameters, which are respectively:

[0046] ΔVth 0 = avth 0 WL * agauss ( 0,1,1 ) - - - ( 1 ) ;

[0047] Δ u 0 = 1 + au 0 WL * agauss ( 0,1,1 ) - - - ( 2 ) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More