FPGA automatic logic loading device and method

An automatic loading and logic technology, applied in the direction of program control device, program loading/starting, etc., can solve the problems of high cost and poor reliability of loading logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0016] Device embodiment of the present invention:

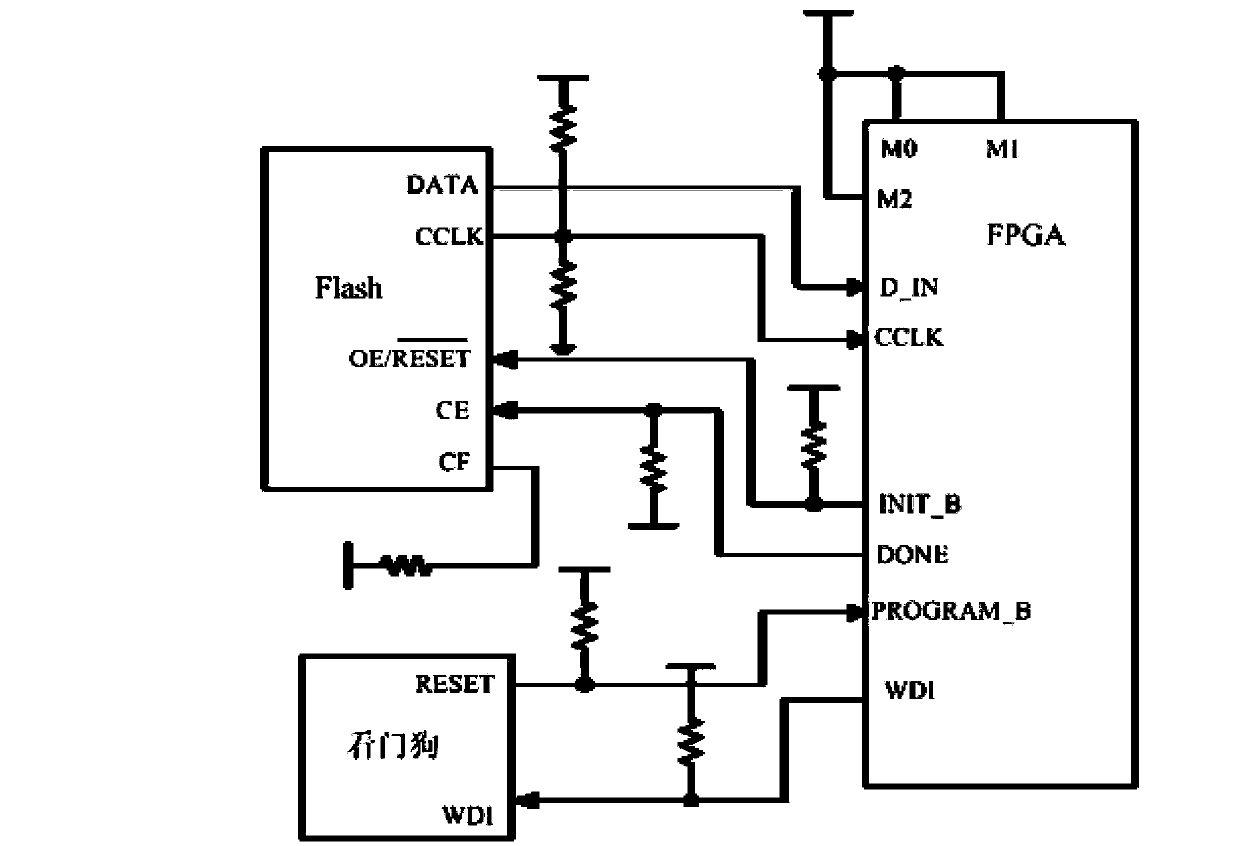

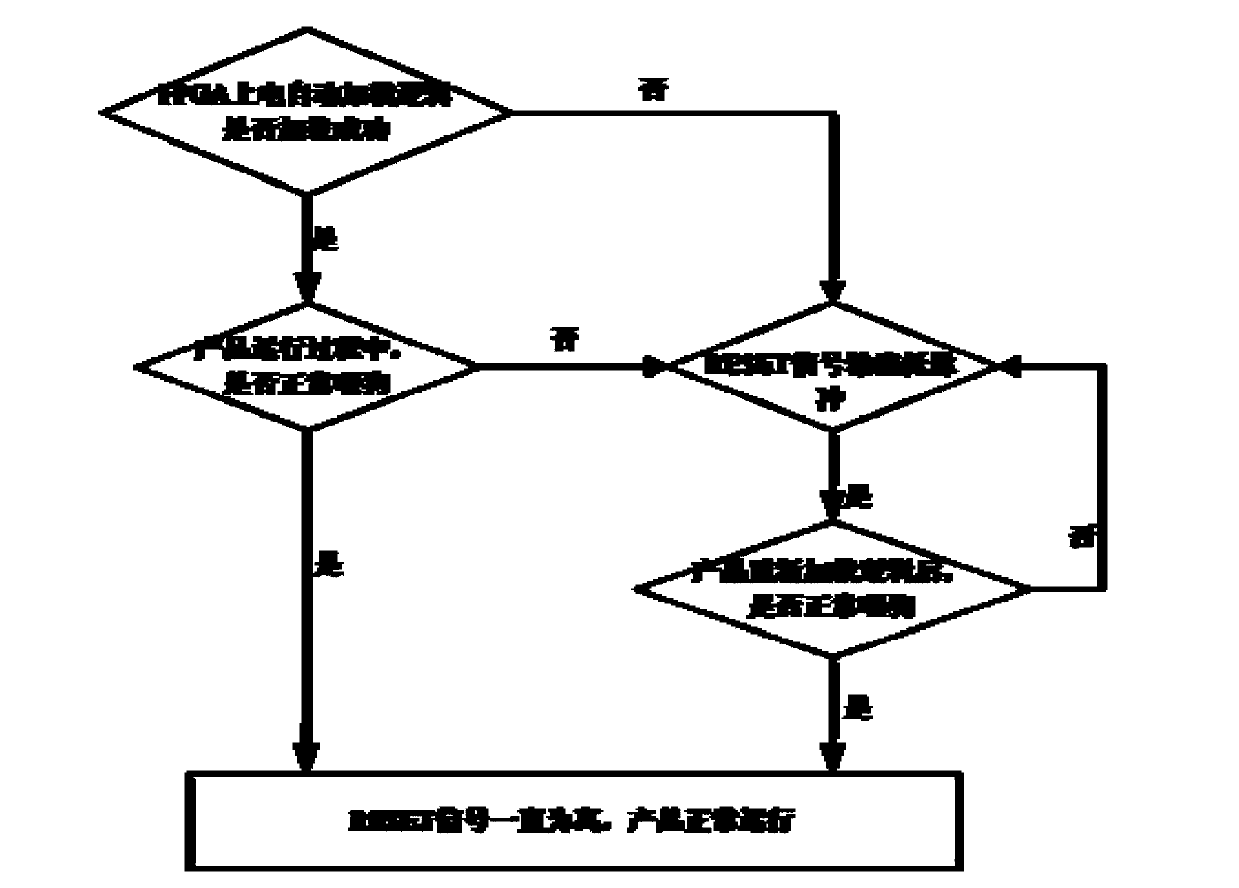

[0017] figure 1 Schematic diagram of the device for automatically loading logic for FPGA. The FPGA automatic loading logic device includes an FPGA chip and a FLASH memory that are connected correspondingly through signal lines, and also includes a watchdog chip. The reset output signal RESET terminal of the watchdog chip is connected to the start loading signal PROGRAM_B terminal of the FPGA chip. The dog feeding signal WDI end of the dog chip is connected to the corresponding WDI signal end of the FPGA chip.

[0018] In this example, the FPGA is configured as Slave Serial, assuming that the FPGA loading mode is slave serial, and the CF signal is not used. The selection of the watchdog chip must satisfy that its timeout time is less than the sum of the time required for the FPGA to load the logic and fee...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More