Hardware implementation method and system for algorithm

A hardware implementation and algorithm technology, applied in software testing/debugging, etc., can solve problems such as large hardware scale, limited optimization effect, and algorithm not having hardware feasibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

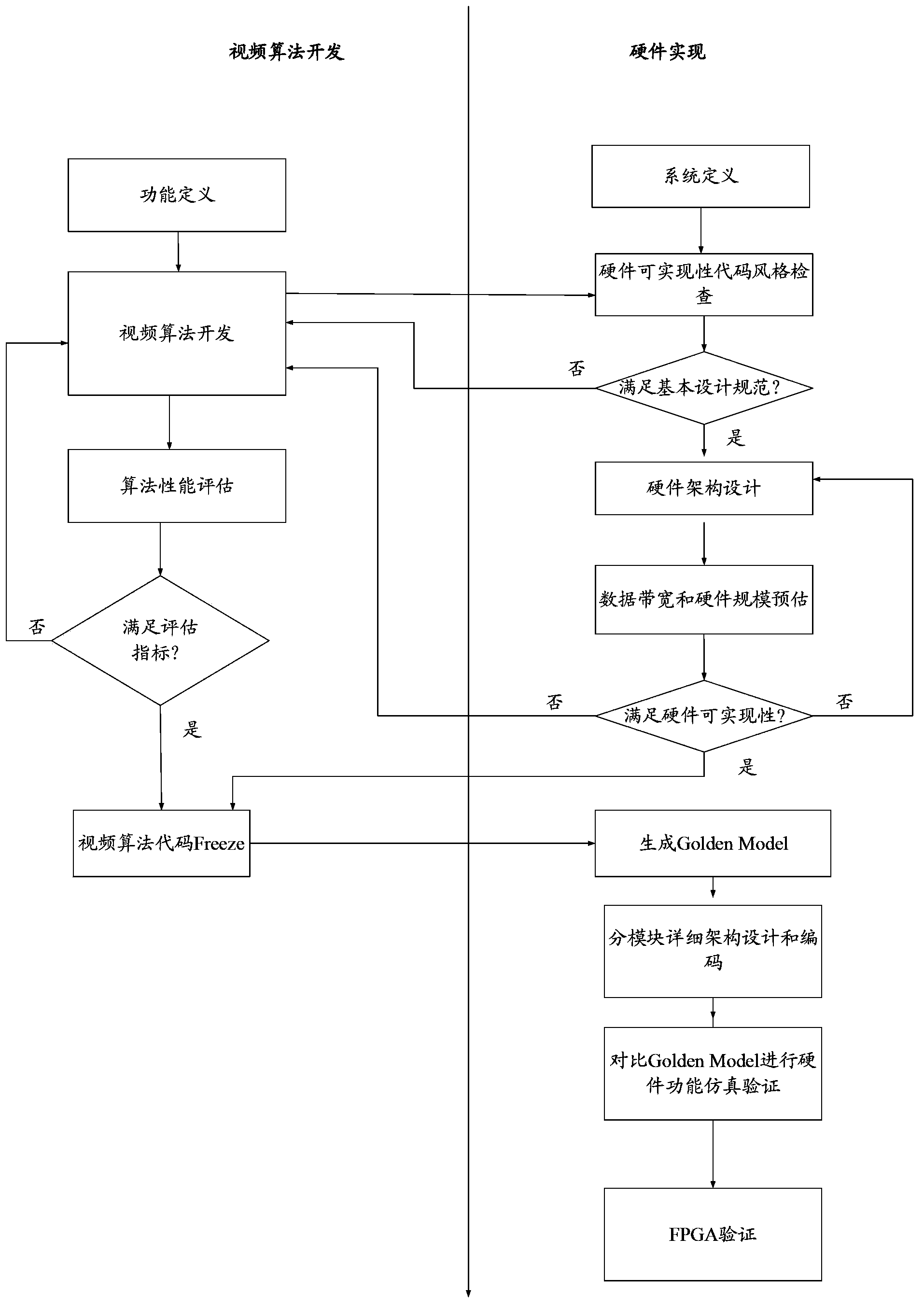

[0054]The algorithm hardware implementation method of the present application, an embodiment thereof, comprises the following steps:

[0055] Step A: Algorithm development.

[0056] Algorithm development includes: defining the function and performance index of the algorithm; developing and coding the algorithm according to the function definition and performance index definition.

[0057] Step B: Evaluate the hardware implementation of the algorithm.

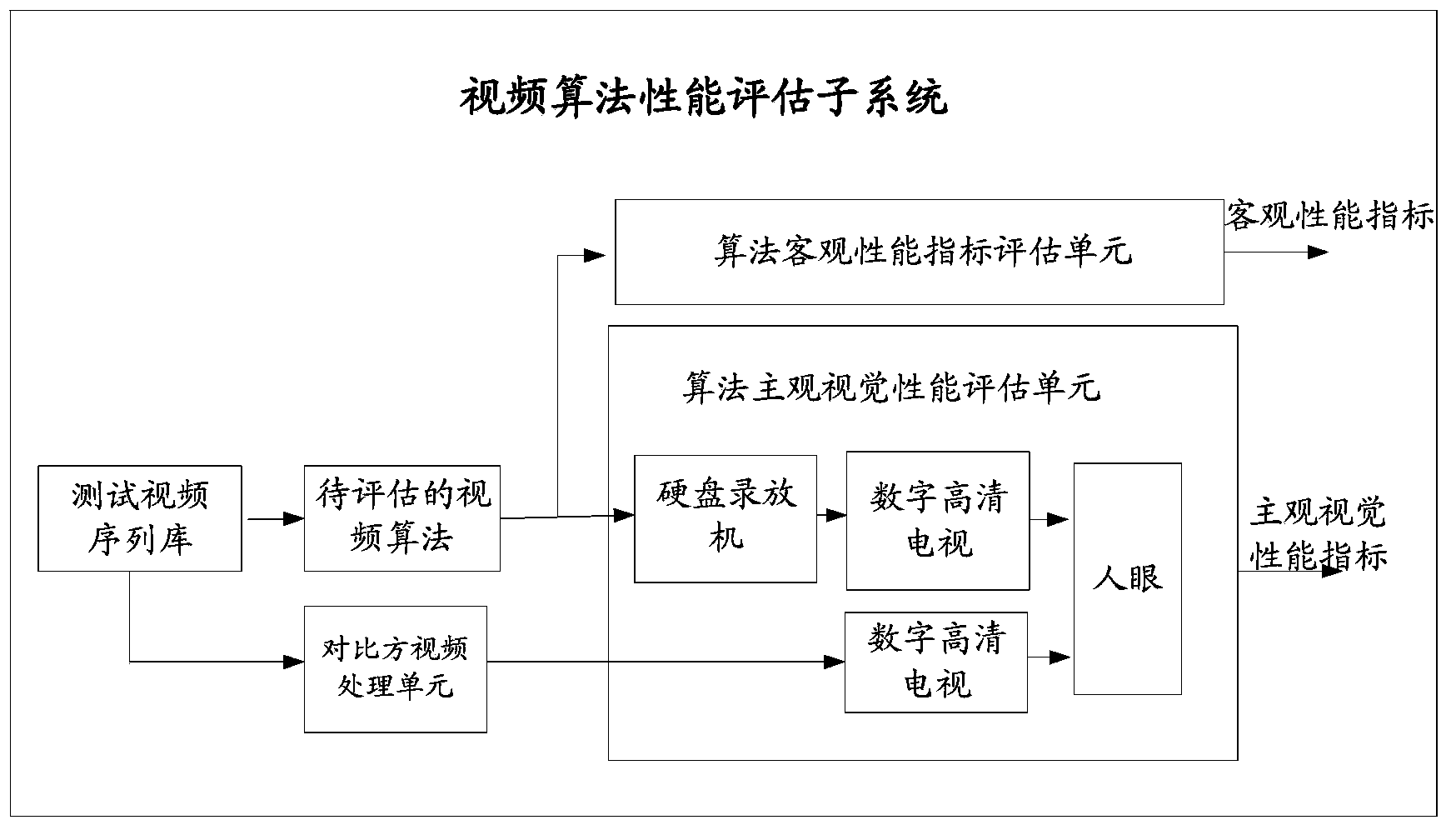

[0058] The algorithm includes a video algorithm, and the performance evaluation of the algorithm includes: the video algorithm reads the video from the test video sequence library to obtain the processed video; the video processed by the video algorithm is respectively input to the subjective visual evaluation unit and the objective performance index Evaluation unit; the objective performance index evaluation unit calculates the objective performance index of the algorithm processing result to be evaluated; after the subjective...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More