Hardware on-chip storage method applicable to infra-frame prediction reference pixels in HEVC (high efficiency video coding) standard

A technology of reference pixel and intra-frame prediction, applied in the field of digital video, can solve the problems affecting resource occupation and coding efficiency, and achieve the effect of easy reading, speeding up reading, and reducing difficulty of reading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

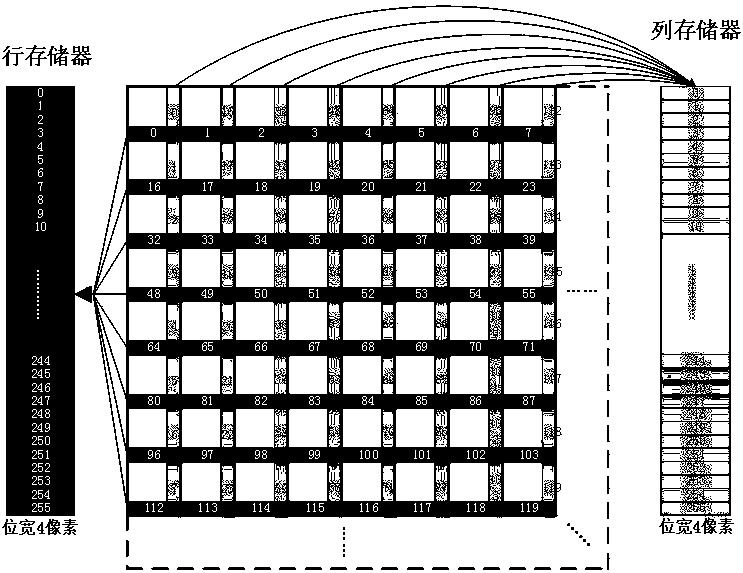

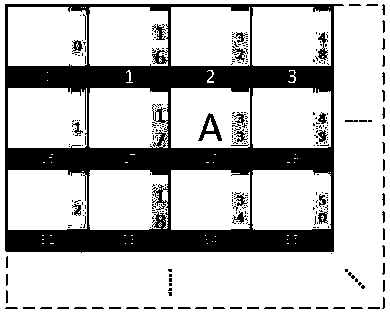

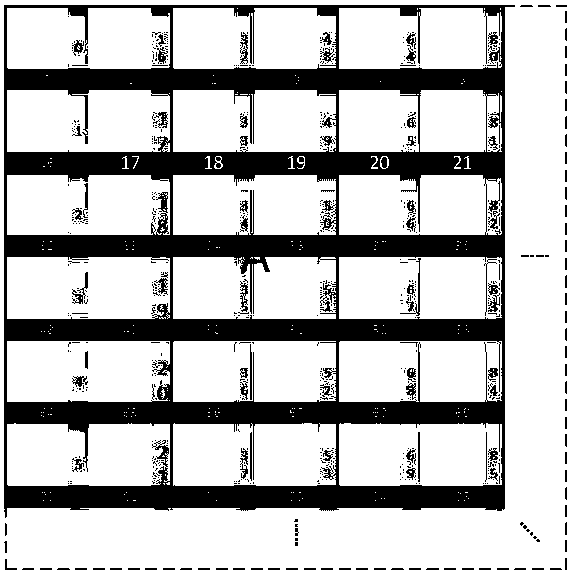

[0027] The method of the present invention will be further specifically described below by way of examples and in conjunction with the accompanying drawings.

[0028] as for Figure 4 , for the 4×4 block marked A, its abscissa x- rd is 2, the ordinate y rd is 1. Then, according to the formula (1), the first address of the reference pixel to be read in the line memory is obtained Row_Addr rd is 1, and the remaining addresses are 2 and 3; according to the formula (2), the first address of the reference pixel to be read in the line memory is obtained Col_Addr rd is 16, and the remaining addresses are 17 and 18.

[0029] Another example is right Figure 5 , for the 8×8 block marked A, the abscissa of the 4×4 block in the upper left corner x- rd is 2, the ordinate y rd for 2. Then according to the formula (1), the first address of the required reference pixel in the line memory is obtained Row_Addr rd is 17, and the remaining addresses are 18, 19, 20, 21; accordi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More