semiconductor structure

A semiconductor and carrier technology, applied in the field of semiconductor structures with anti-stress regions, can solve the problems of reducing the yield of semiconductor structures by 200%, lack of general products, inconvenience, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the semiconductor structure proposed according to the present invention, its specific implementation, structure, characteristics and effects, are as follows in conjunction with the accompanying drawings and preferred embodiments. Details are as follows.

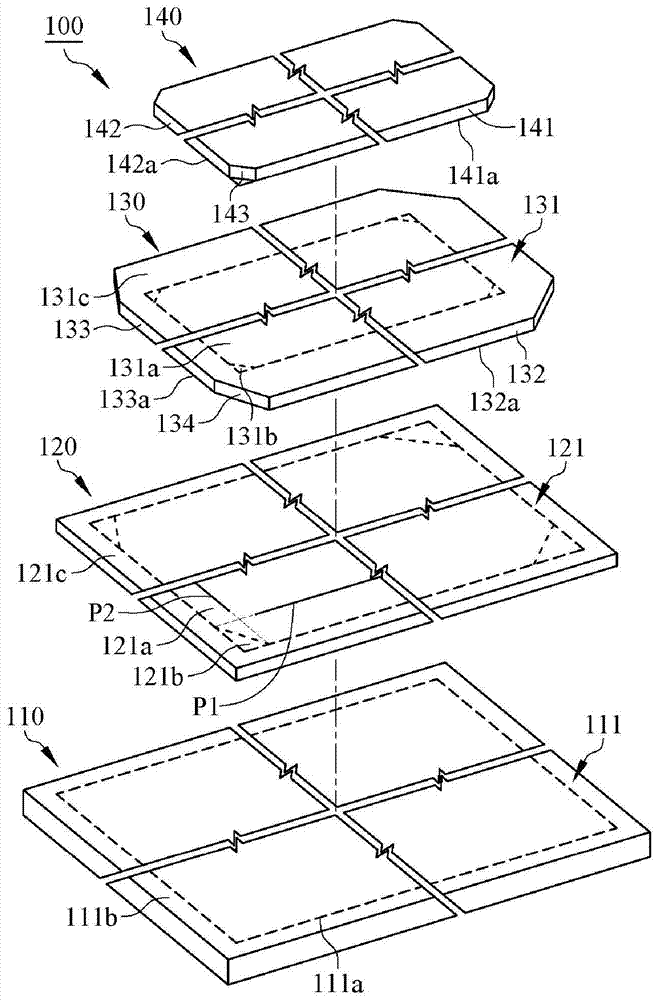

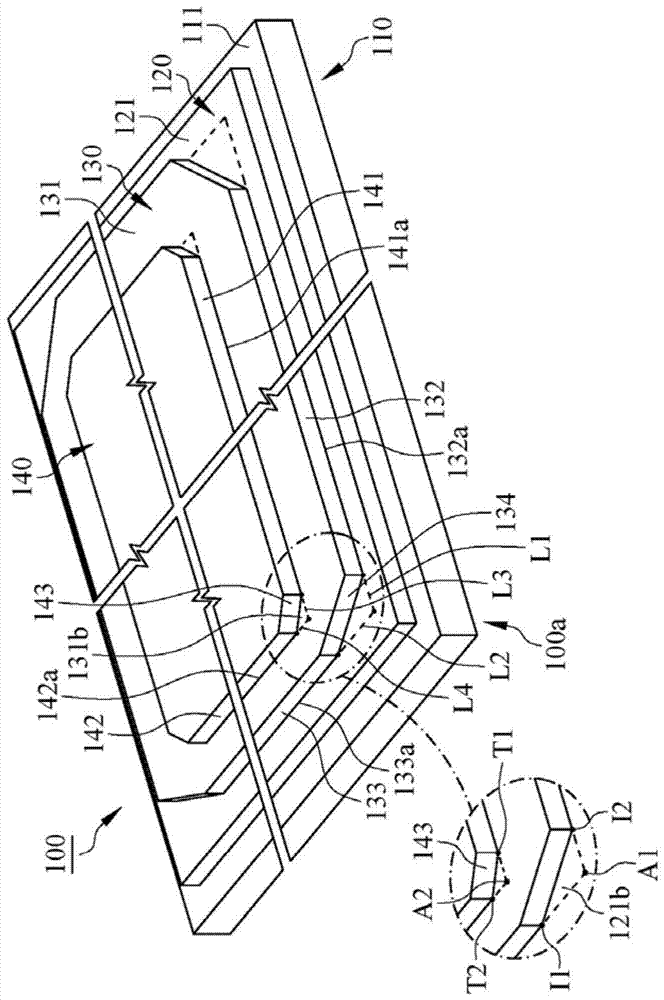

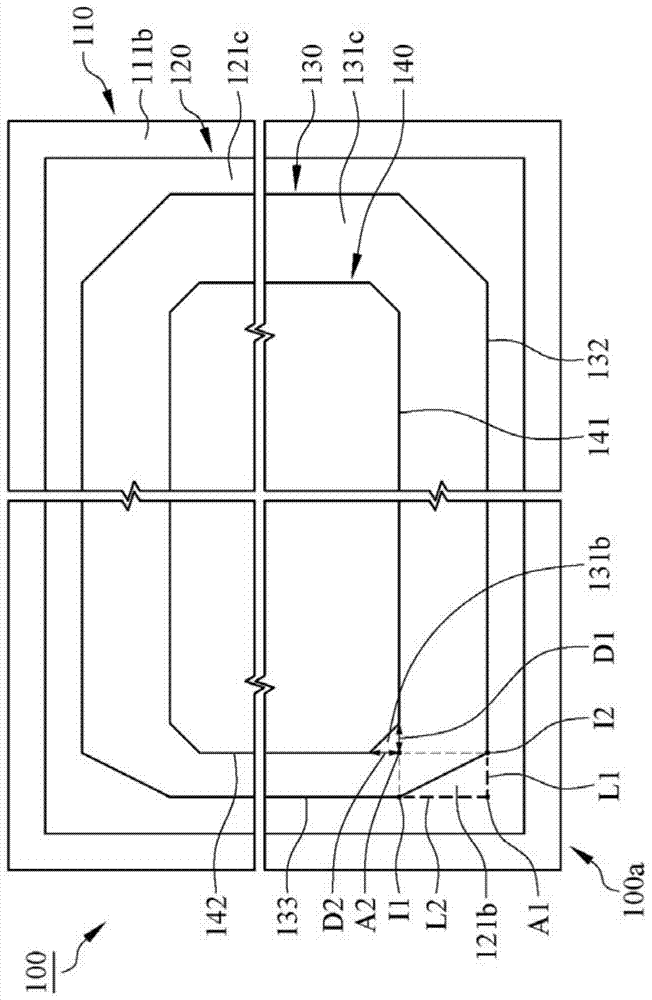

[0024] see figure 1 and figure 2 , which is a first preferred embodiment of the present invention, a semiconductor structure 100 has a corner 100a, the semiconductor structure 100 includes a carrier 110, a first protection layer 120, a second protection layer 130 and a third protection layer 140, The carrier 110 has a carrier surface 111, the carrier surface 111 has a protective layer setting area 111a and a protective layer exposed area 111b located outside the protective layer setting area 111a, the first protective layer 120 is set on the protective layer setting area 111a, the T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More