Network chip temperature optimization method applied to two-dimensional grid structure piece

A network chip and two-dimensional grid technology, applied in resource allocation, multi-programming devices, etc., can solve problems such as reducing chip operating performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

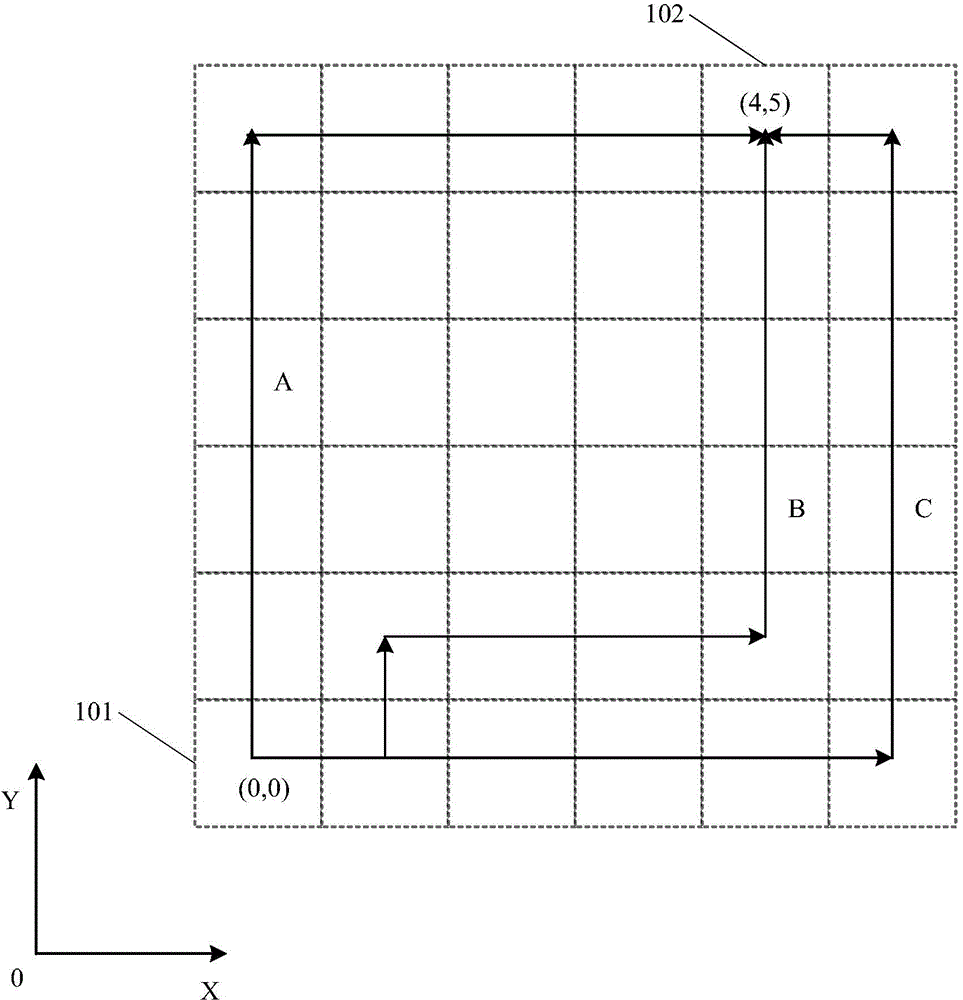

[0035] The present invention will be further described below in conjunction with the accompanying drawings. Such as figure 1 As shown, the two-dimensional grid structure network-on-chip chip is constructed by multiple cores in a grid structure. Each core is at a fixed physical location, and the communication tasks between the cores must be completed through the transfer between the cores, so each communication task will select a communication path to complete the communication. Such as figure 1 , assuming that the position of the kernel 101 is (x 101 ,y 101 ), the position of the kernel 102 is (x 102 ,y 102 ), the communication task from the core 101 to the core 102 can choose three paths A, B, and C for communication, the length of the communication path is the number of cores passed, if the length of the communication path is equal to (|y 101 -y 102 |)+(|x 101 -x 102 |), then this path is called the shortest path of the communication task. figure 1 Both path A and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More