Pattern optimized LED substrate with cone cluster type patterns and LED chip

A graphics-optimized substrate and cone cluster technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of limiting the promotion and application of LED chips on nano-scale graphics substrates, high manufacturing costs of nano-scale patterns, and reducing the life of LED chips, etc. problem, to achieve the effect of improving external quantum efficiency, reducing processing difficulty, and increasing reflection area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

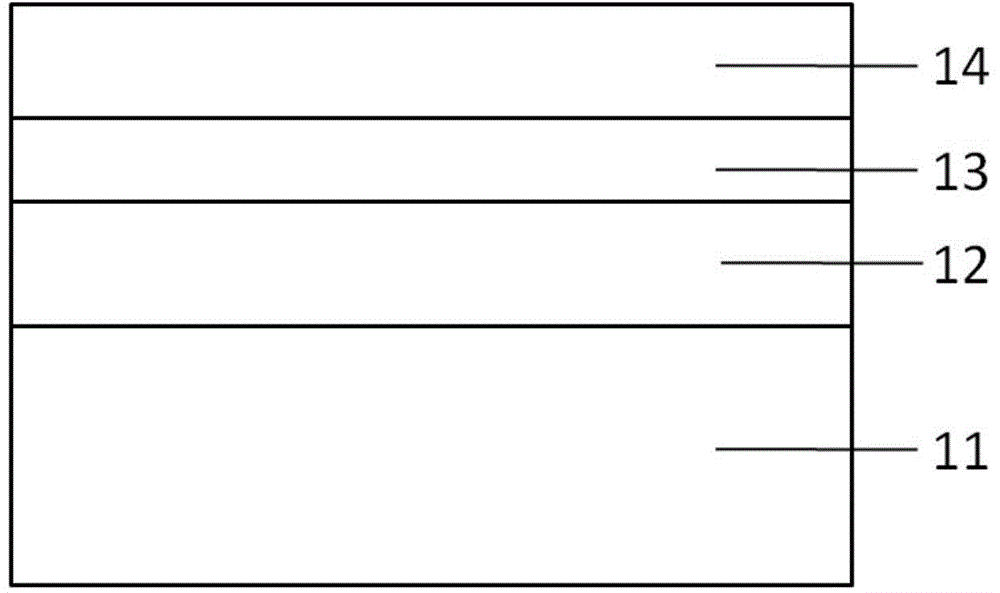

[0031] figure 1 It is a schematic diagram of the LED chip of this embodiment, which is composed of LED pattern optimized substrate 11, N-type GaN layer 12, MQWs quantum well layer 13, and P-type GaN layer 14 arranged in sequence.

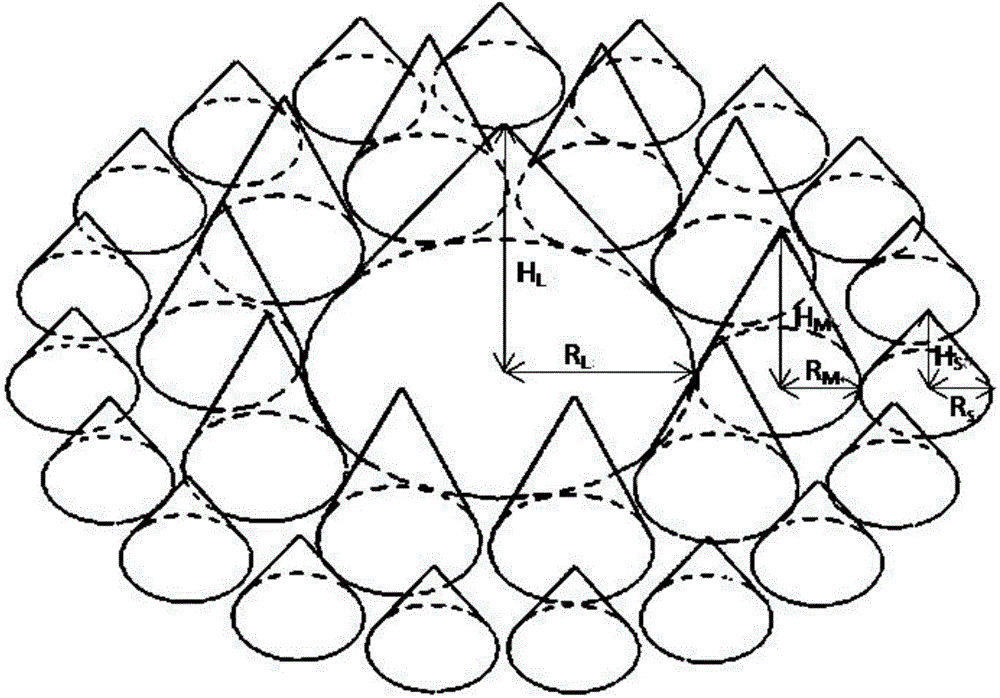

[0032] Such as figure 2 As shown, the pattern of the substrate in this embodiment consists of a plurality of conical clusters of the same shape arranged on the surface of the substrate in a rectangular arrangement. Such as image 3 As shown, each cone cluster is composed of a large cone, multiple medium cones and multiple small cones; the multiple medium cones are arranged in a circle around the large cone to form a medium cone circle; the multiple small cones surround the medium cone The circles are arranged in a circle to form small cone circles; the height H of each large cone L 2.0μm, bottom surface radius R L is 1.2μm; the height H of each middle cone M 1.25μm, bottom radius R M is 0.5μm; the height H of each small cone S 0.67μm, bottom...

Embodiment 2

[0034] The LED chip of this embodiment is composed of a conical cluster pattern LED pattern optimized substrate, an N-type GaN layer, an MQWs quantum well layer, and a P-type GaN layer arranged in sequence.

[0035] Such as Figure 4 As shown, the pattern of the substrate in this embodiment consists of a plurality of conical clusters of the same shape arranged on the surface of the substrate in a hexagonal arrangement. Each cone cluster is made up of a large cone, multiple medium cones and multiple small cones; the multiple medium cones are arranged in a circle around the large cone to form a medium cone circle; the multiple small cones are arranged in a circle around the medium cone circle circle, forming a small cone circle; the height H of each large cone L 1.0μm, bottom radius R L is 0.6μm; the height H of each middle cone M 0.75μm, bottom radius R M 0.25μm; the height H of each small cone S 0.3μm, bottom radius R S is 0.15 μm; the edge distance d of adjacent cone cl...

Embodiment 3

[0037] This embodiment is the same as Embodiment 1 except for the following features.

[0038] A plurality of cone clusters with the same shape in this embodiment adopt such as Figure 5 The rhombus arrangement shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More