EEPROM durability test method and EEPROM durability test device

A technology to be tested for durability test, applied in static memory, instruments, etc., can solve the problem of long time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

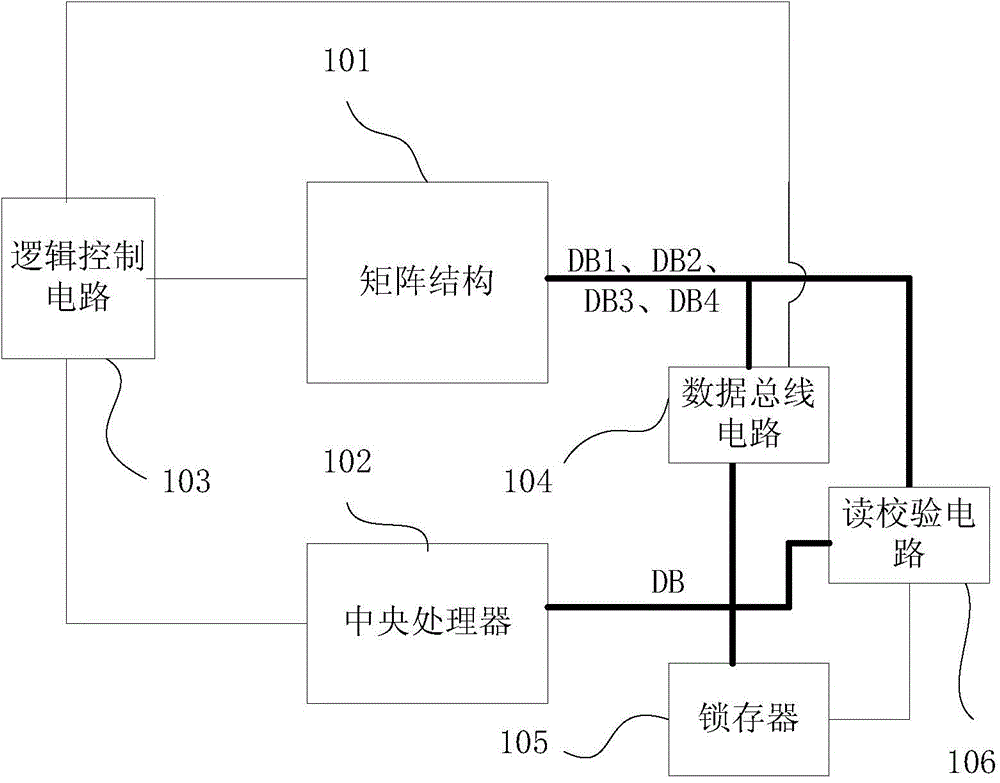

[0042] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

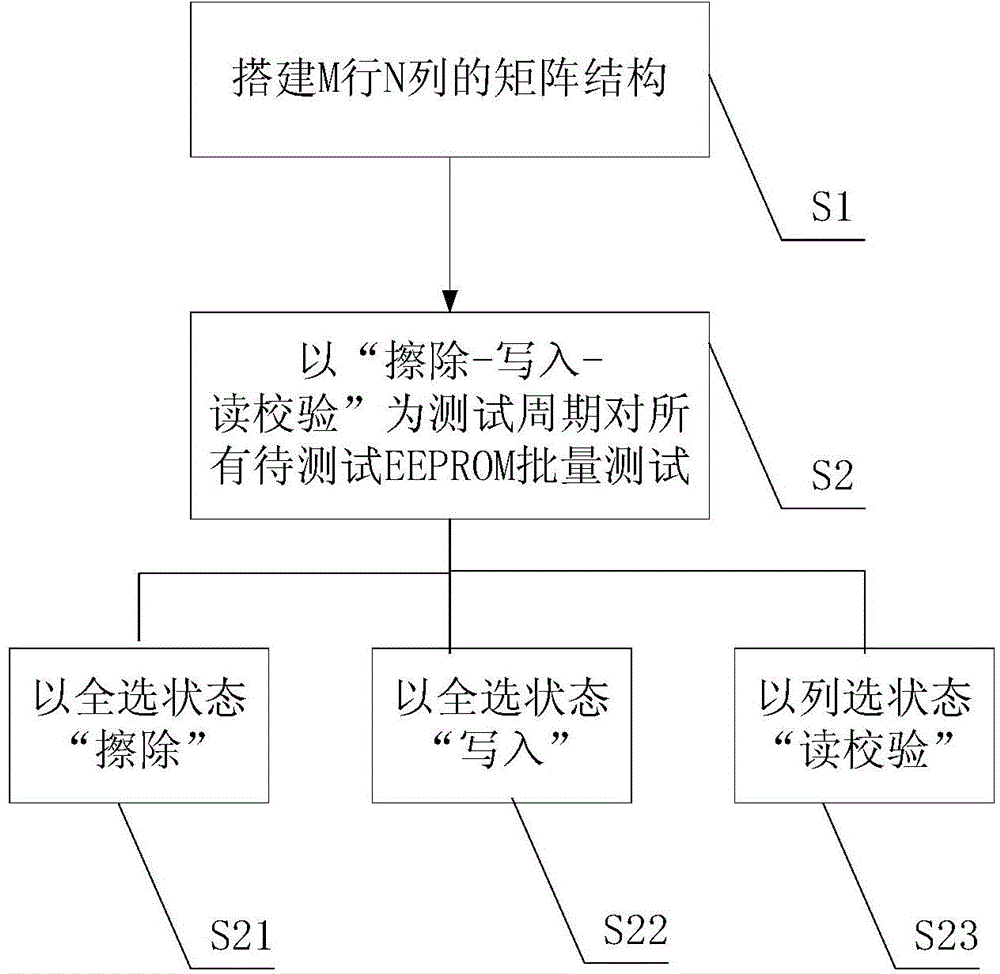

[0043] According to the solution of the present invention, aiming at the existing EEPROM durability test process "erase-blank check-write-read verification", the step of "blank check" is removed and parallel operation is introduced. see figure 1 , the EEPROM durability test method according to an embodiment of the present invention comprises the steps:

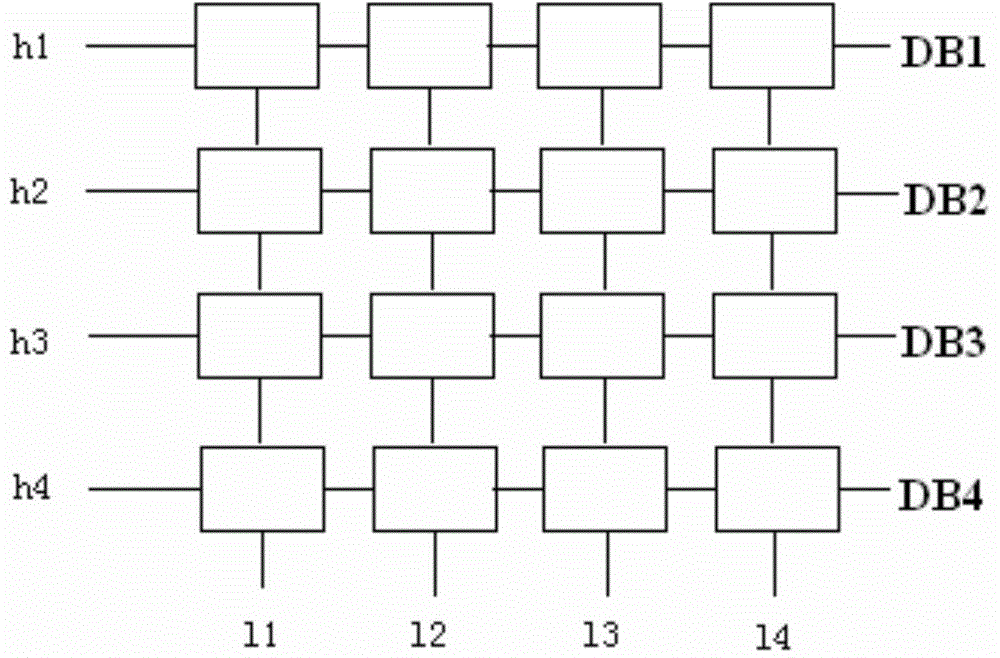

[0044] S1, build a matrix structure with M rows and N columns with M*N pipe positions. The pipe positions are used to insert the EEPROM to be tested. Each row of N pipe positions leads to a local data bus. M≥2 and is an integer, and N≥2 and It is an integer; the size of M and N is based on actual test needs, and the expansion is limited by the number of signals and the driving capability of the circuit. In this embodiment, both M and N are 4 (hereinafter both M and N=4 are taken as an example). In t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More