Dynamic release method and system of register file cache resources and processor

A register file and release system technology, applied in the field of processors, can solve problems affecting thread execution efficiency, waste of register file cache resources, and thread execution efficiency, and achieve the effects of high release and recovery efficiency and sensitive monitoring.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

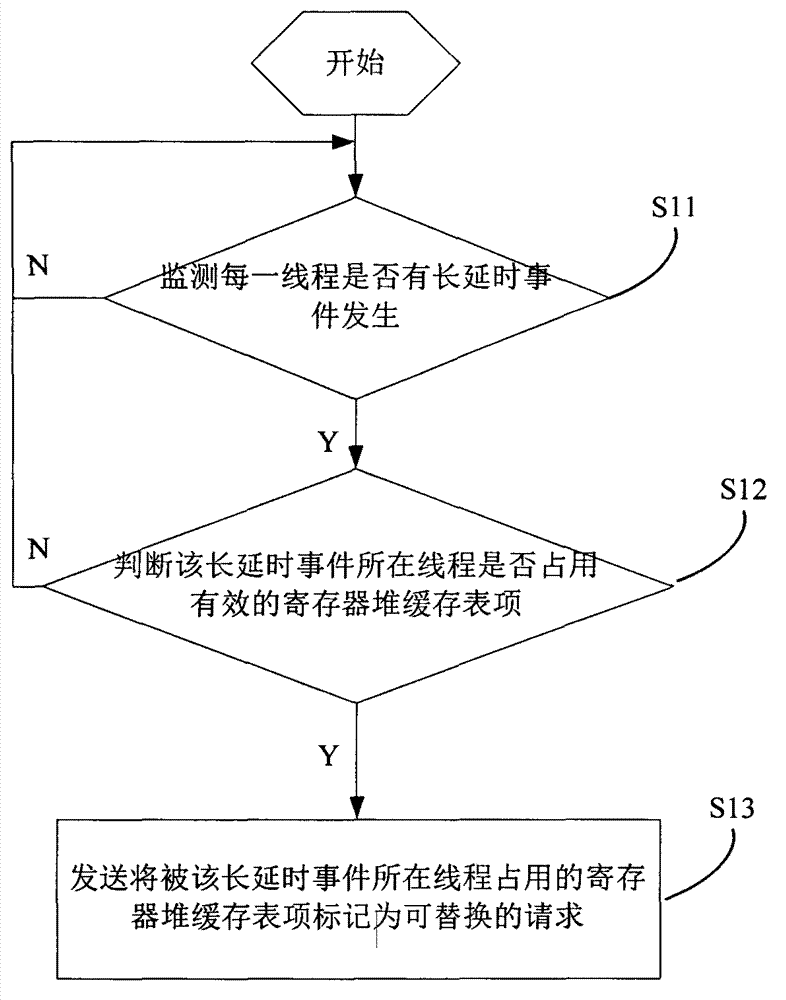

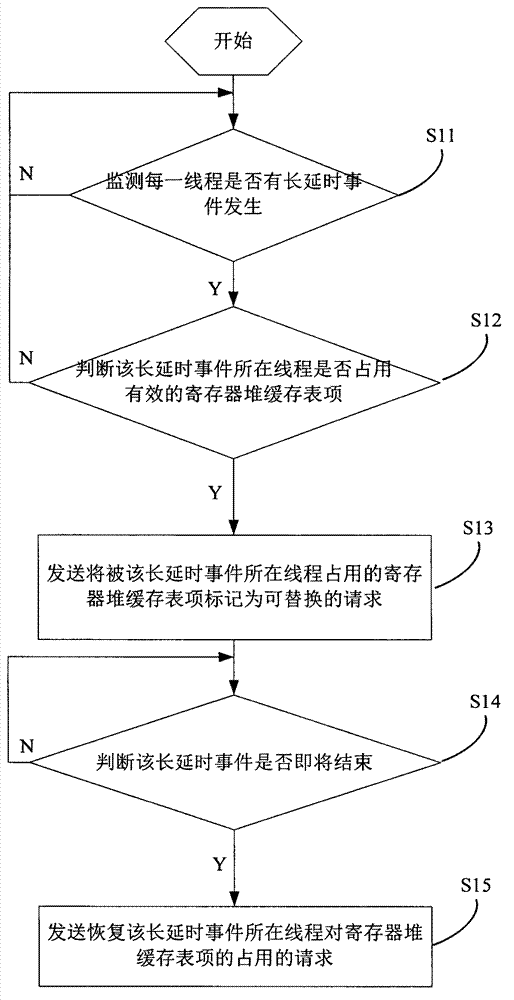

[0063] This embodiment provides a method for dynamically releasing register file cache resources, which is mainly used in multithreaded processors for operating register file caches, and sending requests to register file caches when register file cache resources need to be released. like figure 1 As shown, it specifically includes the following steps:

[0064] S11: Monitor whether a long-delay event occurs in each thread, if so, go to step S12, otherwise continue monitoring. Among them, a time threshold can be set to determine whether it is a long-delay event, and the event needs to be paused for more than the time threshold, and then it is identified as a long-delay event. It is also possible not to set a specific time threshold, but a long-delay event determined empirically during the processor design process, such as memory access miss, write operation cache read-after-write conflict (Store Buffer RAW), branch prediction error, among which Access misses such as TLB (Trans...

Embodiment 2

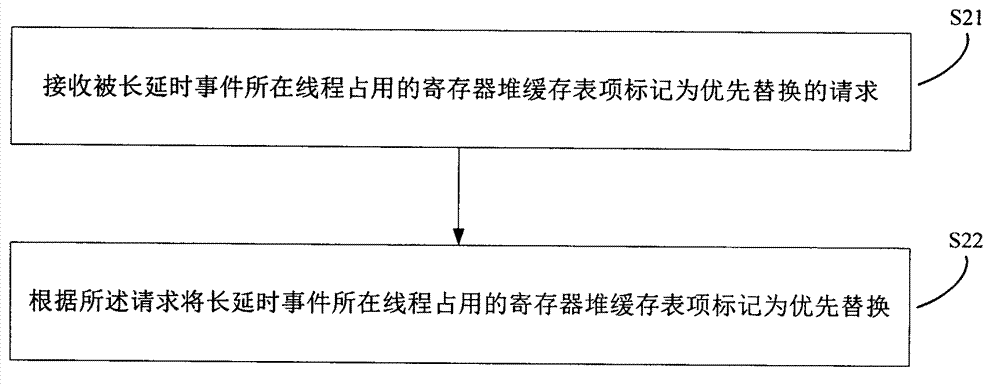

[0076] This embodiment provides a method for dynamically releasing register file cache resources, which is applied to the register file cache in a multi-threaded processor, and cooperates with the method in Embodiment 1, such as image 3 shown, including the following steps:

[0077] S21: Receive a request that the register file cache entry occupied by the thread where the long-delay event is located is marked as priority replacement.

[0078] S22: According to the request, mark the register file cache entry occupied by the thread where the long-delay event is located as priority replacement.

[0079] When other threads need to transfer their registers from the main register file into the register file cache, the entries marked as priority replacement in the register file cache are preferentially replaced.

[0080] Preferably, the following steps are also included before step S21:

[0081] S20: Set the index number and identification bit for the register file cache entry, wh...

Embodiment 3

[0089] This embodiment provides a dynamic release system 1 for register file cache resources, which is applied to multi-threaded processors and cooperates with register file cache 2, such as Figure 5 shown, including:

[0090] The monitoring unit 101 is configured to monitor whether a long-delay event occurs in each thread. A time threshold can be set to determine whether it is a long-delay event, and the event needs to be paused for more than the time threshold to determine it as a long-delay event. It is also possible not to set a specific time threshold, but a long-delay event determined empirically in the process of processor design, such as missing memory access, write operation cache read-after-write conflict (Store Buffer RAW), branch prediction error, Among them, access misses such as TLB (Translation Look-aside Buffer) misses, second-level cache misses, third-level cache misses, execution of barrier instructions such as Sync, Tlbi, etc., are all recognized long-dela...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com