Multi-master arbitration method in dynamic reconfigurable high-rate serial bus

A technology of high-speed serial bus and arbitration method, which is applied in the field of multi-master arbitration, can solve the problems of unsatisfactory UM-BUS bus real-time performance, reliability, poor bandwidth utilization rate, and large transmission delay, so as to reduce the waste of communication resources, The effect of improving reliability and speeding up rotation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

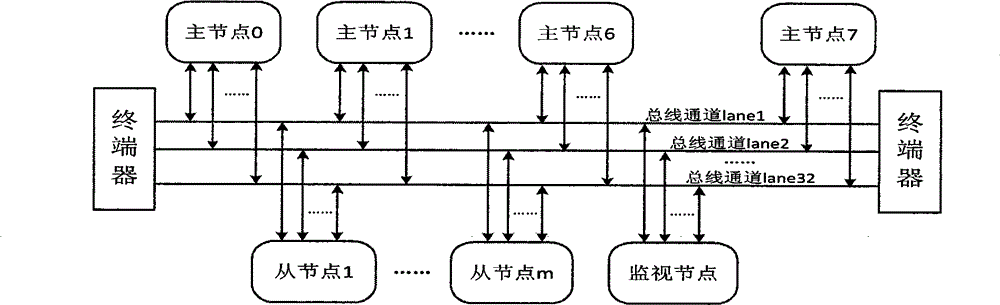

[0025] Based on the working principle of the above-mentioned UM-BUS bus, a kind of specific implementation of the multi-master arbitration method of the present invention is as follows:

[0026] For the convenience of description, it is assumed that the UM-BUS bus supports 8 master nodes, the node number is defined as 0~7, the bus single-channel communication rate is 200Mbps, the working clock of the bus MAC sublayer is 100MHz, and the maximum transmission time of bus signals between nodes is 260ns. An arbitration time slot timer and a time slice timer of the arbitration time slot counter are set in the UM-BUS bus node controller to generate the timing and counting of the required arbitration time slots. In order to ensure that in the worst case, each node of the bus can detect the occupancy of the bus by the master node within one arbitration time slot, the timing length of the arbitration time slot is set to 500 ns in this embodiment. The value range of the arbitration slot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More