FPGA (Field Programmable Gate Array) key data protection method for microsatellite

A key data and micro-satellite technology, which is applied in the fields of electrical digital data processing, generation of response errors, instruments, etc., can solve problems such as poor protection capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

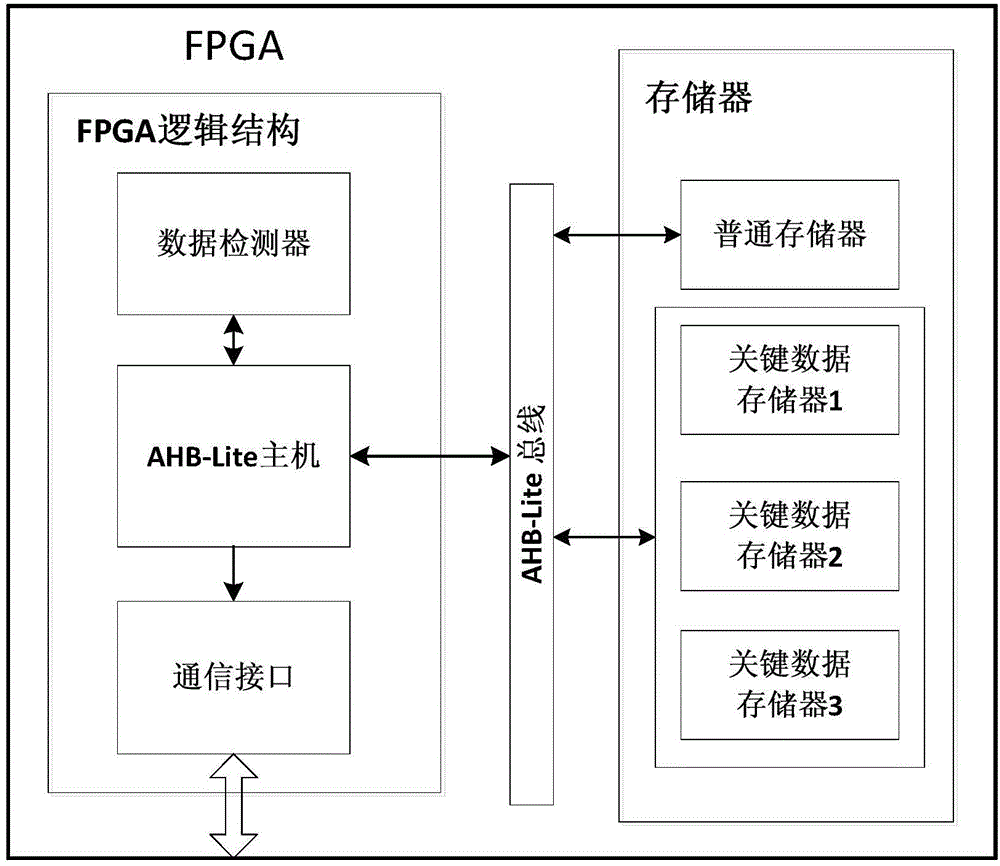

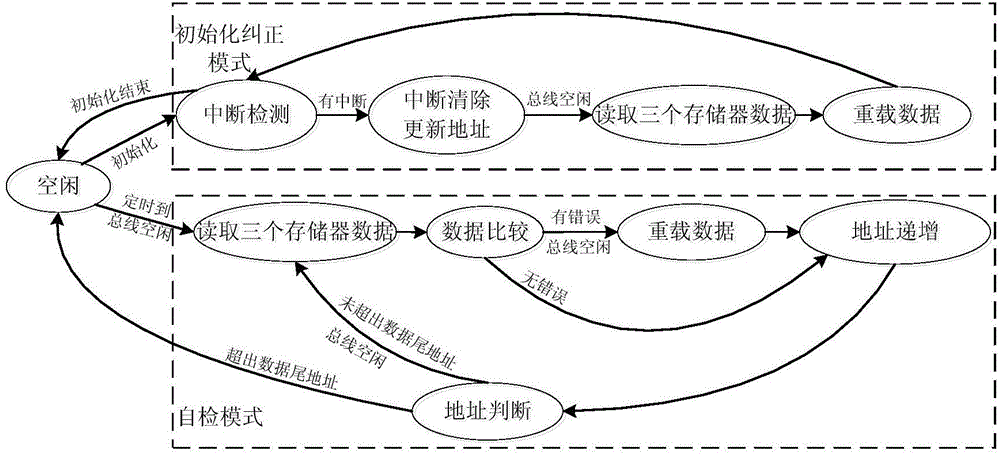

[0033] 3. Key data protection method: Key data protection is based on the first two implementation methods, and the FPGA internal logic of the AHB-Lite host and data detector is designed. The logic design of these two modules is the core content of FPGA key data protection. The specific implementation is as follows:

[0034] a) The AHB-Lite host provides the memory access interface to the data detector, generates and detects error correction codes, and generates multi-bit error interrupts.

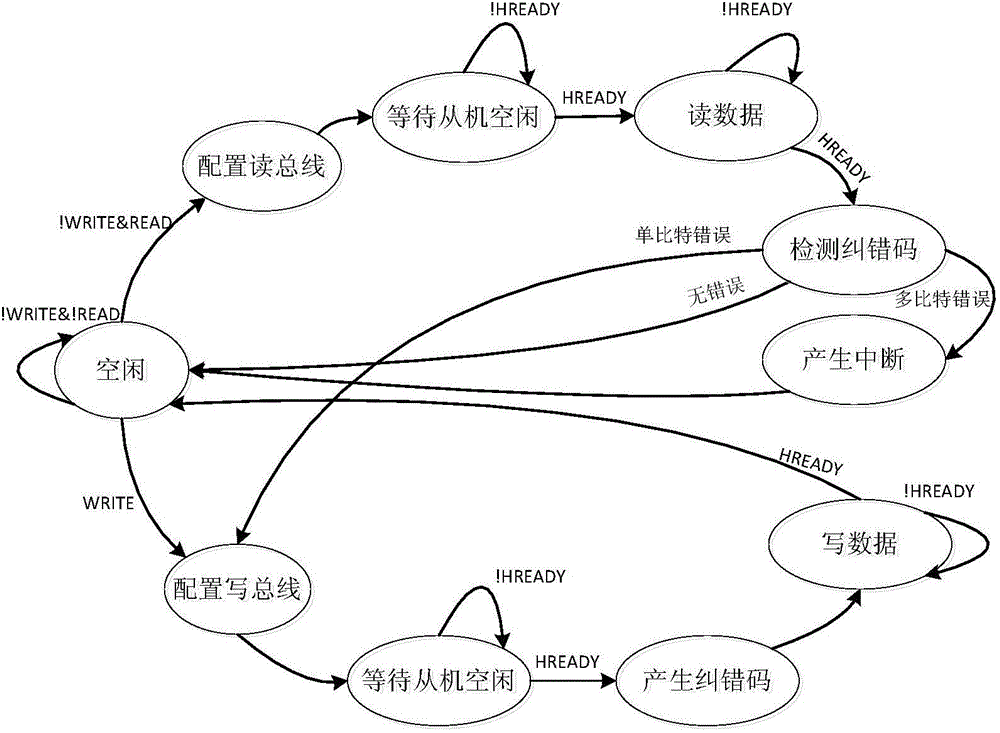

[0035] The design method of AHB-Lite mainframe adopts the finite state machine to realize. The logic design is designed according to the control timing of the AHB-Lite bus, and the address signal and control signal are driven on the rising edge of the bus clock to realize the read and write operations of the data by the AHB-Lite host. In order to avoid data read and write conflicts, the write priority is higher than the read priority. First, the state machine is in the "idle" state. Whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More