A memory testing device and a memory chip testing method

A technology for memory testing and memory chips, applied in static memory, instruments, etc., can solve the problems of ineffective recording of information, expensive AFM, low utilization of AFM hardware storage space, etc., and achieve the effect of improving utilization and test speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the purpose and features of the present invention more comprehensible, the specific embodiments of the present invention will be further described below with reference to the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

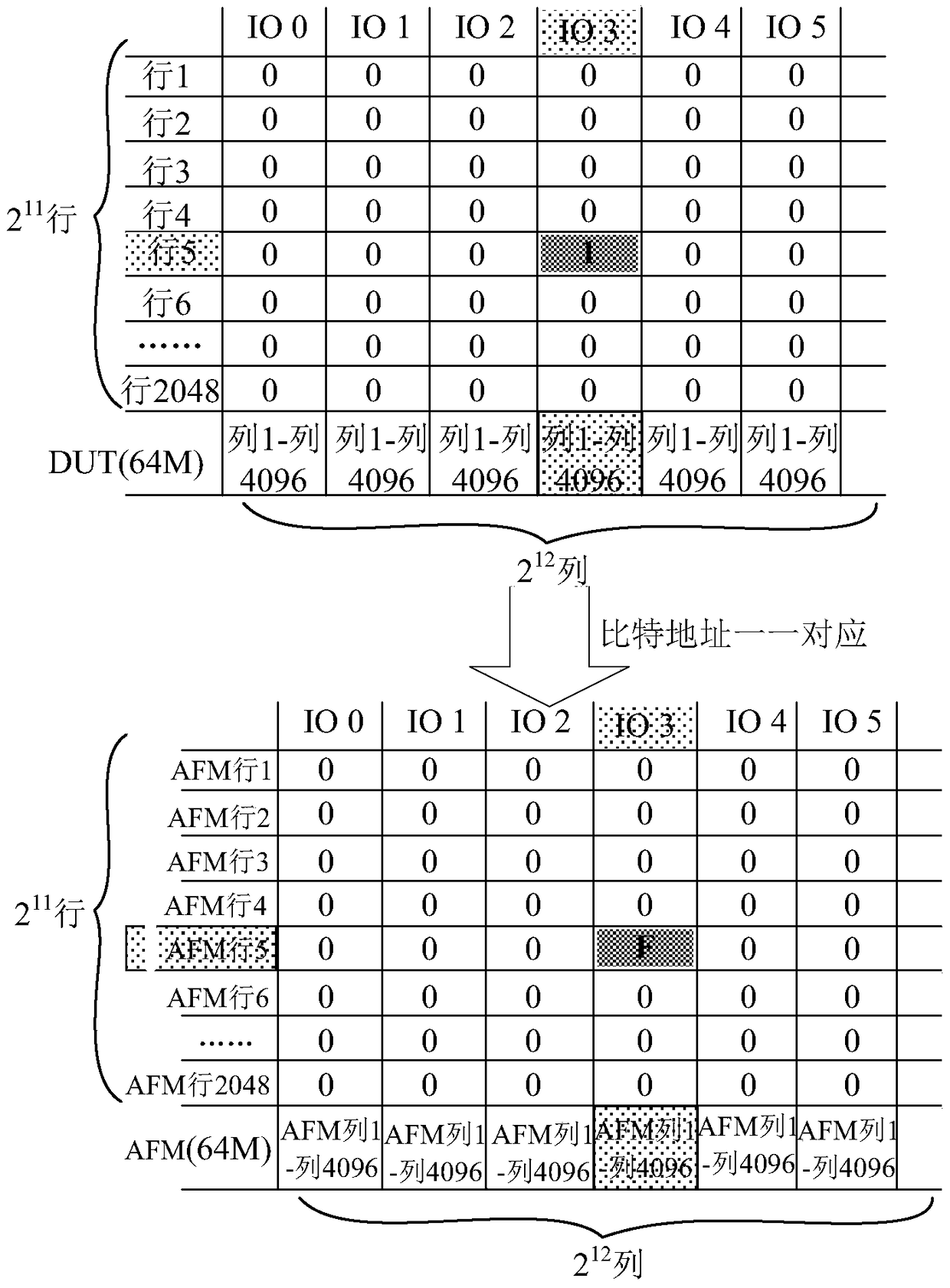

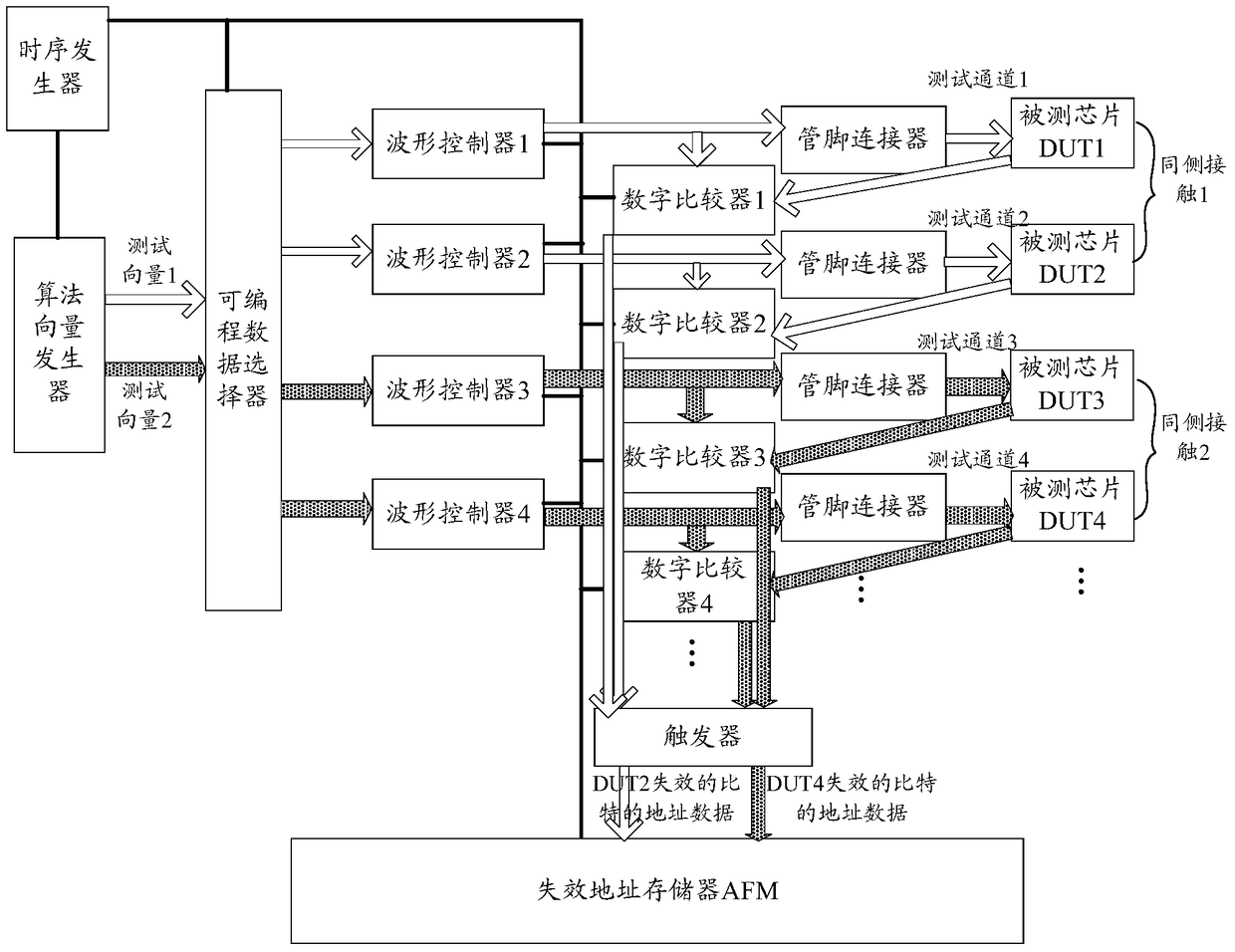

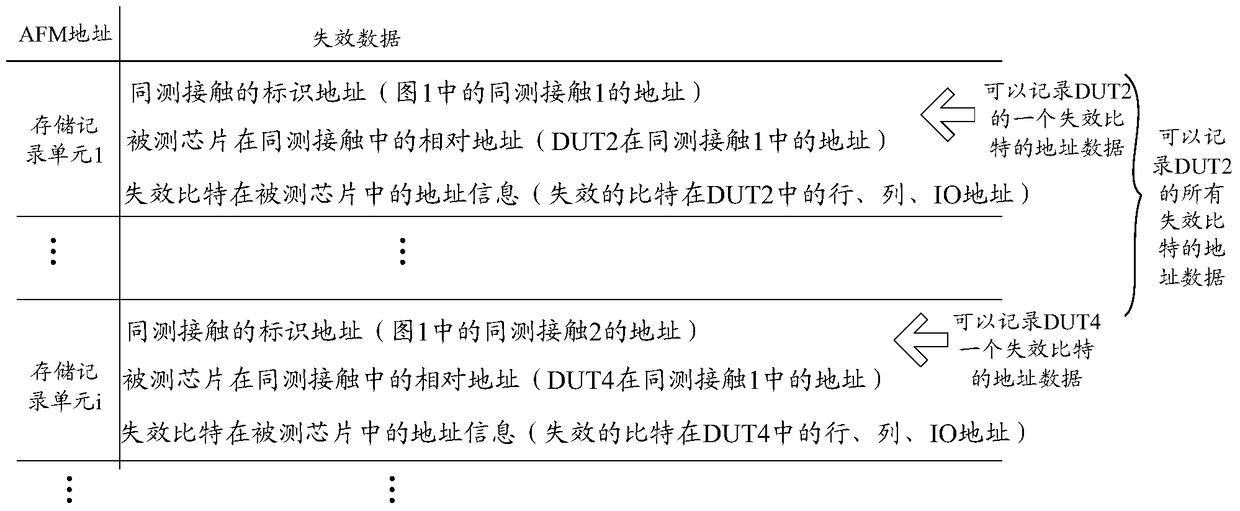

[0036] With the continuous advancement of semiconductor technology, those large memories that originally existed in wafers will be transformed into tens or hundreds of small memory arrays, and they will be scattered in every corner of the wafer. The technical scheme of the present invention is mainly aimed at improving the problems of low efficiency of collecting invalid address information and poor utilization of AFM hardware during the large-scale simultaneous testing of such large-scale memories (flash memory, SRAM, DRAM, etc.). Please refer to Figure 4 As shown, because there are often multiple memory chip units (Die) that need to be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More